# HEKATON: Horizontally-Scalable zkSNARKs via Proof Aggregation

Michael Rosenberg

Tushar Mopuri

Hossein Hafezi

micro@umd.edu

UMD

tmopuri@upenn.edu

UPenn

h.hafezi@nyu.edu **NYU**

Ian Miers

Pratyush Mishra

imiers@umd.edu

UMD

prat@upenn.edu

UPenn

July 26, 2024

#### Abstract

Zero-knowledge Succinct Non-interactive ARguments of Knowledge (zkSNARKs) allow a prover to convince a verifier of the correct execution of a large computation in private and easily-verifiable manner. These properties make zkSNARKs a powerful tool for adding accountability, scalability, and privacy to numerous systems such as blockchains and verifiable key directories. Unfortunately, existing zkSNARKs are unable to scale to large computations due to time and space complexity requirements for the prover algorithm. As a result, they cannot handle real-world instances of the aforementioned applications.

In this work, we introduce HEKATON, a zkSNARK that overcomes these barriers and can efficiently handle arbitrarily large computations. We construct HEKATON via a new "distribute-and-aggregate" framework that breaks up large computations into small chunks, proves these chunks in parallel in a distributed system, and then aggregates the resulting chunk proofs into a single succinct proof. Underlying this framework is a new technique for efficiently handling data that is shared between chunks that we believe could be of independent interest.

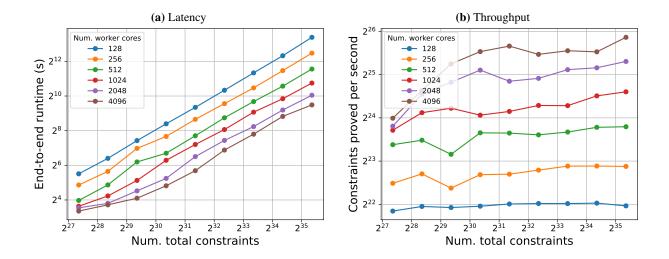

We implement a distributed prover for HEKATON, and evaluate its performance on a compute cluster. Our experiments show that HEKATON achieves strong horizontal scalability (proving time decreases linearly as we increase the number of nodes in the cluster), and is able to prove large computations quickly: it can prove computations of size 2<sup>35</sup> gates in under an hour, which is much faster than prior work.

Finally, we also apply HEKATON to two applications of real-world interest: proofs of batched insertion for a verifiable key directory and proving correctness of RAM computations. In both cases, HEKATON is able to scale to handle realistic workloads with better efficiency than prior work.

## **Contents**

| 1  | Introduction                                                 | 1          |

|----|--------------------------------------------------------------|------------|

|    | 1.1 Our contributions                                        | 1          |

|    | 1.2 Related work                                             | 3          |

| •  | Tachniques                                                   | 6          |

| 2  | Techniques                                                   |            |

|    | 2.1 Partition-friendly memory checking                       | 6<br>8     |

|    | 2.2 Aggregating heterogeneous commit-carrying zkSNARKs       |            |

|    | 2.3 Our aggregation scheme for Mirage                        | 8          |

|    | 2.4 Optimizations                                            | 10         |

| 3  | Preliminaries                                                | 11         |

| 3  |                                                              | 11         |

|    |                                                              |            |

|    |                                                              | 11<br>12   |

|    | 3.3 Aggregation schemes                                      | 12         |

| 4  | Partitioning circuits via memory checking                    | 14         |

| ٠. | • •                                                          | 14         |

|    |                                                              | 15         |

|    |                                                              | 15         |

|    | 4.5 Reducing partitioned Roll chedits to committable chedits | 13         |

| 5  | Aggregation scheme for Mirage                                | 20         |

|    | 88 8                                                         | 20         |

|    |                                                              | 22         |

|    |                                                              | 24         |

|    | 5.5 Construction                                             | <b>∠</b> ¬ |

| 6  | Divide-and-aggregate zkSNARKs                                | 26         |

| •  | 88 8                                                         | 26         |

|    |                                                              | 27         |

|    |                                                              | 27         |

|    | or opinizations                                              |            |

| 7  | Implementation                                               | 29         |

| _  |                                                              | •          |

| 8  |                                                              | 30         |

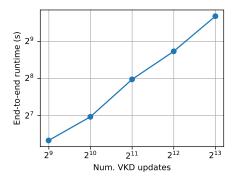

|    | r                                                            | 30         |

|    | C 1                                                          | 30         |

|    |                                                              | 33         |

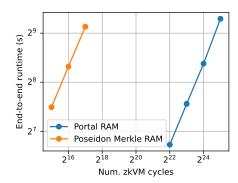

|    | 8.4 Application: verifiable RAM computation                  | 34         |

|    | L.,                                                          | 20         |

| Ac | knowledgements                                               | 36         |

| A  | Design choices and cluster architecture                      | 37         |

| B  | Additional definitions and lemmas                            | 37         |

| _  |                                                              | 38         |

|    | 2.1. 2010                                                    | 20         |

| C  | Proof of Theorem 6.1                                         | 39         |

| _  |                                                              | 39         |

|    | 1                                                            | 40         |

|    |                                                              | 43         |

|    |                                                              | 44         |

|    | C. Embleney                                                  |            |

| Re | ferences                                                     | 45         |

#### 1 Introduction

Zero-knowledge Succinct Non-interactive ARguments of Knowledge (zkSNARKs) are cryptographic proofs that allow a prover to convince a verifier that, given a function F and public input  $\mathbb{X}$ , there is a private witness  $\mathbb{X}$  such that  $F(\mathbb{X},\mathbb{X})=1$ . zkSNARKs hide all information about  $\mathbb{X}$ , and are *small* and *easy to verify* regardless of the complexity of F. Recent efficient constructions of zkSNARKs [GGPR13; Gro16; GWC19; CHMMVW20; Set20] have enabled a range of applications and industrial deployments that rely on zkSNARKs to improve efficiency and privacy characteristics. However, zkSNARKs cannot currently scale to prove useful computations on realistic problem sizes. Indeed, many proposed applications of zkSNARKs, such as verifiable key transparency [TFZBT22], proofs of program execution or vulnerability [BCGTV13; ZGKPP18], or machine learning inference [LXZ21], are limited to toy problem sizes due to zkSNARK scalability limitations.

In more detail, in typical zkSNARKs, to prove the correctness of a computation F on inputs (x, w), we must first express F as an arithmetic circuit  $C_F$ . The size of the latter is often much larger than the description of F, leading to two scalability issues:

- Poor parallelization: zkSNARK provers perform a number of expensive operations whose cost grows linearly with the circuit size  $|C_F|$ . Unfortunately, these operations have diminishing parallelizability, particularly for real implementations that must account for inter-process communication costs between cores, processors, and even compute clusters.

- Large memory overheads The space complexity of the prover also tends to scale linearly with  $|C_F|$ . As a result, memory often ends up being the key bottleneck for proving complex computations: while one can always wait longer for a proof, one cannot always add more RAM to the prover's machine.

These problems are not merely asymptotic, but lead to high concrete costs even for relatively simple computations. For instance, a circuit for proving the multiplication of two  $700 \times 700$  matrices requires 685 million gates. Prior work [WZCPS18] reports that using even a 64-threaded machine to prove this circuit requires hundreds of minutes and a prohibitive 1.7TB of RAM.

Moreover, these problems are exacerbated for many exciting SNARKs applications which, frequently, are RAM Programs (e.g., proofs of vulnerability, zkRollups, etc.). This poses two challenges. First, representing a RAM program as a bare circuit requires all branches be taken and loops be unrolled, drastically increasing circuit size. Second, circuits do not, natively, provide memory access and the methods for providing memory either offer high overhead or, as we will see, place constraints how we can address the space and time complexity.

**Distributed proving: a path forward?** A promising approach to scale zkSNARKs up to large circuits is to distribute the proving algorithm across a set of workers in a way that ensures that the proof computation is parallelized across the workers, and which ensures that each worker's local memory requirements are low. In this work, we revisit this approach and design HEKATON, a new *horizontally-scalable* zkSNARK whose prover algorithm can be distributed over large compute clusters much more efficiently than all prior work [WZCPS18; Xie+22; LXZSZ24]. We detail the technical contributions underlying HEKATON next.

#### 1.1 Our contributions

HEKATON is the result of several contributions:

(1) Scalable proving via divide-and-aggregate. We distill a generic framework for constructing scalable zkSNARKs that we call *divide-and-aggregate*, or DNA for short. Our framework proceeds as follows:

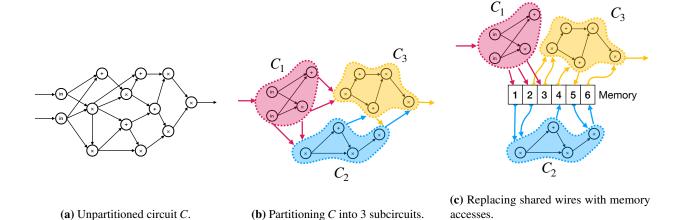

Figure 1: Partitioning circuits for use with our divide-and-aggregate zkSNARK.

to prove the execution of a function F represented as a circuit  $C_F$ , partition  $C_F$  into smaller *subcircuits*  $C_1, \ldots, C_n$ , and have each cluster machine use a simpler "inner" zkSNARK to prove the satisfaction of an individual subcircuit separately. Then, invoke a *proof aggregation* protocol [BMMTV21; GMN22; ABST23] to relatively cheaply aggregate these subcircuit proofs into a single succinctly-verifiable proof.

Instantiating the foregoing blueprint requires addressing two challenges: aggregating proofs for different subcircuits, and sharing wires between subcircuits.

- (2) Multi-circuit aggregation. We generalize prior proof aggregation schemes [BMMTV21; GMN22] to efficiently aggregate proofs for *different* circuits. This allows our framework to handle computations with *arbitrary* subcircuit structure. In contrast, schemes implicit in prior work [BMMTV21] are only able to handle *uniform* circuits that just repeat the same subcircuit many times.

- (3) Shared wires via efficient global memory. All known aggregation schemes (including ours) are only able to achieve succinct verification when proofs for neighbouring subcircuits share a small constant amount of data. However, this is incompatible with our goal of designing a proof system for *arbitrary* circuits where subcircuits might share many wires.

We overcome this challenge via a new low-overhead technique for providing subcircuits with efficient access to a *global memory bank*. This allows subcircuits to share wire values by accessing them from the memory bank, rather than directly passing them between subcircuits. To efficiently prove correctness of memory accesses, we design a new memory-checking circuit that can itself be partitioned into subcircuits that share just a constant number of wires. The resulting workflow is illustrated in Fig. 1.

On a technical level, our approach extends recent work on permutation-based memory checking techniques [ZGKPP18; BCGJM18] that uses commit-carrying SNARKs by extending our aggregation scheme into one that supports a commit-carrying mode.

(4) Efficient instantiation and implementation. We instantiate our DNA zkSNARK blueprint by choosing Mirage [KPPS20] as the inner zkSNARK, and designing a new "commit-carrying" aggregation scheme for Mirage. We call the resulting system HEKATON.

We implement HEKATON in a Rust library that supports distributed proving. Our implementation also provides a novel framework for writing partitioned circuits that enables us to minimize communication (in distributed mode) and memory requirements (in both modes). We provide details in Section 7.

(5) Applications and evaluation. As noted above, our evaluation of HEKATON demonstrates that it can prove computations that are orders-of-magnitude larger than prior work, while requiring a fraction of the time. We provide details in Section 8. To showcase the improvements HEKATON offers over state of the art provers, we implement two real world applications. In the first application, we use HEKATON to prove the correctness of batched updates to a Verifiable Key Directory [TFZBT22], whose configuration, for the first time, matches that of deployed systems, i.e., using a sparse Merkle Tree and SHA256 as a hash function. In the second application, we adapt our memory-checking techniques to build a proof for RAM execution that achieves a throughput of 50 kHz. Our system is able to prove a large execution trace of 2<sup>25</sup> instructions via a circuit of 2<sup>35</sup> constraints.

#### 1.2 Related work

**Lookup tables.** Our global memory technique is reminiscent of recent work on lookup arguments [GW20; ZBKMNS22]. Indeed, one could consider constructing a large lookup table containing the shared wire values. However, a key difference is that most lookup arguments assume that the commitment to the table is constructed honestly in an offline phase (often over public values), and hence optimize their proving algorithm for this regime. In our setting, the "table" is for secret wire values unique to the witness and therefore must be constructed online during the proving phase by the untrusted prover. To use a lookup argument, we would first need to check that the table commitment was generated honestly, and would need to design a proving algorithm optimized for this regime.

**Partitioning circuits.** Assuming sufficient resources, HEKATON's latency is determined by the size of the largest of the partitioned subcircuit and the number of shared wires between the subcircuits. The latter costs only 13 constraints per shared wire, thus partitioning the circuit into equal-sized subcircuits leads to good performance since in practice, these partitioned circuits have a very small number of shared wires. We leave the problem of optimal circuit partitioning to future work, but note that HEKATON is compatible with prior automatic circuit partitioning schemes [Cos+15; San+23].

#### 1.2.1 Distributed zkSNARKs

Like HEKATON, all prior works on distributed zkSNARKs use a coordinator which gets as input the circuit C, the public input x, and the witness w, and is responsible for distributing these to the worker nodes, who in turn jointly compute the zkSNARK proof. Existing protocols differ in how these workers perform the latter computation. We provide an asymptotic comparison between the above systems in Table 1, and focus below on qualitative differences.

| system            | supported computation | proof<br>size | per-worker<br>time | total comm. | verifier<br>time | SRS size     |

|-------------------|-----------------------|---------------|--------------------|-------------|------------------|--------------|

| DIZK [WZCPS18]    | arbitrary             | O(1)          | $	ilde{O}( C /n)$  | O( C )      | O(1)             | O( C )       |

| DeVirgo [Xie+22]  | data-parallel         | O(n)          | $	ilde{O}( C /n)$  | O( C )      | $O(\log n)$      | $O(\lambda)$ |

| Pianist [LXZSZ24] | arbitrary             | O(1)          | $	ilde{O}( B )$    | O(1)        | O(1)             | O( C )       |

| HEKATON           | arbitrary             | $O(\log n)$   | $	ilde{O}( B )$    | O(1)        | $O(\log n)$      | O(n+k B )    |

**Table 1:** Comparison of distributed zkSNARKs. Here C is the circuit being proved, n is the number of subcircuits, k is the number of *unique* subcircuits, and B is the largest unique subcircuit.

**DIZK** [WZCPS18] initiated the study of distributed algorithms for zkSNARK provers, focusing on the zkSNARK in [Gro16] (though the techniques are applicable to other proof systems as well). In more detail,

the core contributions of DIZK are the design and implementation of efficient distributed algorithms for the core operations performed in zkSNARK provers, namely FFTs and multi-scalar multiplications. The primary drawback of DIZK is its need for a *linear* amount of inter-worker communication. In practice, this greatly increases the latency of proving: the per-gate cost is  $10 \times$  worse than local proving. In contrast, HEKATON requires only *constant* inter-worker communication, and is able to achieve per-gate costs that are very similar to local proving.

**DeVirgo** [Xie+22] is a SNARK with a distributed prover that focuses on supporting only *data-parallel* computations, i.e., the circuit being proved consists of repeated copies of a single subcircuit. DeVirgo's prover requires the primary node to perform cryptographic work that scales with the size of the subcircuit, and requires linear inter-worker communication. In contrast, as noted above, HEKATON supports arbitrary computations, requires only constant inter-worker communication, and ensures that the cryptographic work performed by the primary node scales only with the number of workers.

**Pianist** [LXZSZ24] is a very recent work that designs a distributed proving algorithm for the Plonk zk-SNARK [GWC19]. At a high level, Pianist relies on the elegant observation that using *bivariate* polynomial commitments allows one to decompose Plonk's global permutation check, which is used for circuit wiring correctness, into local per-worker permutation checks. The resulting protocol, produces constant proof size and verifier time, whereas the latter costs scale logarithmically for HEKATON.<sup>1</sup>

However, Pianist, as instantiated, requires an SRS whose size scales linearly with circuit size. To be precise, the SRS for the bivariate polynomial commitment in Pianist depends on the degree of the variables. The degree of the first variable corresponds to subcircuit size, and that of the other to the number of workers. As a result, Pianist's SRS size is O(|C|). In contrast, because HEKATON'S SRS consists of the SRS(es) for subcircuits and a small SRS for aggregation, its SRS size is dominated by the number of unique subcircuits. For many circuits of interest (e.g., RAM programs), the number and size of the unique subcircuits is much smaller than the total circuit size, leading to substantial SRS size savings for HEKATON. We provide a thorough experimental comparison of HEKATON and Pianist in Section 8.2.

Mangrove [NDCTB24] is a concurrent theoretical work that uses similar commit-and-prove-based permutation-checking techniques as us. Unlike us, however, Mangrove only reports estimated performance numbers, and does not provide a full implementation or evaluation. Furthermore, applying Mangrove's techniques to distributed proving would lead to a prover that requires linear inter-worker communication.

**Distributed proving based via recursive proofs.** A promising idea for distributed proving is to use recursive verification, where the system uses recursive proofs to aggregate subcircuit proofs. The idea would be to replace the custom aggregation scheme in HEKATON with a system that verifies batches of subcircuit proofs recursively in a tree-like manner. However, this approach has several drawbacks.

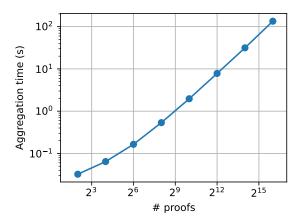

First, even assuming state-of-the-art folding-based techniques [BCLMS21; KST22] that have reduced the cost of recursive verification, a back-of-the-envelope calculation shows that such an approach would have over 2×-worse aggregation time than HEKATON. This is even when we assume that the aggregation step is *also* distributed; without this assumption, the recursive verification approach would have much worse aggregation time.

Second, even a state-of-the-art recursive aggregation scheme, would still need to support shared wires between subcircuits, and as discussed in Section 2.1.1, existing approaches for this would incur much higher overhead than HEKATON. Adapting the memory-checking techniques in HEKATON to a recursive verification setting is a non-trivial research problem, and indeed formed a key component of concurrent work [NDCTB24].

<sup>&</sup>lt;sup>1</sup>Note that one can generically reduce HEKATON's proof sizes via depth-1 recursive proof composition [Cos+15; BCGMMW20].

Finally, scalable implementation of these approaches would be challenging due to the need for complex multi-round communication and straggler management.

## 2 Techniques

We construct our divide-and-aggregate zkSNARK via the blueprint outlined in Section 1.1, which we recall next. To prove a circuit C, (a) partition C into subcircuits  $(C_1, \ldots, C_n)$ , (b) replace shared wires with accesses to a global memory, (c) construct augmented subcircuits  $(C'_1, \ldots, C'_n)$  that additionally check memory accesses, (d) prove each  $C'_i$  using via an inner zkSNARK (denoted ARG), and (e) aggregate the resulting proofs using an aggregation scheme for ARG proofs (denoted Agg).

In the rest of this section, we will expand on each of these steps, focusing on our novel memory checker (Section 2.1) and our new commit-carrying aggregation scheme (Section 2.2) that supports this memory checker.

### 2.1 Partition-friendly memory checking

To check the consistency of these memory accesses, one can design a "memory-checker" circuit M using standard memory checking techniques [BEGKN91]. However, integrating this into our blueprint requires that the memory checker M can be partitioned into n subcircuits  $M_1, \ldots, M_n$ , such that (a)  $M_i$  checks the memory accesses made by  $C_i$ , and (b)  $M_i$  and  $M_{i+1}$  share just a constant number of wires. Given such an M, we can obtain a DNA zkSNARK for arbitrary circuits by invoking our blueprint on *augmented* subcircuits  $C_i'$  that invoke  $C_i$  and  $M_i$  together. Let us thus focus on constructing such a partitioning-friendly memory checker.

#### 2.1.1 Limitations of existing memory checkers

**Attempt 1: Online memory checkers.** In *online memory checking* [BEGKN91], memory is committed to via a Merkle tree and read/write operations consist of checking/updating the Merkle path for that location. This requires sharing only a single wire value (the Merkle root) between subcircuits, and is used in all prior divide-and-aggregate SNARKs [BCTV14a; CTV15]. However, online memory checking creates both asymptotic and concrete bottlenecks.

Asymptotically, Merkle path checking imposes a logarithmic overhead: if  $s_i$  is the number of shared wires in the i-th subcircuit  $C_i$ , then checking  $C_i$ 's memory accesses requires  $s_i \cdot O(\log s)$  hash function invocations, where  $s = \sum_i s_i$  is the size of the global memory. Since in the worst case the number of shared wires can be as large as the circuit size  $|C_i|$ , the size of the memory checker subcircuit  $M_i$ , and hence that of the augmented subcircuit  $C_i'$ , can be as large as  $O(|C_i|\log|C_i|)$ . Concretely, even with zkSNARK-friendly [AABDS20; GKRRS21] hash functions that require  $\sim 300$  gates, each memory access costs  $300 \log |s|$  gates, which results in unacceptable slowdowns in practice.

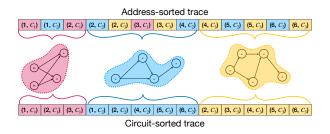

Attempt 2: Memory trace checkers. A second approach [BCGT13] verifies memory operations by recording them in a *memory trace*, and performing cheap checks on the trace entries. In more detail, a memory trace logs each memory operation as (subcircuit-number, op = read/write, addr, value). The checker then considers two versions of this trace: one sorted by address (denoted A), and another sorted by subcircuit number (denoted T), and performs both local and global checks on these traces. As we will show later, the local checks are easily partitioned across subcircuits, but the global check requires verifying that the two traces contain the same entries, and are hence permutations of each other. Efficiently implementing this "permutation check" in a manner amenable to partitioning is a challenge, as we explain next.

**Permutation checking.** State-of-the-art permutation checking techniques [ZGKPP18; BCGJM18; KPPS20] require the optimal O(s) gates to check permutations between s-sized traces. They achieve this low cost by relying on randomized Reed-Solomon fingerprinting [Lip89; Lip90], which performs the following randomized check to ensure that two traces  $T := (t_1, ..., t_s)$  and  $A := (a_1, ..., a_s)$  are permutations:

- 1. construct trace polynomials  $T(X) := \prod_{i=1}^{s} (X t_i)$  and  $A(X) := \prod_{i=1}^{s} (X a_i)$ ;

- 2. sample a random field element  $r \leftarrow \mathbb{F}$ ; and

- 3. check that T(r) = A(r).

This check can be realized quite efficiently via a circuit that witnesses T, A, and r, computes the products  $\prod_{i=1}^{s} (r-t_i)$  and  $\prod_{i=1}^{s} (r-a_i)$ , and checks that these are equal. We now show that this computation can also be partitioned easily across subcircuits in a way that ensures that each subcircuit only pays for the accesses it makes to the memory.

#### 2.1.2 Partitioning polynomial evaluation

Our partitioning strategy relies on the simple but crucial observation that **the trace polynomials can be evaluated incrementally**. In more detail, notice that for every  $j \in [s]$ , if we are given the running products  $\tau := \prod_{i=1}^{j} (r-t_i)$  and  $\alpha := \prod_{i=1}^{j} (r-a_i)$ , and the j+1-th trace entries  $t_{j+1}$  and  $a_{j+1}$ , we can easily compute the next running products  $\tau' := \tau \cdot (r-t_{j+1})$  and  $\alpha' := \alpha \cdot (r-a_{j+1})$ . We can then iterate this process to eventually compute T(r) and A(r). We leverage this observation to construct memory-checking subcircuits  $M_1, \ldots, M_n$  as follows.

**Notation.** Denote by  $s_i$  the number of memory accesses in the *i*-th subcircuit  $C_i$ , by  $k_i = \sum_{j=1}^{i-1} s_j$  the total number of accesses in the previous subcircuits  $C_1, \ldots, C_{i-1}$ , and finally by  $S_i$  the set  $\{k_i + 1, \ldots, k_i + s_i\}$ .

Let  $T = (t_1, ..., t_s)$  and  $A = (a_1, ..., a_s)$  be the memory traces as defined in Section 2.1.1. We split these traces up into n subtraces, one for each subcircuit, as follows. The i-th subtrace of T is defined to contain those entries access by  $C_i$ , i.e.,  $T_i := \{t_j \mid j \in S_i\}$ . The i-th subtrace of A is defined analogously as  $A_i := \{a_j \mid j \in S_i\}$ . Finally, denote by  $\tau_i$  and  $\alpha_i$  the running products up to (but excluding) the i-th subcircuit, i.e.,  $\tau_i := \prod_{j \in [k_i]} (r - t_j)$  and  $\alpha_i := \prod_{j \in [k_i]} (r - a_j)$ .

Construction. We are now ready to describe how our construction of the memory-checking subcircuits  $M_i$ .

- $M_i$  receives as **public input** the random challenge r, the last entries t and a of  $T_{i-1}$  and  $A_{i-1}$  respectively, as well as the running products  $\tau_i$  and  $\alpha_i$ .

- The **public output** of  $M'_i$  consists of the last entries t' and a' of  $T_i$  and  $A_i$  respectively, as well as the updated running evaluations  $\tau_{i+1}$  and  $\alpha_{i+1}$ .

- $M_i$  receives as additional witness the subtraces  $T_i$  and  $A_i$ .

- $M_i$  performs the following computations:

- $M_i$  replaces each memory gate with with a 'read' from the value in the corresponding entry in  $T_i$ .

- $M_i$  checks that entries in  $T_i$  all have the subcircuit number set to i, and that  $A_i$  is sorted by address.

- $M_i$  checks that consecutive entries in  $A_i$  are consistent: if they have the same address, then they must contain the same value.

- $M_i$  computes the new running products  $\tau_{i+1} := \tau_i \cdot \prod_{j \in \mathcal{S}_i} (r t_j)$  and  $\alpha_{i+1} := \alpha_i \cdot \prod_{j \in \mathcal{S}_i} (r a_j)$

This approach, illustrated in Fig. 2, achieves the desired performance: the *i*-th memory-checking circuit processes exactly an  $s_i/s$ -fraction of the traces in just  $O(s_i)$  gates, as required, and the hidden constants are great: just 13 gates per shared wire. We provide formal details and analyses of this construction in Section 4.2.

We note that our full construction in Section 4.2 incorporates the optimizations mentioned in Section 2.4 to further simplify and reduce the cost of memory-checking.

<sup>&</sup>lt;sup>2</sup>Note that  $A_i$  can be entirely disjoint from  $T_i$ , i.e., it might contain no entries corresponding to  $C_i$ 's memory accesses.

Figure 2: Memory traces are partitioned across subcircuits.

#### 2.2 Aggregating heterogeneous commit-carrying zkSNARKs

A question left open by the description of the memory-checker construction in Section 2.1 is that of how to derive the challenge r for the trace polynomial evaluation. An approach taken by prior work [ZGKPP18; KPPS20] is to derive the random challenge r by hashing (via a random oracle  $\rho$ ) *commitments* to the traces. This requires the SNARK proof for each subcircuit to additionally ensure that the witnessed traces are consistent with their claimed commitments. Prior work achieves this consistency check efficiently by using special *commit-carrying zkSNARKs* (cc-zkSNARK) [CFQ19] where the commitment scheme is co-designed with the SNARK so that the contents of the commitment are "natively" available as witnesses in the proven circuit.

We briefly recall their high-level strategy here, and then explain why it does not work in our setting. First, the prover commits to the traces, obtaining commitments tcm and acm; then, it derives the challenge  $r := \rho(\text{tcm}, \text{acm})$ ; and finally, it invokes the zkSNARK's proving algorithm on the augmented subcircuits  $C_i'$  to prove that the committed traces are valid memory traces. Unfortunately, the natural extension to our setting where the prover derives the challenge r by hashing the individual subcircuit commitments fails to meet our goals because the proof is no longer succinct.

Our approach: commit-carrying aggregation schemes. We resolve this issue by defining a new notion of *commit-carrying aggregation schemes* that support aggregating not only the proofs the underlying inner cc-zkSNARK, but also their commitments. Our notion also naturally supports *multi-circuit* aggregation that allows the prover to aggregate proofs for multiple circuits into a single combined proof.

With this new tool in hand, we can augment our blueprint construction as follows. Given an inner cc-zkSNARK ARG and a commit-carrying aggregation scheme Agg for ARG, to prove a partitioned circuit  $C = (C_1, ..., C_n)$ ,

- 1. construct augmented subcircuits  $(C'_1, \ldots, C'_n)$  and memory subtraces  $(T_1, \ldots, T_n)$  and  $(A_1, \ldots, A_n)$ ;

- 2. compute trace commitments  $(tcm_1,...,tcm_n)$  and  $(acm_1,...,acm_n)$  using ARG's commitment scheme;

- 3. aggregate these with Agg to obtain succinct commitments (tcm, acm), and derive  $r := \rho(\text{tcm}, \text{acm})$ ;

- 4. prove each circuit  $C'_i$  with ARG and aggregate the resulting inner proofs with Agg.

This approach achieves succinctness while preserving soundness. We provide details of our construction in Section 6.

#### 2.3 Our aggregation scheme for Mirage

To instantiate the foregoing blueprint, we choose the Mirage cc-zkSNARK [KPPS20] as our inner zkSNARK. Mirage is a commit-carrying variant of the Groth16 zkSNARK [Gro16], and inherits the succinctness and prover efficiency of the latter. In more detail, a Mirage proof, like a Groth16 one, consists of three group elements (A, B, C), while the commitment is another group element D. The verifying key, like that of Groth16,

contains elements  $\alpha \in \mathbb{G}_1$  and  $\beta, \delta, \in \mathbb{G}_2$ , as well as an extra element  $\eta \in \mathbb{G}_2$ . To check a proof  $\pi = (A, B, C)$  with respect to a commitment D, the verifier checks that the following pairing equation is satisfied.

$$e(A,B) = e(\alpha,\beta)e(C,\delta)e(D,\eta)$$

.

**Background for** Mirage. To construct an aggregation scheme for Mirage, we follow existing work on aggregation schemes for Groth16 [BMMTV21; GMN22] by relying on *inner-pairing product* argument systems [BCCGP16; BBBPWM18] to enable proving more general bilinear products. Two variants are relevant for our purposes: "MIPPs", which prove the inner product  $\sum_i a_i \cdot B_i$  for (committed) vectors  $\mathbf{a} \in \mathbb{F}^n$ ,  $\mathbf{B} \in \mathbb{G}^n$ , and "TIPPs", which prove the pairing product  $\prod_i e(r^i \cdot A_i, B_i)$  for a scalar r and (committed) vectors  $\mathbf{A} \in \mathbb{G}_1^n$ ,  $\mathbf{B} \in \mathbb{G}_2^n$ .

To construct an aggregation scheme for Mirage that proves the correctness of a batch of Mirage proofs (A, B, C) with respect to commitments D, we will use the above ingredients to prove the following randomized pairing check with respect to a random challenge r:

$$\prod_{i} e(r^{i} \cdot A_{i}, B_{i}) = e(\alpha, \beta)^{\sum_{i} r^{i}} \prod_{i} e(r^{i} \cdot C_{i}, \delta) \prod_{i} e(r^{i} \cdot D_{i}, \eta) .$$

To aggregate these proofs, the aggregation prover first commits to the A, B, C, D using a "structure-preserving" commitment scheme [AFGHO16], hashes these to obtain r, and then proves the above equation using MIPPs and TIPPs. Clearly, the left hand side can be proven using a TIPP, while the remaining terms can be proven using MIPPs. Unfortunately, we are not done yet, as our setting requires us to aggregate proofs for multiple circuits simultaneously.

**Multi-circuit aggregation.** When aggregating multiple circuits, the  $\delta$  and  $\eta$  components of the verifying key differ across circuits, meaning our randomized check changes to the following:

$$\prod_{i} e(r^{i} \cdot A_{i}, B_{i}) = e(\alpha, \beta)^{\sum r^{i}} \prod_{i} e(r^{i} \cdot C_{i}, \delta_{i}) \prod_{i} e(r^{i} \cdot D_{i}, \eta_{i}) .$$

While all the pairing checks can now be proven using TIPPs, preserving succinctness requires care. To see this, let us inspect the two kinds of TIPPs performed in the above equation. Notice that in the TIPP for the left-hand-side check  $(\prod_i e(r^i \cdot A_i, B_i))$ , both arguments are prover-supplied, and hence it is fine for the prover to provide commitments to  $\boldsymbol{A}$  and  $\boldsymbol{B}$ . The TIPPs on the right-hand side, however, involve one prover-supplied argument  $(\boldsymbol{C}$  and  $\boldsymbol{D})$  and one verifier-supplied argument  $(\boldsymbol{\delta}$  and  $\boldsymbol{\eta})$ . While the prover can provide commitments to  $\boldsymbol{C}$  and  $\boldsymbol{D}$ , it would be *unsound* for it to do the same for  $\boldsymbol{\delta}$  and  $\boldsymbol{\eta}$ , as it could commit to arbitrary elements that cause the checks to pass.

Therefore, the verifier must obtain these commitments itself. The straightforward solution of having the verifier compute them itself would violate succinctness. To resolve this issue, we leverage the fact that the subcircuit structure is known at setup time, which in turn means that the vectors  $\delta$  and  $\eta$  are also known at setup time. This means that commitments to the latter can be computed then and included in the verifying key, thus preserving succinctness.

**Reducing the number of TIPPs.** The aggregation scheme proposed so far is sound and relatively efficient. However, it requires the prover to prove multiple TIPPs, worsening prover complexity and proof size. Because aggregation is performed on a single machine (and is not parallelized), improving its prover complexity is important. We do so by devising a method for batching multiple TIPP instances together into a single TIPP instance, and providing a single TIPP proof for the latter.

**Our aggregation scheme for** Mirage. The sketch above omits details, including how we handle public inputs. We provide these details in Section 5.

#### 2.4 Optimizations

The foregoing discussions omit a number of optimizations that we developed to improve the efficiency of our construction. We describe these next.

**Read-only memory.** Notice that we can assume that the memory is read-only, as the prover can initialize the memory with values of all the shared wires, and subcircuits which access these wires can simply check that the memory contains the correct value. This optimization greatly reduces the concrete cost of the local checks performed on the memory traces.

**Reducing SRS size.** The description in the foregoing sections obscures the fact that, as described, each augmented subcircuit  $C_i$  is unique, even if the topology of the underlying subcircuit  $C_i$  is shared with other subcircuits. This is because we need to embed into  $C_i$  information about (a) its circuit number i (so that it can check the trace entries correspond to its own memory access), and (b) the addresses it reads from (so that it reads the appropriate shared wires). Because of this, each subcircuit becomes unique, leading to a blowup in SRS size when we instantiate HEKATON with the Mirage cc-zkSNARK [KPPS20] as the latter has circuit-specific setup (we would need to generate a separate SRS for each subcircuit).

To resolve this issue, we observe that the aforementioned information (circuit number and addresses) is not dependent on the prover's witness, and can be committed to via Mirage's commitment scheme in a preprocessing phase. We provide details in Section 6.3.

**Homogenizing public inputs via Merkle trees.** Recall from Section 2.1.2 that each memory-checking subcircuit  $M_i$  receives as public input the triple  $\mathsf{in}_i = (r, (t, a), (\tau_{k_i}, \alpha_{k_i}))$ , and outputs the pair  $\mathsf{out}_i = ((t', a'), (\tau_{k_{i+1}}, \alpha_{k_{i+1}}))$ . This means that each  $M_i$ 's public input is necessarily different. Existing constructions of aggregation schemes [BMMTV21] can handle such heterogeneous public inputs, but incur prover complexity and proof size overheads. Instead, we propose to homogenize the public inputs of all the subcircuits by careful and selective use of *online* memory checking: we commit to  $(\mathsf{in}_i, \mathsf{out}_i)$  in the i-th leaf of a Merkle tree, and use the corresponding path to verifiably access the i-th leaf in the i-th subcircuit. This allows us to eschew the complex public input handling mechanisms of prior aggregation schemes.

**Batch setup optimization.** We perform a common setup for all circuits simultaneously. This helps us improve efficiency by reducing the number of TIPPs by 1.

#### 3 Preliminaries

**Indexed relations.** An *indexed relation*  $\mathscr{R}$  is a set of triples (i, x, w) where i is the index, x is the instance, and w is the witness; the corresponding *indexed language*  $\mathscr{L}(\mathscr{R})$  is the set of pairs (i, x) for which there exists a witness w such that  $(i, x, w) \in \mathscr{R}$ . An indexed relation is said to be *committable* if the witness can be split into two parts,  $w = (w_1, w_2)$ .

**Definition 3.1** (circuit satisfiability). The committable indexed relation CSAT is the set of triples  $(i, x, w) = ((\mathbb{F}, \ell, m, n, C), x, (w_1, w_2))$  where  $\mathbb{F}$  is a finite field,  $\ell$ , m, and n are natural numbers,  $x \in \mathbb{F}^{\ell}$ ,  $w_1 \in \mathbb{F}^m$ , and  $w_2 \in \mathbb{F}^n$  are vectors, and  $C : \mathbb{F}^{\ell+m+n} \to \mathbb{F}$  is an arithmetic circuit over  $\mathbb{F}$  such that  $C(x, w_1, w_2) = 0$ .

To obtain the usual notion of circuit satisfiability we can set m = 0 and  $w_1 = \bot$ .

**Security parameters.** For simplicity of notation, we assume that all public parameters have length at least  $\lambda$ , so that algorithms which receive such parameters can run in time poly( $\lambda$ ).

**Random oracles.** We denote by  $\mathcal{U}(\lambda)$  the set of all functions that map  $\{0,1\}^*$  to  $\{0,1\}^{\lambda}$ . A *random oracle* with security parameter  $\lambda$  is a function  $\rho: \{0,1\}^* \to \{0,1\}^{\lambda}$  sampled uniformly at random from  $\mathcal{U}(\lambda)$ .

**Bilinear groups.** We denote groups by  $\mathbb{G}$ . A bilinear function  $e: \mathbb{G}_1 \times \mathbb{G}_2 \to \mathbb{G}_T$  is a *type-3 bilinear pairing* if there is no efficiently computable group homomorphism from  $\mathbb{G}_2$  to  $\mathbb{G}_1$ . e is *degenerate* if there is a non-identity  $G \in \mathbb{G}_1$  such that e(G,H) = 1 for all  $H \in \mathbb{G}_2$ . We use additive notation for  $\mathbb{G}_1$  and  $\mathbb{G}_2$ , and multiplicative notation for  $\mathbb{G}_T$ . As shorthand we sometimes write  $[a]_1$  for  $a \cdot G$  and  $[b]_2$  for  $b \cdot H$ .

#### 3.1 Commitment schemes

A commitment scheme CM = (Setup, Commit) over a universe of message spaces  $\{\mathcal{M}_i\}_{i\in\mathbb{N}}$  enables a party to generate a (perfectly) hiding and (computationally) binding commitment to a given message  $m \in \mathcal{M}$ .

- *Setup:* on input a security parameter and a description of the message space  $\mathcal{M}$ , CM.Setup samples a commitment key ck.

- Commitment: on input public parameters ck, message  $m \in \mathcal{M}$ , and randomness r, CM. Commit outputs a commitment C to m.

#### 3.2 Commit-carrying zkSNARKs

A tuple of algorithms ARG =  $(\mathcal{G}, \mathcal{C}, \mathcal{P}, \mathcal{V})$  is a commit-carrying succinct non-interactive argument of knowledge (cc-SNARK) [CFQ19] in the random oracle model (ROM) for a committable indexed relation  $\mathscr{R}$  if it satisfies the following syntax and properties:

- **Setup.** On input a security parameter  $\lambda$  and a set of indices  $[\dot{\mathbf{i}}_i]_{i=1}^n$ ,  $\mathcal{G}$  outputs corresponding proving keys  $[\dot{\mathbf{i}} \mathbf{k}_i]_{i=1}^n$ , commitment keys  $[\dot{\mathbf{i}} \mathbf{k}_i]_{i=1}^n$ , and verification keys  $[\dot{\mathbf{i}} \mathbf{k}_i]_{i=1}^n$ . When n=1, we omit indices.

- Commitment. On input a commitment key ick, a message  $w_1$ , and commitment randomness r, C outputs a commitment cm.

- **Proving.** On input a proving key ipk, an instance x, a witness  $w = (w_1, w_2)$ , and commitment randomness r,  $\mathcal{P}$  outputs a proof  $\pi$ .

- **Verifying.** On input a verification key ivk, an instance x, a commitment cm, and a proof  $\pi$ ,  $\mathcal{V}$  outputs a bit indicating whether  $\pi$  is a valid proof.

Throughout, we assume without loss of generality that the proving key ipk contains ick, ivk and i. These algorithms must satisfy the following properties:

• Multi-instance completeness. For every set of indices  $[i_i]_{i=1}^n$  and every efficient adversary A, the following probability is 1.

$$\Pr\left[\begin{array}{c} \forall i \in [n]: \\ \begin{pmatrix} (\mathbb{i}_i, \mathbb{x}_i, \mathbb{w}_i) \in \mathscr{R} \\ \downarrow \\ \mathcal{V}^{\rho}(\mathsf{i}\mathsf{v}\mathsf{k}_i, \mathbb{x}_i, \mathsf{cm}_i, \pi_i) = 1 \end{pmatrix} \right. \left. \begin{array}{c} ([\mathsf{i}\mathsf{p}\mathsf{k}_i]_{i=1}^n, [\mathsf{i}\mathsf{c}\mathsf{k}_i]_{i=1}^n, [\mathsf{i}\mathsf{v}\mathsf{k}_i]_{i=1}^n) \leftarrow \mathcal{G}^{\rho}(1^{\lambda}, [\mathbb{i}_i]_{i=1}^n) \\ ([\mathbb{x}_i]_{i=1}^n, [\mathbb{w}_i]_{i=1}^n, [\mathsf{i}\mathsf{w}_i]_{i=1}^n) \leftarrow \mathcal{A}^{\rho}([\mathsf{i}\mathsf{p}\mathsf{k}_i]_{i=1}^n) \\ \forall i \in [n]: \mathsf{cm}_i \leftarrow \mathcal{C}^{\rho}(\mathsf{i}\mathsf{c}\mathsf{k}_i, \mathbb{w}_i, 1; r_i) \\ \forall i \in [n]: \pi_i \leftarrow \mathcal{P}^{\rho}(\mathsf{i}\mathsf{p}\mathsf{k}_i, \mathbb{x}_i, \mathbb{w}_i; r_i) \end{array} \right]$$

• Multi-instance knowledge soundness. For every efficient adversary  $\tilde{\mathcal{P}}$  and auxiliary input distribution  $\mathcal{D}$ , there exists an efficient extractor  $\mathcal{E}_{\tilde{\mathcal{P}}}$  such that for every set of indices  $[\hat{\imath}_i]_{i=1}^n$ , the following probability is negligible:

$$\Pr\left[\begin{array}{c} \exists i \in [n]: \\ \begin{pmatrix} (\mathbb{i}_i, \mathbb{X}_i, \mathbb{W}_i) \not\in \mathscr{R} \\ \lor \\ \mathcal{C}^{\rho}(\mathrm{ipk}_i, \mathbb{W}_{i,1}; r_i) \neq \mathrm{cm} \end{pmatrix} \right. \\ \left. \begin{pmatrix} (\mathrm{ipk}_i]_{i=1}^n, [\mathrm{ick}_i]_{i=1}^n, [\mathrm{ivk}_i]_{i=1}^n \end{pmatrix} \leftarrow \mathcal{G}^{\rho}(1^{\lambda}, [\mathbb{i}_i]_{i=1}^n) \\ = \mathrm{aux} \leftarrow \mathcal{D}^{\rho}(1^{\lambda}, [\mathbb{i}_i]_{i=1}^n) \\ = \mathrm{aux} \leftarrow \mathcal{D}^{\rho}(1^{\lambda}, [\mathbb{i}_i]_{i=1}^n) \\ = \mathrm{implies}([\mathbb{X}_i, \mathrm{cm}_i, \pi_i)]_{i=1}^n \leftarrow \mathcal{\tilde{P}}^{\rho}([\mathrm{ipk}_i]_{i=1}^n, \mathrm{aux}) \\ = \mathrm{implies}([\mathbb{W}_i, r_i)]_{i=1}^n \leftarrow \mathcal{E}_{\tilde{\mathcal{P}}}([\mathrm{ipk}_i]_{i=1}^n, \mathrm{aux}) \end{array}\right]$$

• Multi-instance zero-knowledge. There exists an efficient simulator  $S = (S_1, S_2)$  such that for every efficient stateful adversary  $\tilde{V} = (\tilde{V}_1, \tilde{V}_2, \tilde{V}_3)$ , the following probabilities are negligibly close:

$$\Pr\left[\begin{array}{c} \forall i \in [n]: \\ (\mathbb{i}_i, \mathbb{x}_i, \mathbb{w}_i) \in \mathscr{R} \\ \tilde{\mathcal{V}}_3^{\rho}([\operatorname{ipk}_i]_{i=1}^n, [\operatorname{cm}_i]_{i=1}^n, [\pi_i]_{i=1}^n, \operatorname{st}) = 1 \end{array}\right. \left( \begin{array}{c} \rho \leftarrow \mathcal{U}(\lambda) \\ [\mathbb{i}_i]_{i=1}^n \leftarrow \tilde{\mathcal{V}}_1^{\rho}(1^{\lambda}) \\ ([\operatorname{ipk}_i]_{i=1}^n, [\operatorname{ick}_i]_{i=1}^n, [\operatorname{ivk}_i]_{i=1}^n) \leftarrow \mathcal{G}^{\rho}(1^{\lambda}, [\mathbb{i}_i]_{i=1}^n) \\ ([\mathbb{x}_i]_{i=1}^n, [\mathbb{w}_i]_{i=1}^n) \leftarrow \tilde{\mathcal{V}}_2^{\rho}(1^{\lambda}, [\operatorname{ipk}_i]_{i=1}^n) \\ \forall i \in [n]: \operatorname{cm}_i \leftarrow \mathcal{C}^{\rho}(\operatorname{ick}_i, \mathbb{w}_{i,1}) \\ \forall i \in [n]: \pi_i \leftarrow \mathcal{P}^{\rho}(\operatorname{ipk}_i, \mathbb{x}_i, \mathbb{w}_i) \end{array}\right]$$

and

$$\Pr\left[\begin{array}{c} \forall i \in [n]: \\ (\mathbb{i}_i, \mathbb{x}_i, \mathbb{w}_i) \in \mathscr{R} \\ \tilde{\mathcal{V}}_3^{\rho[\mu]}([\mathrm{ipk}_i]_{i=1}^n, [\mathrm{cm}_i]_{i=1}^n, [\pi_i]_{i=1}^n, \mathrm{st}) = 1 \end{array}\right. \left. \begin{array}{c} \rho \leftarrow \mathcal{U}(\lambda) \\ [\mathbb{i}_i]_{i=1}^n \leftarrow \tilde{\mathcal{V}}_1^{\rho}(1^{\lambda}) \\ ([\mathrm{ipk}_i]_{i=1}^n, \tau) \leftarrow \mathcal{S}_1^{\rho}(1^{\lambda}, [\mathbb{i}_i]_{i=1}^n) \\ ([\mathbb{x}_i]_{i=1}^n, [\mathbb{w}_i]_{i=1}^n) \leftarrow \tilde{\mathcal{V}}_2^{\rho}(1^{\lambda}, [\mathrm{ipk}_i]_{i=1}^n) \\ ([\mathrm{cm}_i]_{i=1}^n, [\pi_i]_{i=1}^n, \mu) \leftarrow \mathcal{S}_2^{\rho}([\mathrm{ipk}_i]_{i=1}^n, [\mathbb{x}_i]_{i=1}^n, \tau) \end{array} \right]$$

In the foregoing,  $\rho[\mu]$  is the function that, on input x, equals  $\mu(x)$  if  $\mu$  is defined on x, or  $\rho(x)$  otherwise. This definition uses explicitly-programmable random oracles [BR93]. Note that we can recover the definition of a standard zkSNARK by setting the commitment algorithm  $\mathcal{C}$  to be a no-op and considering n = 1.

#### 3.3 Aggregation schemes

Let  $ARG = (\mathcal{G}, \mathcal{C}, \mathcal{P}, \mathcal{V})$  be a ccSNARK for CSAT. Then, at a high level, an aggregation scheme for ARG is a ccSNARK that proves the validity of a batch of ARG proofs (for possibly different circuits). Formally, an aggregation scheme for ARG is a ccSNARK for the committable indexed relation  $\mathcal{R}_{Agg}$  defined below.

**Definition 3.2** (aggregation relation). The committable indexed relation  $\mathcal{R}_{\mathsf{Agg}}$  is the set of triples

$$(\mathtt{i},\mathtt{x},(\mathtt{w}_1,\mathtt{w}_2)) = ([\mathtt{ivk}_i]_{i=1}^n,\mathtt{x},([\mathtt{cm}_i]_{i=1}^n,[\pi_i]_{i=1}^n))$$

where, for each  $i \in [n]$ ,

- $ivk_i$  is an honestly-generated verification key under ARG for some index  $i_i$  for CSAT,

- x is a valid instance for CSAT with respect to  $i_i$  (i.e.,  $(i_i, x) \in \mathcal{L}(CSAT)$ ),

- $cm_i$  is a commitment, and

- $\pi_i$  is a valid proof under  $ivk_i$  for x, i.e.,  $V(ivk_i, x, cm_i, \pi_i) = 1$ .

## 4 Partitioning circuits via memory checking

We now describe our transformation that partitions a circuit C into augmented subcircuits via the memory-checking infrastructure described in Section 2.1. Our transformation can be decomposed into two steps. First, in Section 4.2, we show how to augment a partitioned circuit C into a 'ROM'-circuit where wires between subcircuits are replaced with memory accesses. Then, in Section 4.3, we show how to check these memory accesses with a memory checker, and how to split the checks performed by the latter across subcircuits.

The resulting transformation, which we denote by  $f = (f_i, f_{w_1}, f_{x,w_2})$ , maps a partitioned circuit instance  $(i, x, w) \in k$ -CSAT (Definition 4.3) to a batch of CSAT instances  $[(i_i, x', (w_{i,1}, w_{i,2}))]_{i=1}^k$  such that x' is of the form  $(1, rt, \alpha, \beta)$ , where  $(\alpha, \beta)$  are field elements, and rt is the root of a Merkle tree. The reduction satisfies the following lemma.

**Lemma 4.1.** There exists an efficient transformation  $f = (f_i, f_{w_1}, f_{x,w_2})$  satisfying the following properties:

- Completeness: For all  $\alpha, \beta \in \mathbb{F}$ , if  $(i, x, w) \in k$ -CSAT, then x is the 0-th leaf of rt and  $(i_i, x', (w_{i,1}, w_{i,2})) \in CSAT$  for all  $i \in [k]$ .

- **Knowledge soundness:** Let CM = (Setup, Commit) be a commitment scheme. There exists an efficient extractor  $\mathcal{E}$  such that for every i, efficient adversary  $\mathcal{A}$  and auxiliary distribution  $\mathcal{D}$ , the following probability is negligible:

$$\Pr\left[\begin{array}{c} (\texttt{i}, \texttt{x}, \texttt{w}) \notin \textit{k-CSAT} \\ (\texttt{i}, \texttt{x}, \texttt{w}) \notin \textit{k-CSAT} \\ & & (\texttt{i}_{i}, \texttt{x}', (\texttt{w}_{i,1}, \texttt{w}_{i,2})) \in \texttt{CSAT} \\ & & (\texttt{w} \in [k] : \\ (\texttt{i}_{i}, \texttt{x}', (\texttt{w}_{i,1}, \texttt{w}_{i,2})) \in \texttt{CSAT} \\ & & (\texttt{w}_{i}]_{i=1}^{n}, \texttt{rt}) \leftarrow \mathcal{W}^{\rho}(\texttt{i}, \texttt{aux}_{\mathcal{W}}) \\ & & (\texttt{w}_{i})_{i=1}^{n}, \texttt{rt}) \leftarrow \mathcal{W}^{\rho}(\texttt{i}, \texttt{aux}_{\mathcal{W}}) \\ & & (\texttt{m} \leftarrow \texttt{CM.Commit}(\texttt{ck}, [\texttt{w}_{i,1}]_{i=1}^{n}) \\ & & (\texttt{a}, \texttt{b}) \leftarrow \rho(\texttt{cm}) \\ \hline & & \texttt{x}' := (\texttt{1}, \texttt{rt}, \texttt{a}, \texttt{b}) \\ & & (\texttt{x}, \texttt{w}) \leftarrow \mathcal{E}^{\rho}_{\mathcal{W}}(\texttt{i}, \texttt{aux}_{\mathcal{W}}) \\ \end{array}\right.$$

We now describe the components of the transformation f, beginning with some notation.

#### 4.1 Notation

We begin by defining a notion of graph and circuit partitions.

**Definition 4.2.** A labelled k-partition V of a graph G = (V, E) is a list  $\{V_1, \ldots, V_k\}$  that partitions the vertex set V. Specifically, V is a k-partition of G if and only if the sets in V are non-empty and mutually disjoint, and the union of these sets equals V.

In the following, let G = (V, E) be a directed acyclic graph, and V a k-partition of G. The *cut-set* of two vertex subsets  $V_1, V_2 \subseteq V$  is defined as the set of edges originating in  $V_1$  and terminating in  $V_2$ . That is,  $cut(V_1, V_2) := \{(u, v) \in E \mid u \in V_1, v \in V_2\}$ . The *reduced* cut-set of  $V_1, V_2$  (denoted d-cut( $V_1, V_2$ )) is obtained from  $cut(V_1, V_2)$  by removing all edges with the same source vertex except the lexicograpically first one. That is, for all  $e = (u, v) \in cut(V_1, V_2)$ ,  $e \in d$ -cut( $V_1, V_2$ ) if and only if there is no v' such that  $(u, v') \in d$ -cut( $V_1, V_2$ ).

We call an arithmetic circuit C partitioned if there exists a k-partition  $C = \{C_1, \dots, C_k\}$  of the underlying graph. Each  $C_i \in C$  is called a *subcircuit* of C. We identify circuits and subcircuits with their underlying graphs. For example, we will call the graph k-partition underlying a partitioned circuit C a k-partition of the circuit itself. This allows us to define the following relation.

**Definition 4.3** (*k*-partitioned circuit satisfiability). The committable indexed relation *k*-CSAT is the set of triples  $(i, x, w) = ((i_{CSAT}, \mathcal{C}), x_{CSAT}, w_{CSAT})$  where  $(i_{CSAT}, x_{CSAT}, w_{CSAT}) \in CSAT$  and  $\mathcal{C} = \{C_1, \dots, C_k\}$  is a *k*-partition of C.

Notice that the set of wires shared between two subcircuits  $C_i, C_j \in \mathcal{C}$  is exactly the reduced cut-set d-cut( $C_i, C_j$ ). We will denote by S the set of all shared wires, i.e.,  $S = \bigcup_{i \neq j} \text{d-cut}(C_i, C_j)$ .

#### 4.2 Eliminating shared wires with ROM circuits

We introduce a new circuit model: circuits with read-only access to a memory bank. We call such circuits **ROM circuits**.

**Definition 4.4.** A **ROM circuit** over the field  $\mathbb{F}$  is an arithmetic circuit over  $\mathbb{F}$  equipped with access to a **memory** M, which is an array of  $\mathbb{F}$  elements that is indexed by the elements of  $\mathbb{F}$ . A ROM circuit, in addition to the standard addition and multiplication gates, contains a read gate that takes as input an index i and outputs the value M[i].

Throughout this section, we will use s to denote the size of a memory bank M.

**Definition 4.5** (*k*-partitioned ROM circuit satisfiability). The indexed relation *k*-RCSAT is the set of all triples (i, x, w) =

$((\mathbb{F},k,\ell,n,s,C,\mathcal{C}),x,(w,M))$  where  $\mathbb{F}$  is a finite field,  $\ell$ , n, and s are natural numbers,  $x \in \mathbb{F}^{\ell}$  and  $w \in \mathbb{F}^n$  are vectors over  $\mathbb{F}$ , M is a memory bank of size s over  $\mathbb{F}$ , and  $C:\mathbb{F}^{\ell+n}\to\mathbb{F}$  is a ROM circuit over  $\mathbb{F}$  with respect to M, such that  $C^M(x,w)=0$  and  $C=\{C_1,\ldots,C_k\}$  is a k-partition of C.

In Figure 3, we provide a formal description of our reduction  $c2r = (c2r_i, c2r_x, c2r_w)$  from *k*-CSAT to *k*-RCSAT that removes shared wires between subcircuits. The following lemma follows from the construction of the reduction.

**Lemma 4.6.** The function  $c2r = (c2r_{i}, c2r_{x}, c2r_{w})$  defined in Fig. 3 is a reduction from k-CSAT to k-RCSAT. That is,  $(i, x, w) \in k$ -CSAT if and only if  $(i_{M}, x_{M}, w_{M}) \in k$ -RCSAT, where  $i_{M} = c2r_{i}(i)$ ,  $x_{M} = c2r_{x}(x)$ , and furthermore, there are no shared wires between the subcircuits in  $i_{M}$ .

#### 4.3 Reducing partitioned ROM circuits to committable circuits

We now show how to reduce the problem of checking satisfiability of an instance of *k*-RCSAT to that of checking simultaneous satisfaction of *k* instances of CSAT. For this we use the notion of a *memory trace* [BCGT13; BCGTV13; BCTV14b; ZGKPP18]. Informally, a memory trace is a list of entries recording memory reads performed by a ROM circuit.

**Definition 4.7.** A memory trace entry is a tuple e = (t, i, v), where  $t \in [s]$  is the index of the subcircuit that performed this operation, i is the memory address accessed, and v is the value read from M[i]. A memory trace is a list of memory trace entries, one for each read gate in a ROM circuit.

We will consider memory traces whose entries are sorted by subcircuit index (denoted T), and by memory address (denoted A).

**Notation.** We now introduce some notation for partitioning memory traces arising from a k-partitioned ROM CSAT instance  $(\mathbb{F}, \ell, n, s, R, \mathcal{R} = \{R_1, \dots, R_k\})$ . Denote by  $s_i$  the number of read gates in the i-th subcircuit  $R_i$ ,

```

c2r_{i}(i = (\mathbb{F}, k, \ell, n, C, C)) \rightarrow i_{M}:

1. Parse C as \{C_1, ..., C_k\}.

2. Initialize an empty memory bank M and a counter t := 0.

3. For each i \in [k], initialize new ROM subcircuits R_i := C_i.

4. For each pair of distinct subcircuits C_i, C_j \in \mathcal{C}, and for each shared wire w = (u, v) \in \text{d-cut}(C_i, C_j):

(a) Append a new entry to M containing the value of w, and increment t.

(b) Add read gates to R_i and R_j that read index t of the memory M.

(c) Add to R_i a new equality check between u and the output of the new read gate.

(d) For every wire w' = (u, v') \in \text{cut}(C_i, C_i) with the same source u as w:

i. Remove w' from R_i and R_j.

ii. Add to R_i a new equality check between v' and the output of the new read gate.

5. Denote by R the circuit whose partition is \mathcal{R} = \{R_1, \dots, R_k\}.

6. Denote by s the size of M, and by \ell' and n' the number of public input and witness wires in R, respectively.

7. Output (\mathbb{F}, \ell', n', s, R, \mathcal{R}).

c2r_{\mathbb{X}}(\mathbb{X}) \to \mathbb{X}_M: Output \mathbb{X}_M := \mathbb{X}.

c2r_w(i,x,w) \rightarrow w_M:

1. Use c2r_{i}(i) to obtain the ROM circuit R.

2. Use x and w to compute the witness w_M for R (i.e., the wires w_M and the contents of M).

3. Output w_M.

```

**Figure 3:** Reduction from *k*-CSAT to *k*-RCSAT.

by  $k_i = \sum_{j=1}^{i-1} s_j$  the cumulative number of read gates in circuits  $R_1, \dots, R_{i-1}$ , and by  $S_i = \{k_i + 1, \dots, k_{i+1}\}$  the set of (indices of) all read gates in  $R_i$ .

Let  $T = (T_1, ..., T_s)$  and  $A = (A_1, ..., A_s)$  denote the subcircuit-sorted and the address-sorted memory traces respectively. Then the *i*-th subcircuit-sorted subtrace  $T_i$  is defined as  $T_i := (T_{k_i+1}, ..., T_{k_i+s_i})$ . Note that, by construction, the subcircuit index of each entry in  $T_i$  equals i, i.e.  $T_i$  contains only those trace entries that correspond to the memory reads made by  $R_i$ . Denote by  $T_i$  the last entry in  $T_i$ . Similarly, the  $T_i$  address-sorted subtrace is defined as  $T_i := (T_{k_i+1}, ..., T_{k_i+s_i})$ , and  $T_i := (T_i, ..., T_i)$ .

**Construction intuition.** We begin by noting that valid memory traces for ROM circuits produced by the reduction in Section 4.2 should satisfy the following properties:

- 1. **Values are consistent:** If consecutive entries (t, i, v) and (t', i', v') in the trace **A** have the same address (i.e. i = i'), they must have the same values (v = v').

- 2. Every subcircuit reads: Consecutive entries (t, i, v) and (t', i', v') in T satisfy the constraint that either t = t' or t = t' + 1. If t = t', then it must be that  $i \le i'$ .

- 3. Every address is read: Consecutive entries (t, i, v) and (t', i', v') in **A** must satisfy the constraint that either i = i' or i = i' + 1. If i = i', then it must be that  $t \le t'$ .

- 4. Traces are consistent: T and A are permutations of each other.

We now describe the intuition behind our reduction  $f^k = (f_1^k, f_{w_1}^k, f_{w_1}^k, f_{x,w_2}^k)$  from k-RCSAT to k-CSAT, deferring to Figure 4 the formal pseudocode of the reduction.

The function  $f_i^k$  constructs a set of k 'commit-carrying' circuits  $R_i'$  by relying on the following observations. Checks 1 to 3 are entirely local as they inspect only consecutive entries in  $T_i$  and  $A_i'$ , and can thus be enforced by each subcircuit  $R_i$  independently. Check 4, on the other hand, is a global property that requires coordination

<sup>&</sup>lt;sup>3</sup>Note that  $A_i$  can be entirely disjoint from  $T_i$ , i.e., it might contain no entries corresponding to  $C_i$ 's memory accesses.

between the subcircuits. To enable this coordination, we store the running trace evaluations (as well as the last entries of the sorted traces) in a Merkle tree, and give to each subcircuit the root of this tree as public input. In more detail, each circuit  $R'_i$  is constructed as follows.

- $R'_i$  takes as public input  $x' = (1, rt, \alpha, \beta)$  where  $\alpha, \beta \in \mathbb{F}$  are field elements, and rt is a Merkle tree root. (We will specify how these are obtained below.)

- $R'_i$  takes as input a witness that can be split two parts,  $w_{i,1}$  and  $w_{i,2}$ , where the first contains the subtraces  $T_i$  and  $A_i$ , while the second contains the witness wires of  $R_i$  and two Merkle paths.

- $R_i'$  enforces (a) that the input Merkle paths are valid paths for the i-1-th and the i-th leaves in a Merkle tree with root rt; (b) that the i-th leaf of the Merkle tree contains the last entries  $t_i$  and  $a_i$  of  $T_i$  and  $A_i$  respectively; (c) the correctness of running trace evaluations  $T_i(\alpha,\beta)$  and  $A_i(\alpha,\beta)$ , where  $T_i(X,Y) := \prod_{j=1}^{k_{i+1}} (X (t_j^T + Y \cdot i_j^T + Y^2 \cdot v_j^T))$  and  $A_i(X,Y) := \prod_{j=1}^{k_{i+1}} (X (t_j^A + Y \cdot i_j^A + Y^2 \cdot v_j^A))$ ; and (d) that the 0-th leaf holds the public input x of R.

The reduction satisfies the following lemma, which roughly says that when the inputs  $\alpha$ ,  $\beta$  are chosen by hashing commitments to the memory traces, the output circuits are satisfiable if and only if the input ROM circuit is satisfiable.

**Lemma 4.8.** Let CM = (Setup, Commit) be a commitment scheme. Then  $f^k = (f_i^k, f_{w_1}^k, f_{x,w_2}^k)$  defined in Fig. 4 on input  $(i, x, (w, M), \alpha, \beta)$ , outputs  $([i_i]_{i=1}^k, x', [w_{i,1}]_{i=1}^k, [w_{i,2}]_{i=1}^k)$  such that the following properties hold:

- Completeness: For all  $\alpha, \beta \in \mathbb{F}$ , if  $(i, x, (w, M)) \in k$ -RCSAT, then  $(i, x', (w_{i,1}, w_{i,2})) \in CSAT$  for all  $i \in [k]$  and x is the 0-th leaf of rt.

- **Knowledge soundness:** There exists an efficient extractor  $\mathcal{E}$  such that for every  $\mathcal{A}$  the following probability is negligible:

$$\Pr\left[\begin{array}{c} (\texttt{i}, \texttt{x}, (\texttt{w}, M)) \notin k\text{-RCSAT} \\ (\texttt{i}, \texttt{x}, (\texttt{w}, M)) \notin k\text{-RCSAT} \\ & \& \\ \forall i \in [k]: \\ (\texttt{i}_i, \texttt{x}', (\texttt{w}_{i,1}, \texttt{w}_{i,2})) \in \text{CSAT} \\ & \& \\ & \texttt{x} \text{ is the } 0\text{-th leaf} \\ & of \text{ rt} \end{array}\right. \left. \begin{array}{c} \rho \leftarrow \mathcal{U}(\lambda) \\ (\texttt{i}_i)_{i=1}^n = f_i(\texttt{i}, \mathcal{C}) \\ \texttt{ck} \leftarrow \text{CM.Setup}(1^{\lambda}, \mathcal{M}_i) \\ \hline \\ (\texttt{w}_i)_{i=1}^n, \text{rt}) \leftarrow \mathcal{W}^{\rho}(\texttt{i}, \texttt{aux}_{\mathcal{W}}) \\ \texttt{cm} \leftarrow \text{CM.Commit}(\texttt{ck}, [\texttt{w}_{i,1}]_{i=1}^n) \\ (\alpha, \beta) \leftarrow \rho(\texttt{cm}) \\ \hline \\ & \texttt{x}' := (1, \text{rt}, \alpha, \beta) \\ (\texttt{x}, (\texttt{w}, M)) \leftarrow \mathcal{E}^{\rho}_{\mathcal{W}}(\texttt{i}, \texttt{aux}_{\mathcal{W}}) \end{array} \right]$$

*Proof.* Completeness. Let  $\alpha, \beta$  be arbitrary elements of  $\mathbb{F}$  and parse i as  $(\mathbb{F}, k, \ell, n, s, R, \mathcal{R})$  and x' as  $(1, rt, \alpha, \beta)$ . By construction, x is the 0-th leaf of the Merkle tree with root rt.

If  $(i, x, (w, M)) \in k$ -RCSAT, then  $R^M(x, w) = 0$ , which in turn implies that we can construct appropriate memory sub-traces  $[w_{i,1} = (\boldsymbol{T}_i, \boldsymbol{A}_i)]_{i=1}^k$  and witnesses  $[w_{i,2}]_{i=1}^k$  such that  $(i, x', (w_{i,1}, w_{i,2})) \in CSAT$  for all  $i \in [k]$ .

**Knowledge soundness.** We construct an extractor  $\mathcal{E}$  such that if  $(i_i, x', (w_{i,1}, w_{i,2})) \in CSAT$  for all  $i \in [k]$ , the probability that  $\mathcal{E}$  fails to produce (x, (w, M)) such that  $(i, x, (w, M)) \in k$ -RCSAT and x is the 0-th leaf of rt is negligible.  $\mathcal{E}$  works as follows:

```

f_{\mathbf{i}}^k(\mathbf{i}) \to [\mathbf{i}_i]_{i=1}^k:

```

Parse  $i = (\mathbb{F}, \ell, n, s, R, \mathcal{R} = \{R_1, \dots, R_k\})$  and construct circuits  $[C_i]_{i=1}^k$  by augmenting  $[R_i]_{i=1}^k$  as follows:

- 1. Each  $C_i$  takes as public input x' and takes as witness  $w_{i,1}$  and  $w_{i,2}$ . The contents of these are as described in the construction intuition.

- 2. For each  $i \in [k] \setminus \{1\}$ , augment  $C_i$  further as follows:

- (a) Replace the output wire of the j-th read gate in  $R_i$  with a wire carrying the value of the j-th entry in  $T_i$ .

- (b)  $C_i$  parses  $w_{i,2}$  as Merkle proofs  $\pi_{rt}^{i-1}$  and  $\pi_{rt}^i$ , and checks that:

- For each  $j \in \{i-1,i\}$ ,  $\pi_{rt}^{j}$  is a valid path with respect to rt for the j-th leaf with value  $(\boldsymbol{t}_i, \boldsymbol{a}_i, T_i(\alpha, \beta), A_i(\alpha, \beta)).$

- The trace  $(t_{i-1}, T_i)$  is sorted by the label  $t_i^T$ , and the trace  $(a_{i-1}, A_i)$  is sorted by the address  $t_i^A$ .

- Entries of  $(a_{i-1}, A_i)$  with the same address  $i_i^A$  contain the same value  $v_i^A$ , and that consecutive values of  $i_i^A$  differ by at most 1.

- The running products are computed correctly:

$$T_i(\alpha, \beta) = T_{i-1}(\alpha, \beta) \cdot \prod_{j \in \mathcal{S}_i} (\alpha - (t_j^T + \beta \cdot i_j^T + \beta^2 \cdot v_j^T)), \text{ and } A_i(\alpha, \beta) = A_{i-1}(\alpha, \beta) \cdot \prod_{j \in \mathcal{S}_i} (\alpha - (t_j^A + \beta \cdot i_j^A + \beta^2 \cdot v_j^A)).$$

- The entries  $t_i$  and  $a_i$  are the last entries of  $T_i$  and  $A_i$  respectively.

- 3.  $C_1$  is augmented to perform analogous checks on leaf 1 of the Merkle tree and to additionally check that x in leaf 0 is consistent with its wires.

- 4. For each  $i \in [k]$ , compute  $\ell'_i, n'_i, m'_i$  to be the sizes of  $\mathbf{x}'_i, \mathbf{w}_{i,1}$  and  $\mathbf{w}_{i,2}$  respectively. Output  $[(\mathbb{F}, \ell'_i, n'_i, m'_i, C_i)]_{i=1}^k$ .

```

f_{w_1}^k(i,x,(w,M)) \to [w_{i,1}]_{i=1}^k:

1. Parse i as ((\mathbb{F},\ell,n,s,R),\mathcal{R}).

```

- 2. Construct the memory traces T and A by executing  $R^M(x, w)$ , and partition them to obtain  $[T_i]_{i=1}^k$  and  $[A_i]_{i=1}^k$ .

- 3. Output  $[w_{i,1} = (T_i, A_i)]_{i=1}^k$ .

```

f_{\mathbf{x},\mathbf{w}_2}^k(\mathbf{i},\mathbf{x},(\mathbf{w},\mathbf{M}),\boldsymbol{\alpha},\boldsymbol{\beta}) \to (\mathbf{x}',[\mathbf{w}_{i,2}]_{i=1}^k):

```

- 1. Parse i as  $((\mathbb{F}, \ell, n, s, R), \mathcal{R})$ .

- 2. Compute the augmented indices  $[\mathbf{i}'_i]_{i=1}^k := f_{\mathbf{i}}^k(\mathbf{i})$ .

- 3. Construct the memory traces T and A by executing  $R^M(x, w)$ .

- 4. Use x,  $\alpha$ ,  $\beta$ , T and A to construct a Merkle tree with root rt with the 0-th leaf containing x and the i-th leaf containing ( $\boldsymbol{t}_i, \boldsymbol{a}_i, T_i(\alpha, \beta), A_i(\alpha, \beta)$ ).

- 5. Partition w into disjoint subwitnesses  $w_1, \dots, w_k$ , corresponding to  $R_1, \dots, R_k$  respectively.

- 6. For each  $i \in [k]$ , construct  $w_{i,2}$  to contain  $w_i$  and the Merkle paths for leaves i-1 and i of the Merkle tree.

- 7. Output  $(\mathbf{x}' := (1, \mathsf{rt}, \alpha, \beta), [\mathbf{w}_{i,2}]_{i=1}^k)$ .

**Figure 4:** Reduction from k-RCSAT to k instances of CSAT.

$\mathcal{E}^{

ho}_{\mathcal{W}}(\mathtt{i},\mathsf{aux}_{\mathcal{W}}) o (\mathtt{x},(\mathtt{w},\mathit{M}))$ :

- 1. Parse i as  $(\mathbb{F}, k, \ell, n, s, R, \mathcal{R})$  and compute  $[i'_{i}]_{i=1}^{k} = f_{i}^{k}(i)$ .

- 2. Obtain  $([(\mathbf{w}_{i,1}, \mathbf{w}_{i,2})]_{i=1}^n, \mathsf{rt}) \leftarrow \mathcal{W}^{\rho}(\mathbf{i}, \mathsf{aux}_{\mathcal{W}}).$

- 3. Compute  $(\alpha, \beta) \leftarrow \rho(\mathsf{CM}.\mathsf{Commit}(\mathsf{ck}, [\mathbb{w}_{i,1}]_{i=1}^n))$ .

- 4. Set  $x' := (1, rt, \alpha, \beta)$ .

- 5. For all i in  $\{1,\ldots,k\}$  parse  $w_{i,1}$  as  $(\boldsymbol{T}_i,\boldsymbol{A}_i)$  and construct  $\boldsymbol{T}=\boldsymbol{T}_1||\cdots||\boldsymbol{T}_k$  and  $\boldsymbol{A}=\boldsymbol{A}_1||\cdots||\boldsymbol{A}_k$ .

- 6. For all  $i \in [k] \setminus \{1\}$ , check that the values read from the *i*-th leaf of the Merkle tree with root rt are consistent in  $w_{i-1,2}$  and  $w_{i,2}$ .

- 7. Check that **T** is sorted by subcircuit index, **A** is sorted by address, and that **T** and **A** are permutations of each other.

- 8. Construct the memory M from T and A.

- 9. For all  $i \in [k]$ , parse  $w_{i,2}$  to obtain  $w_i$  corresponding to  $R_i$  and the Merkle paths for leaves i-1 and i of the tree corresponding to rt.

- 10. Use  $[w_i]_{i=1}^k$  to reconstruct w.

- 11. Use the merkle path from  $w_{1,2}$  to set x to be the value in the 0-th leaf of the Merkle tree.

- 12. Output (x, (w, M)).

We prove the following claim about the extractor  $\mathcal{E}$ .

**Claim 4.9.** Given that  $(i_i, x', (w_{i,1}, w_{i,2})) \in \text{CSAT}$  for all  $i \in [k]$ , if the extractor  $\mathcal{E}$  does not abort, it outputs a valid (x, (w, M)) such that  $(i, x, (w, M)) \in k\text{-RCSAT}$ .

*Proof.* Since the public input of R is used only in the first subcircuit  $R_1$ , the fact that  $(i_1, x', (w_{1,1}, w_{1,2})) \in CSAT$  and the extracted x is exactly the 0-th leaf of rt implies that the public input of R is consistent with x, by construction of  $C_1$ .

Since  $\mathcal{E}$  does not abort, this implies that all the values read from the Merkle tree are consistent amongst all k subcircuits and T and A are permutations of each other.

By construction of each index  $[i]_{i=1}^k$ , and because for each i,  $(i_i, x', (w_{i,1}, w_{i,2})) \in CSAT$ , we have that the witness w and memory M extracted by  $\mathcal{E}$  are such that  $R^M(x, w) = 1$ .

It is now sufficient to prove that the extractor aborts with negligible probability, which we do in the following claim.

**Claim 4.10.** Given that  $(i_i, x', (w_{i,1}, w_{i,2})) \in CSAT$  for all  $i \in [k]$ , the extractor  $\mathcal{E}$  aborts with negligible probability.

*Proof.* The extractor only aborts if the values read from the Merkle tree are not consistent amongst all k subcircuits, or if T and A are not permutations of each other.

The probability that the adversary can open the same leaf to two different values is negligible, and so it must be the case that, except with negligible probability, the values read from the Merkle tree are consistent amongst all *k* subcircuits.

Now,  $(i_i, x', (w_{i,1}, w_{i,2})) \in CSAT$  for all  $i \in [k]$ , implies that T is a valid time sorted trace, A is a valid address sorted trace, and  $T(\alpha, \beta) = A(\alpha, \beta)$ , where  $T(X, Y) := \prod_{j=1}^s (X - (t_j^T + Y \cdot i_j^T + Y^2 \cdot v_j^T))$  and  $A(X, Y) := \prod_{j=1}^s (X - (t_j^A + Y \cdot i_j^A + Y^2 \cdot v_j^A))$ . Lemma B.1 now implies that, except with negligible probability, T(X, Y) = A(X, Y), thus implying that T and A are permutations of each other.

Thus overall the probability of abort is negligible.

## 5 Aggregation scheme for Mirage

We now describe our aggregation scheme for the Mirage commit-carrying zkSNARK (Section 5.1.1). We describe the aggregation scheme and prove it secure in Section 5.3. A key building block of our construction is a method to prove the correctness of multiple pairing products simultaneously. We describe this building block in Section 5.2.

Throughout this section we assume that the public inputs to each subcircuit are of the form  $(1, rt, \alpha, \beta)$  as this is what the reduction in Section 4 mandates. We also assume Agg. C does not take any randomness as input as Agg does not have to be hiding.

#### 5.1 Background

We begin by recalling some results from prior work [BMMTV21; GMN22] that we will use in our construction.

**Commitment schemes.** The commitment scheme  $CM_D$  [GMN22] is defined as follows.

```

\mathsf{CM}_{D}.\mathsf{Setup}(\mathbb{G}_{1}^{n},\mathbb{G}_{2}^{n}) \colon \\ 1. \ \mathsf{Sample} \ a,b \leftarrow \mathbb{F}. \\ 2. \ \mathsf{Set} \ \mathbf{v}_{1} \coloneqq [a^{i}H]_{i=0}^{n-1}, \text{ and } \mathbf{v}_{2} \coloneqq [b^{i}H]_{i=0}^{n-1}. \\ 3. \ \mathsf{Set} \ \mathbf{w}_{1} \coloneqq [a^{i}G]_{i=n}^{2n-1}, \text{ and } \mathbf{w}_{2} \coloneqq [b^{i}G]_{i=n}^{2n-1}. \\ 4. \ \mathsf{Output} \ \mathsf{ck}_{D} \coloneqq (\mathbf{v}_{1},\mathbf{v}_{2},\mathbf{w}_{1},\mathbf{w}_{2}). \\ 5. \ \mathsf{Set} \ T \coloneqq \prod_{i=0}^{n-1} e(A_{i},a^{i}H) \cdot \prod_{i=0}^{n-1} e(a^{n+i}G,B_{i}). \\ 6. \ \mathsf{Set} \ U \coloneqq \prod_{i=0}^{n-1} e(A_{i},b^{i}H) \cdot \prod_{i=0}^{n-1} e(b^{n+i}G,B_{i}). \\ 7. \ \mathsf{Output} \ C \coloneqq (T,U).

```

We will also use  $CM_1$  and  $CM_2$ , two special cases of the above commitment scheme. In the former, the  $\mathbb{G}_2$  component of the message is ignored, while in the latter, the  $\mathbb{G}_1$  component is ignored. That is,  $CM_1$  is a commitment scheme with message space  $\mathbb{G}_1^n$ , while  $CM_2$  is a commitment scheme with message space  $\mathbb{G}_2^n$ . In fact,  $CM_1$  is the same as the commitment scheme  $CM_S$  from [GMN22].

We now define two relations associated with the above commitment schemes. These are slightly modified versions of the relation  $\mathcal{R}_{TIPP}$  defined in [BMMTV21]:

**Definition 5.1** (seprate pairing product relation). The indexed relation  $\mathcal{R}_{SPP}$  is the set of triples

$$(\mathbf{i},\mathbf{x},\mathbf{w}) = (\mathsf{ck}_D,(\mathsf{cm}_A^1,\mathsf{cm}_B^2,Z,r),(\pmb{A}',\pmb{B}))$$

where  $\mathsf{ck}_D$  is a commitment key for the commitment schemes  $\mathsf{CM}_1$  and  $\mathsf{CM}_2$  (Section 3.1),  $\mathsf{cm}_A^1$  and  $\mathsf{cm}_B^2$  are commitments under  $\mathsf{CM}_1$  and  $\mathsf{CM}_2$ , Z is the claimed pairing product of A' and B, C is a field element, and C is a field element element element.

$$\mathsf{cm}_A^1 = \mathsf{CM}_1.\mathsf{Commit}(\mathsf{ck}_D, \pmb{r}^{-1} \circ \pmb{A}')$$

$\mathsf{cm}_B^2 = \mathsf{CM}_2.\mathsf{Commit}(\mathsf{ck}_D, \pmb{B})$

$Z = \pmb{A}' * \pmb{B}$

**Definition 5.2** (combined pairing product relation). The indexed relation  $\mathcal{R}_{CPP}$  is the set of triples

$$(\mathbf{i},\mathbf{x},\mathbf{w}) = (\mathsf{ck}_D,(\mathsf{cm}^D,Z,r),(\pmb{A}',\pmb{B}))$$

where  $ck_D$  is a commitment key for the commitment scheme  $CM_D$  (Section 3.1),  $cm^D$  is a commitment under  $\mathsf{CM}_D$ , Z is the claimed pairing product of  $\mathbf{A}'$  and  $\mathbf{B}$ , r is a field element, and  $\mathbf{A}' \in \mathbb{G}_1^n$  and  $\mathbf{B} \in \mathbb{G}_2^n$  are vectors of group elements such that

$$\mathsf{cm}^D = \mathsf{CM}_D.\mathsf{Commit}(\mathsf{ck}_D, \mathbf{r}^{-1} \circ \mathbf{A}', \mathbf{B})$$

$Z = \mathbf{A}' * \mathbf{B}$

#### Mirage: commit-carrying Groth16

Below we describe the commit-carrying zkSNARK Mirage [CFQ19; KPPS20]. We note that while [KPPS20] does not have a formal statement regarding the binding property of Mirage, the ccGro16 construction in [CFQ19] is morally the same as Mirage, except that the latter handles public inputs as well. As a result, Theorem H.1 from [CFQ19] can easily be extended to prove knowledge soundness for Mirage. For simplicity, in our use case, we use a construction of ARG where  $ipk_i = ick_i$  for all  $i \in [n]$ .

$\mathsf{Mirage}.\mathsf{Setup}(\lambda,[\mathtt{i}_i]_{i=1}^n) \to ([\mathsf{ipk}_i]_{i=1}^n,[\mathsf{ick}_i]_{i=1}^n,[\mathsf{ivk}_i]_{i=1}^n) :$

- 1. For each i in  $\{1,\ldots,n\}$ , parse  $i_i$  as  $(\mathbb{F},\ell_i,m_i,n_i,C_i)$  and construct from it the QAP index  $(\mathbb{F},t_i(X),\boldsymbol{a}_i(X),\boldsymbol{b}_i(X),\boldsymbol{c}_i(X))$ .

- 2. Sample  $\alpha, \beta, [\gamma_i]_{i=1}^n, [s_i]_{i=1}^n \leftarrow \mathbb{F}$  and  $[\delta_i]_{i=1}^n, [\eta_i]_{i=1}^n \leftarrow \mathbb{F}$ .

- 3. For each  $i \in [n]$  and  $j \in [\ell_i + m_i + n_i]$ , define  $p_{i,j}(X) := \beta a_{i,j}(X) + \alpha b_{i,j}(X) + c_{i,j}(X)$ .

- 4. For each i in [n], construct the verifying, committing, and proving keys, and output these:

$$\begin{split} \mathrm{ivk}_i &:= \left( e([\alpha]_1, [\beta]_2), [\gamma_i]_2, [\delta_i]_2, [\eta_i]_2, \left\{ \left[ p_{i,j}(s_i)/\gamma_i \right]_1 \right\}_{j=0}^{\ell_i-1} \right); \quad \mathsf{ck}_i := \left( \left[ \delta_i \right]_1, \left\{ \left[ p_{i,j}(s_i)/\eta_i \right]_1 \right\}_{j=\ell_i}^{\ell_i+m_i-1} \right) \\ \mathrm{ipk}_i &:= \left( \mathsf{ck}_i, \mathrm{ivk}_i, \left\{ \left[ s_i^j \right]_1, \left[ s_i^j \right]_2 \right\}_{j=0}^{\ell_i+m_i+n_i-1}, \left\{ \left[ p_{i,j}(s)/\delta_i \right]_1 \right\}_{j=\ell_i+m_i}^{\ell_i+m_i+n_i-1}, \left\{ \left[ s_i^j t_i(s_i)/\delta_i \right]_1 \right\}_{j=0}^{\ell_i+m_i+n_i-1} \right); \quad \mathrm{ick}_i := \mathrm{ipk}_i \end{split}$$

5. Output  $([ipk_i]_{i=1}^n, [ick_i]_{i=1}^n, [ivk_i]_{i=1}^n)$ .

Mirage.Commit(ick,  $w'_C$ ,  $\kappa_D$ )  $\rightarrow$  D:

- 1. Obtain ck from ick and parse ck as  $([\delta]_1, \{[p_i(s)/\eta]_1\}_{i=\ell}^{\ell+m-1}).$

- 2. Obtain partial QAP witness  $\mathbf{w}' = [w_i]_{i=\ell}^{\ell+m-1}$  from  $\mathbf{w}'_C$ .

- 3. Define  $V_1(X) := \sum_{i=\ell}^{\ell+m-1} w_i \cdot p_i(X)$ .

- 4. Output  $D := [V_1(s)/\eta]_1 + [\kappa_D \delta]_1$

Mirage. Verify(ivk,  $x_C$ , D,  $\pi$ )  $\rightarrow$  {0, 1}:

- 1. Obtain the QAP instance x from  $x_C$ .

- 2. Parse proof  $\pi$  as (A,B,C).

- 3. Check that e(A,B) =

$$e([\alpha]_1, [\beta]_2) e(\left[\sum_{i=0}^{\ell-1} \frac{\mathbf{x}_i p_i(s)}{\gamma}\right]_1, [\gamma]_2) e(C, [\delta]_2) e(D, [\eta]_2).$$