# **Compact Circuits for Efficient Möbius Transform**

Subhadeep Banik<sup>1</sup>, and Francesco Regazzoni<sup>2,1</sup>

<sup>1</sup> Universita della Svizzera Italiana, Lugano, Switzerland, subhadeep.banik@usi.ch

<sup>2</sup> University of Amsterdam, Amsterdam, Netherlands, f.regazzoni@uva.nl

**Abstract.** The Möbius transform is a linear circuit used to compute the evaluations of a Boolean function over all points on its input domain. The operation is very useful in finding the solution of a system of polynomial equations over GF(2) for obvious reasons. However the operation, although linear, needs exponential number of logic operations (around  $n \cdot 2^{n-1}$  bit xors) for an *n*-variable Boolean function. As such, the only known hardware circuit to efficiently compute the Möbius Transform requires silicon area that is exponential in n. For Boolean functions whose algebraic degree is bound by some parameter d, recursive definitions of the Möbius Transform exist that requires only  $O(n^{d+1})$  space in software. However converting the mathematical definition of this space-efficient algorithm into a hardware architecture is a non-trivial task, primarily because the recursion calls notionally lead to a depth-first search in a transition graph that requires context switches at each recursion call for which straightforward mapping to hardware is difficult. In this paper we look to overcome these very challenges in an engineering sense. We propose a space efficient sequential hardware circuit for the Möbius Transform that requires only polynomial circuit area (i.e.  $O(n^{d+1})$ ) provided the algebraic degree of the Boolean function is limited to d. We show how this circuit can be used as a component to efficiently solve polynomial equations of degree at most d by using fast exhaustive search. We propose three different circuit architectures for this, each of which uses the Möbius Transform circuit as a core component. We show that asymptotically, all the solutions of a system of m polynomials in n unknowns and algebraic degree d over GF(2) can be found using a circuit of silicon area proportional to  $m \cdot n^{d+1}$  and circuit depth proportional to  $2 \cdot \log_2(n-d).$

In the second part of the paper we introduce a fourth hardware solver that additionally aims to achieve energy efficiency. The main idea is to reduce the solution space to a small enough value by parallel application of Möbius Transform circuits over the first few equations of the system. This is done so that one can check individually whether the vectors of this reduced solution space satisfy each of the remaining equations of the system using lower power consumption. The new circuit has area also bound by  $m \cdot n^{d+1}$  and has circuit depth proportional to  $d \cdot \log_2 n$ . We also show that further optimizations with respect to energy consumption may be obtained by using depth-bound Möbius circuits that exponentially decrease run time at the cost of additional logic area and depth.

Keywords: Boolean Functions, Möbius transform, Solution of Equation System.

## 1 Introduction

Several cryptanalytic problems can be reduced to instances of solving a system of multivariate polynomial equations over GF(2). For example, block ciphers with low multiplicative complexity like LowMC [ARS<sup>+</sup>15] employ only 3-bit S-boxes of algebraic degree 2. It is known that given any single plaintext-ciphertext pair from an *r*-round instance of LowMC gives rise to a system of equations in the secret key-bits of algebraic degree  $2^{r/2}$  [Din21]. The public key in the signature scheme **PICNIC v3.0**, consists of a single

Licensed under Creative Commons License CC-BY 4.0.

plaintext/ciphertext pair generated by the LowMC block cipher using the secret key as the block cipher key. The designers recommend using 4-round instances of the block cipher for this purpose. In this case, the secret key that corresponds to a given public key is fully described by a system of n Boolean equations of degree 4 in the in the n unknown bits of the key [Din21]. Thus finding the secret key amounts to cryptanalysis of the block cipher using the single plaintext/ciphertext pair available as the public key of the signature, which amounts to solving n degree 4 equations in n unknowns. (However, we would like to state that our work does not practically threaten the full specification of PICNIC.) It is also known that forging a signature in public key signature schemes like UOV can be done by solving a set of quadratic equations over GF(2) [KPG99]. Other than this there are specific problems in combinatorics like the graph-coloring problem (i.e. given a graph decide whether it can be colored using k colors with no two adjacent vertices assigned the same color) which can be reduced to an instance of solving multi-variate polynomials in GF(2) [Bar09, Appendix C].

The problem can be stated in the following way: given n indeterminates  $x_1, x_2, \ldots, x_n$ , and m polynomials  $f_i \in \mathbb{F}[x_1, x_2, \ldots, x_n]$  (for  $i \in [1, m]$ ), where  $\mathbb{F}$  is any finite field. The task is to find common solutions  $x^* \in \{0, 1\}^n$ , such that  $f_i(x^*) = 0$  for all i. Over any finite field  $\mathbb{F}$ , the problem is NP-complete already when the polynomials are quadratic. For a complete analysis of the significance of equation solvers in cryptography please see the discussion in [Bou22]. Hereafter, we will focus on the case of the Boolean field  $\mathbb{F} = GF(2)$ .

#### 1.1 Previous Work

To the best of our knowledge, there have been two previous works on hardware/software architectures for fast exhaustive search over GF(2). The main idea is as follows: the secret  $x^*$  we are looking for is obviously a point which evaluates to zero for all the  $f_i$ . Thus at the index  $x^*$ , the truth tables of all the Boolean polynomials  $f_i$  will have the constant 0. Hence, we are looking for the indices  $x^*$  at which the logical **OR** of all the truth tables of all the  $f_i$ 's is 0. In [BCC<sup>+</sup>10], the authors use the Gray code technique to evaluate the truth table of each polynomial  $f_i$ . Gray codes are linear codes that have the property that successive codewords differ by only one bit. There are many methods of constructing such codes in literature, and one of the simplest way is to define the *i*-th code word as  $g_i = i \oplus (i \gg 1)$  (the  $\gg$  denotes the shift right operator). For example the eight 3-bit codewords listed sequentially are: 000, 001, 011, 010, 110, 111, 101, 100. Take any polynomial  $f_i$ : we want to evaluate  $f_i$  over all  $2^n$  points of its input domain. Then it is more efficient to do this evaluation in the order specified by the Gray code, i.e. first  $f_i(g_0)$ , then  $f_i(g_1), f_i(g_2)...$  etc. The reason for this is as follows: note  $f_i(g_0) = f_i(\vec{0})$  is just the constant term of  $f_i$ , thereafter if t is the only bit-position where the successive codewords  $g_j$  and  $g_{j+1}$  differ in, and we already have the value of  $f_i(g_j)$  then we can use a Taylor-like expansion formula for Boolean functions to compute  $f_i(g_{i+1})$ :

$$f_i(g_{j+1}) = f_i(g_j) \oplus \frac{\delta f_i}{\delta x_t}(g_j).$$

(1)

Here  $\frac{\delta f_i}{\delta x_t}$  is the 1st order derivative of the function  $f_i$  at the point  $x_t$ . For example if  $f_i = x_1 x_2 \oplus x_3 \oplus x_1 x_4 x_5$ , then  $\frac{\delta f_i}{\delta x_1} = x_2 \oplus x_4 x_5$  and  $\frac{\delta f_i}{\delta x_2} = x_1$ ,  $\frac{\delta f_i}{\delta x_3} = 1$  etc. It is known that the derivative has algebraic degree at least one less than the original function, and so if the derivative is not a constant or a degree one function we recursively evaluate the derivative term in Equation (1) with another round of Taylor expansion. The method obviously works best if the function  $f_i$  is quadratic, but can also be applied to evaluate moderately higher degree functions too if some of the derivatives are precomputed and stored in memory. In a follow up work [BCC<sup>+</sup>13], the same authors proposed a hardware circuit for the problem, however, for only degree 2 functions (that needed negligible amount of pre-computations).

2

Another method to compute the truth table of a Boolean polynomial from its algebraic expression is via the Möbius Transform. This method does not require pre-computations. The transform can be simply evaluated as  $\vec{v} = M_n \vec{u}$ , where  $\vec{u}$  is the  $2^n \times 1$  algebraic normal form (ANF) vector of any *n*-variable Boolean function,  $M_n$  is the  $2^n \times 2^n$  binary Möbius matrix, and  $\vec{v}$  is the truth-table of the function, with its *i*-th element being the function evaluation at the binary string representation of i. As we will soon see, a naive interpretation of this method requires time and space exponential in n to compute. However there exist more subtle methods to compute the matrix-vector product given above in polynomial space (bounded by  $n^{d+1}$  where d is the algebraic degree of the Boolean polynomial). Translating this to hardware is a non-trivial task as the underlying algorithm is significantly complex. In this paper, we will propose strategies to translate the Möbius Transform algorithm into a hardware circuit and we will demonstrate how to overcome the engineering challenges involved. We then show how multiple instances of the above Möbius Transform circuit can be efficiently used to solve or perform fast exhaustive search for roots of equation systems over GF(2) whose degree is bound by some constant d. We show that asymptotically, with silicon footprint proportional to  $m \cdot n^{d+1}$  we can describe a circuit that finds roots of a system of m polynomial equations of degree d in n unknowns over GF(2).

#### 1.2 Impact and Comparison with the state of art

Till date we are not aware of any hardware architecture that solves equations over GF(2)of degree larger than 2. This therefore presents the first instance of a solver in hardware for higher degree equation systems over GF(2). Furthermore building a truth table in hardware has many significant cryptographic applications (please see [Bou22, Section 1.3]). Very briefly, it is known that the pre-image attack [DS11] against the Hamsi-256 hash function requires the attacker to construct efficiently truth tables of degree 6 over 32 variables. The attack against the stream ciphers GEA-1/GEA-2 requires construction of degree 4 truth tables over 33 variables [BDL<sup>+</sup>21]. The cube attack on Trivium [HST<sup>+</sup>21] requires construction of such tables over upto 75 variables of degree 20. The attack against Pyjamask-96 [DRS20] also requires construction of truth tables of Boolean functions of degree 4 of around 128 variables.

#### 1.2.1 Comparison with Linearization Algorithms

Linearization based algorithms like XL [CKPS00] and Elimlin [CB07] also attempt to find the solution of a system of Boolean equations through matrix manipulation techniques like Gaussian Elimination (GE). The idea is to rewrite every higher degree monomial in the equation system as a new linear variable. This converts a system of m equations of any arbitrary algebraic degree d to a system of m linear equations in around  $O(n^d)$  extended variables. Using hardware accelerators for GE like the SMITH framework [BMP+06], one could also describe a circuit that finds roots of the system using silicon area proportional to  $m \cdot n^d$ . However, as shown in [Bar09, Section 12.3], such an approach will generate basis vectors for a space containing an exponential number of false solutions, and it is not immediately clear how efficient circuit hardware architectures can be described to eliminate them. However, note that there are papers in software like [BDT22, JV17, BFSS13, LPT<sup>+</sup>17, Din21, BKW19] which achieve this in software in less than brute force time.

#### 1.2.2 Area Time product

The Möbius Transform operation is similar to the Fast Fourier Transform (FFT) which is defined over larger rings. It is known that the if the layout of the circuit is restricted to 2

dimensions then the Area(A) and Time(T) product of the FFT is subject to a lower bound  $AT^2 \ge N^2$  (where  $N = 2^n$ ) [Tho79]. Because the circuit has to hold the N input data, this implies that  $AT \ge N^{3/2}$ . This lower-bound is based on communication complexity, i.e. the fact that "wires take space". In this paper we begin with two circuits for Möbius Transform i.e. **Expmob1/Expmob2** that take  $AT^2 = N \cdot \log(N)$  and  $N \cdot (\log(N))^2$  respectively.

Instead of optimizing AT directly, consider the case when A is bound polynomially by some  $n^{d+2}$  and T is the clock cycle count of the operation on the given circuit. It makes sense to consider this, since as n increases, it is unreasonable to expect exponential amount of silicon resources to be available for manufacturing. We could ask the question: what is the minimum value of the AT product given that  $A \in O(n^{d+2})$  and the task is to solve n equations of n variables in degree d. In fact this is the metric we look at for the various circuit architectures that we propose in the paper. In Section 5.6, we show that the minimum AT product for all the solvers that we have considered is around  $4 \cdot n^{d+2} \cdot 2^{n-\hat{h}}$ where  $\hat{h}^2 \cdot 2^{\hat{h}} = n^{d+2}$ .

#### 1.3 Contribution and Organization

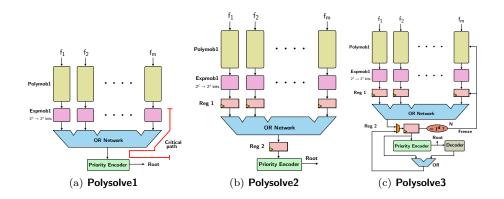

In this paper we present a novel hardware architecture for the Möbius transform for *n*-variable Boolean functions of degree  $\leq d$  that requires silicon resources that are polynomially bounded by  $n^{d+1}$ . We use the recursive definition of the transform found in [Din21, Section 4.2], and identify and solve the engineering difficulties of translating such an algorithm into hardware. Parallel instances of this architecture can be combined to construct hardware solvers that find roots of an underlying equation system over GF(2) by exhaustive search. We describe the architectures of three such solvers the last of which is able to find all roots of any system of *m* Boolean equations in *n* unknowns and algebraic degree *d* in circuit area proportional to  $m \cdot n^{d+1}$  and circuit depth proportional to  $2 \cdot \log_2(n-d)$  units.

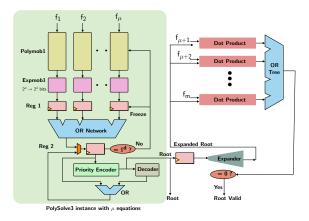

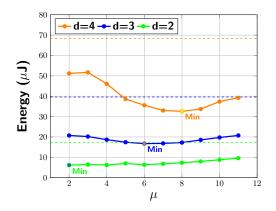

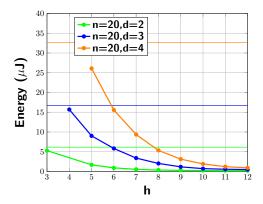

In the next part of the paper we address the issue of energy efficiency. Given an equation system with m equations, performing m Möbius computations leads to a lot of redundant computation and thus wastage of computational effort and energy. We introduce a solver architecture called **Polysolve4**, that aims to minimize these redundant computations. We first use the Möbius Transform circuit to extract the roots of some  $\mu < m$  equations of the system. Assuming that this solution space is small enough we try to individually evaluate the remaining  $m - \mu$  equations at the all the vectors of this reduced space. Then we try to construct **Polysolve4** circuits with Möbius Transform circuits that are height bound. We explain the concept of height bound circuits. We then show that (for solving 20 quartic equations in 20 variables) these circuits can obtain around 100 times energy efficiency when compared to the **Polysolve3** circuit.

The rest of the paper is organized in the following manner. Section 2 presents some preliminary lemmas and definitions in this field. In Section 3 we look at the recursive definition of Möbius transform and we explain in detail how the hardware circuit for the same is designed. In Section 4, we first show how to combine multiple instances of the Möbius Transform circuit that produces a solver that finds at least one root of the underlying equation system. We then list two variants of this architecture, the last of which is able to find all the roots of the equation system. Section 5 describes the solver **Polysolve4** and analyzes of energy consumption of the circuit as a function of the internal parameter  $\mu$  of the circuit. We further look at depth-bound Möbius Transform circuits that enable use to find better energy/time consumption figures. Section 6 concludes the paper.

#### 1.3.1 Notations:

Note that henceforth in the paper T will denote the number of clock cycles required to complete any operation. This value of T is considered for all the AT metric optimizations

throughout the paper. Simultaneously we use the notations  $T_{min}$ ,  $T_{cr}$ ,  $T_d$  at multiple points in the paper. All these symbols denote some physical time parameter associated with the circuit and will be made clear when they appear. As such they are measured in **ns** or similar denominations.

## 2 Definitions and Preliminaries

**Boolean function**: An *n*-variable Boolean function is a map from  $\{0, 1\}^n \to \{0, 1\}$  and it can be uniquely represented by its algebraic expression, called algebraic normal form or ANF. The algebraic expression of such a function using the  $(\oplus, \cdot)$  basis can be written as

$$f(\vec{x}) = f(x_0, x_1, \dots, x_{n-1}) = \bigoplus_{i \in \{0,1\}^n} a_i x^i$$

Here  $i := i_0 i_1 \cdots i_{n-1}$  is the binary string of length n, with  $i_j$  as the individual bits and  $x^i$  is defined as  $\prod x_j^{i_j}$ . The ANF vector  $\vec{u} = [a_0, a_1, \ldots, a_{2^n-1}]$  is defined as the  $2^n$ -length string of all the  $a_i$ 's.

**Example 1.** For example, consider the 3-variable function  $f = 1 \oplus x_0 x_1 \oplus x_2 \oplus x_0 x_2$ . We can write this as  $x_0^0 x_1^0 x_2^0 \oplus x_0^1 x_1^1 x_2^0 \oplus x_0^0 x_1^0 x_2^1 \oplus x_0^1 x_1^0 x_2^1$ . The function can be expressed as a length 8 bit-vector  $\vec{u}$  with bits at locations given by the binary strings 000, 110, 001 and 101 i.e. 0, 6, 1 and 5 set to 1 and the rest of the bits 0, which is to say that  $a_0 = a_1 = a_5 = a_6 = 1$  and the rest of the  $a_i = 0$ .

The algebraic degree of the function (provided the function is not identically null) is defined as the maximum hamming weight of the string *i* such that  $a_i = 1$ . Thus in the previous example, the algebraic degree is 2. For functions having degree *d*, all the coefficients  $a_i$  such that hw(i) > d are naturally 0. Since there are exactly  $\binom{n}{i}$  length *n* strings of hamming weight *i*, we can see that the ANF of degree *d* function can be expressed using  $\binom{n}{\downarrow d} := \sum_{i=0}^{d} \binom{n}{i} < n^d$  binary coefficients.

**Truth Table**: The vector of evaluations of a Boolean function at all its input points is called its **Truth Table** (therefore this is a  $2^n$  length vector). The ANF and the Truth table vectors of any Boolean function are closely related by the Möbius transform. Let  $\vec{v} = [v_0, v_1, \ldots, v_{2^n-1}]$  be the truth-table of the function f, with its *i*-th element being the function evaluation at the binary string representation of i, i.e.  $v_i = f(i_0, i_1, \ldots, i_{n-1})$ . then it is well known that  $\vec{v}$ ,  $\vec{u}$  are related as  $\vec{v} = M_n \cdot \vec{u}$ , where  $M_n$  is the Möbius matrix of size  $2^n \times 2^n$ . The i, j-th element of this matrix  $m_{ij}$  is given as

$$m_{ij} = 1$$

if  $j \leq i$  and 0 otherwise.

The operator  $\leq$  is a partial order over all binary strings: we say that  $j \leq i$  if the binary string representing j is less than or equal to the binary string representing i in all indices. For example,  $4 \leq 5$ , since 100 is less than 101 at all bit-locations, but  $3 \not\leq 4$  since 011 exceeds 100 in the last 2 bit-locations.

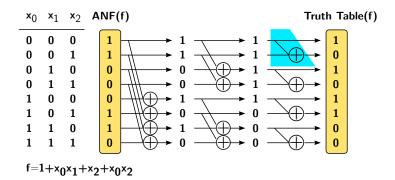

The Möbius matrix  $M_n$  has been widely studied in literature: for example it is well known that is lower-triangular and involutive i.e.  $M_n^{-1} = M_n$ . Thus both  $\vec{v} = M_n \cdot \vec{u}$  and  $\vec{u} = M_n \cdot \vec{v}$  hold. An example of the  $8 \times 8$  Möbius matrix  $M_3$ , i.e. for n = 3 is shown in Figure 1. This helps us see an alternative recursive definition of  $M_n$ . If we define  $M_1 = \begin{bmatrix} 1 & 0 \\ 1 & 1 \end{bmatrix}$ , then for all n > 1, we have  $M_n = M_1 \otimes M_{n-1}$ , where  $\otimes$  is the matrix tensor product.

Multiplication of a vector by this matrix can be quickly executed by the butterflylike operations shown in Figure 2. The butterfly operation shaded in blue is actually

$$M_{3} = \begin{bmatrix} 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 1 & 1 & 0 & 0 & 0 & 0 & 0 & 0 \\ 1 & 0 & 1 & 0 & 0 & 0 & 0 & 0 \\ 1 & 1 & 1 & 1 & 0 & 0 & 0 & 0 \\ 1 & 0 & 0 & 0 & 1 & 0 & 0 & 0 \\ 1 & 1 & 0 & 0 & 1 & 1 & 0 & 0 \\ 1 & 0 & 1 & 0 & 1 & 0 & 1 & 0 \\ 1 & 1 & 1 & 1 & 1 & 1 & 1 & 1 \end{bmatrix}$$

Figure 1: An example of the Möbius matrix M for n = 3

multiplication of the input 2-bit vector by the matrix  $M_1$ . The figure tells us that for an *n*-variable function, the algorithm can be done in-place (without any additional memory) using around  $n \cdot 2^{n-1}$  xor operations and  $2^n$  space.

### 3 Implementing the Möbius Transform

Given Figure 2, we can think of many strategies to implement the basic transform if one has access to exponential silicon resources. The operation consists of n stages of sequential xor layers, with each layer having exactly  $2^{n-1}$  xor operations over bits. Given this, one can think of several circuit strategies to implement this:

- **Expmob1** This architecture implements the circuit in Figure 2 as a single unrolled circuit, i.e. it implements all the *n* butterfly stages as dedicated circuits sequentially. Consider **one**<sub>i</sub>(x) :  $\{0,1\}^{n-1} \rightarrow \{0,1\}^n$  to be the function that inserts a 1 in the *i*-th MSB position of x, and **zero**<sub>i</sub>(x) to be a function that inserts a 0 in the same position, i.e. **one**<sub>0</sub>(1001) = 1 1101 and **zero**<sub>0</sub>(1001) = 0 1001 etc. Note that there are a total of  $2^{n-1}$  butterfly operations in each of the *n* stages. In the *i*-th stage (for  $0 \le i \le n-1$ ), the *j*-th butterfly takes as input the bits in the position **zero**<sub>i</sub>(j) and **one**<sub>i</sub>(j) for all  $0 \le j \le 2^{n-1} 1$ . This requires a total of  $n \cdot 2^{n-1}$  number of 2-input xor gates in total. However such a circuit is able to compute the transformation in a single cycle.

- **Expmob2** This configuration is slightly different from the previous circuit, in the sense that we have only a single stage butterfly which we operate over n clock cycles to compute the transform, i.e. similar to round based circuits of block ciphers in which a single round function circuit is iterated over a given number of cycles to compute the transform. Unlike the round function of a block cipher the successive stages

Figure 2: Möbius transform on  $f = 1 \oplus x_0 x_1 \oplus x_2 \oplus x_0 x_2$ . The blue shaded component represents one butterfly unit.

of xor layers are not exactly similar. For example, consider the topmost butterfly circuit in each stage in Figure 2. The 1st stage takes bits at positions 0 and 4 as input, the second stage takes bits 0 and 2, the third stage takes bits 0 and 1 and so on. So to create a round based circuit, it would seem that one would need multiple n to 1 multiplexers before each of the butterfly circuits. However this can be avoided using a simple observation. Consider  $\pi_n$  to be the following permutation:

$$\pi_n(2x) = x$$

, and  $\pi_n(2x+1) = 2^{n-1} + x$  for all  $0 \le x < 2^{n-1}$

The idea is that after the given stage of butterfly circuits, the bit at position i be shifted to position  $\pi_n(i)$ . Such a permutation over the bits requires only re-routing of wires and thus no additional silicon area. This is essentially the entire round function circuit which has to be executed for a total of n cycles for the transform to be computed. To see why this works, consider the following facts. Let  $B_n$  be the block diagonal matrix defined as  $B_n = M_1 \otimes I_{n-1}$ , where  $I_{n-1}$  is the identity matrix of size  $2^{n-1} \times 2^{n-1}$ . Note that  $B_n$  is transformation defined by the first stage of butterfly layer in Figure 2. Let  $P_n$  be the permutation matrix corresponding to  $\pi_n$ . Then it is easy to verify that the Möbius matrix  $M_n = (P_n \cdot B_n)^n$ .

#### 3.1 Synthesis Results

In this section we will describe the flow of simulation followed for each of the circuits reported in the paper. The design was described at the RTL level using a hardware description language and functional correctness was first verified. Thereafter the circuit was synthesized using the Nangate 15nm Open Cell Library [MMR<sup>+</sup>15] using *Synyopsys Design Vision*, mainly to ensure that the results obtained can be reproduced readily. One of the possible uses of the Möbius Transform, is in solving equation systems. In order to ensure that equations are solved as quickly as possible, the circuit compiler was instructed to specifically optimize the total critical path of the circuit. A timing analysis is then performed on the synthesized netlist using sufficient number of randomly generated test vectors, which outputs the switching statistic of every node in the circuit. This information is used by a power compiler software to estimate the average power consumed by the circuit. Energy is computed as the product of the average power and the total physical time taken for the circuit to execute a given operation.

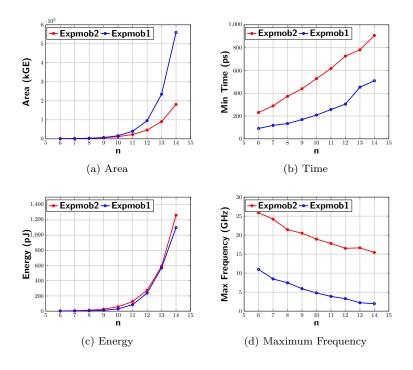

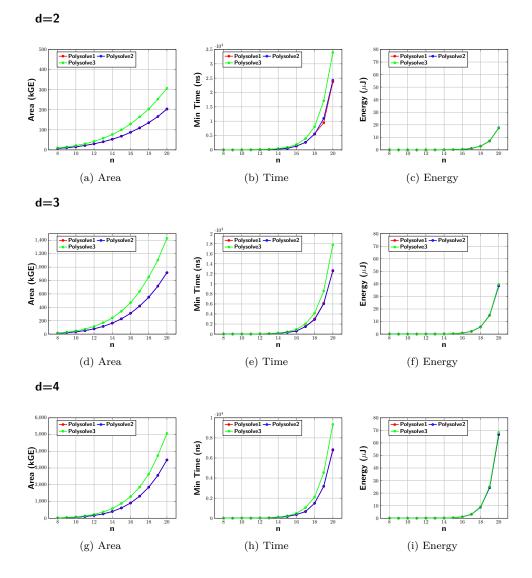

In Figure 3, we present synthesis results for the circuits **Expmob1** and **Expmob2**. It can be seen that **Expmob1** performs better than **Expmob2** in this regard, most probably due to the fact that additional hold/setup time constraints need to be met for **Expmob2** for writing on to the register in each cycle. Similarly the additional energy required for the *n* successive register writes makes **Expmob2** less energy efficient as compared to **Expmob1** as shown in Figure. Detailed results are shown in Table 7 in Appendix D.

However both these circuits require exponential amount of logic gates which starts to become a bottleneck as n increases. We have already seen that a degree d Boolean function can be represented with only  $\binom{n}{\downarrow d} < n^d$  binary coefficients, which means that for small values of d the size of the ANF vector is polynomially bounded. Thus the size of the register that holds the ANF can be bounded by  $n^d$ . However, it is not possible to use **Expmob1/Expmob2** circuit to compute the transform on this reduced size register, since, although the initial ANF vector is small, the output of each layer of butterflies are progressively larger till it reaches  $2^n$  (which is the expected size of the truth table) after the last stage.

#### 3.2 Recursive Algorithm for Möbius transform

There exists algorithms that perform the basic transform (on functions limited to degree d) using polynomial space only, i.e. bounded by  $n^{d+1}$ . We state the algorithm appearing in

Figure 3: Synthesis results for **Expmob1** and **Expmob2** circuits. Energy measured at 1GHz

[Din21, Section 4.3]. The algorithm requires a notional depth-first traversal in a transition graph as shall be explained shortly.

The principal question is how do we circumvent the fact that even if we begin with a ANF vector of size that is polynomially bounded, each butterfly stage is likely to produce an output that is of size larger than the input.

**Example 2.** First let us make the following observation taking Figure 2 as a reference: consider the initial ANF vector  $A_0 = [1100 \ 0110]$  and the vector  $A_1 = [1100 \ 1010]$  just after the first layer. The initial vector corresponds to the function

$$f(x_0, x_1, x_2) = 1 \oplus x_0 x_1 \oplus x_2 \oplus x_0 x_2 = x_0 \cdot (x_1 \oplus x_2) \oplus (1 \oplus x_2)$$

=  $x_0 \cdot [f(1, x_1, x_2) \oplus f(0, x_1, x_2)] \oplus f(0, x_1, x_2)$

Note that  $[f(1, x_1, x_2) \oplus f(0, x_1, x_2)] := \frac{\delta f}{\delta x_0}$  is simply the derivative of f at the coordinate  $x_0$ . Both  $\frac{\delta f}{\delta x_0}$  and  $f(0, x_1, x_2)$  have number of variables which is 1 less than the original function, and it is obvious that both their algebraic degrees can not be more than that of the original function.

Now consider the vectors in the top and bottom halves of  $A_1$  i.e.  $A_{top} = [1100]$  and  $A_{bottom} = [1010]$ . It is easy to observe/verify the following:

- **A:**  $A_{top}$  is the ANF vector for  $f(0, x_1, x_2)$  (in this case  $1 \oplus x_2$ ) and  $A_{bottom}$  is the ANF vector for  $f(1, x_1, x_2)$  (in this case  $1 \oplus x_1$ ).

- **B:** Both  $A_{top}/A_{bottom}$  are outputs of the butterfly layer in which the input is  $A_0$ . Whereas  $A_{top}$  is the arm of the butterfly that does not require xor computations, some xor computations are required for  $A_{bottom}$ .

**C:** The remaining steps from the 2nd stage onward can be seen as the parallel application of the Möbius Transform on the reduced variable Boolean functions  $f(0, x_1, x_2)$  and  $f(1, x_1, x_2)$

Of course in the figure, both the transforms are computed parallelly, which requires  $2^{n-1}$  space each and so the total space requirement is  $2^n$  which is the same as the original. The idea behind the recursive transform is to do these 2 sub-transforms sequentially, i.e. one after the other so that the same space (i.e. register locations) can be used for both the transforms so that the cumulative space requirement does not add up. Let us state the algorithm now formally (Algorithm 1). The algorithm is parameterized by two quantities: number of variables n, and the maximum algebraic degree d that the underlying function can have.

| Algorithm 1: Recursive Möbius Transform                                     |

|-----------------------------------------------------------------------------|

| Möbius $(A_0, n, d)$                                                        |

| <b>Input:</b> $A_0$ : The compressed ANF vector of a Boolean function $f$   |

| <b>Input:</b> <i>n</i> : Number of variables, <i>d</i> : Algebraic degree   |

| <b>Output:</b> The Truth table of $f$                                       |

|                                                                             |

| <pre>/* Final recursion step, i.e. leaf nodes of recursion tree */</pre>    |

| $\mathbf{if} \ n{=}d \ \mathbf{then}$                                       |

| Use the formula $B = M_n \cdot A_0$ to output partial truth table B.        |

| <pre>/* Use either Expmob1/Expmob2 to do this */</pre>                      |

| end                                                                         |

| else                                                                        |

| Declare an array T of size $\binom{n-1}{d}$ bits.                           |

| /* Now we compute the 2 operations of the butterfly layer */                |

| 1 Store 1st butterfly output i.e. $A_{top}$ in T (requires no xors).        |

| Call Möbius $(T, n - 1, d)$                                                 |

| 2 Store 2nd butterfly output i.e. $A_{bottom}$ in $T$ (requires some xors). |

| Call Möbius $(T, n-1, d)$                                                   |

| end                                                                         |

For the sake of simplicity, we have excluded many operational details in the above algorithm to give the reader a better idea of the flow of the algorithm. The space requirement of this algorithm is easy to estimate from the algorithm description. We start out with  $\binom{n}{\downarrow d}$  coefficients required to store  $A_0$ . Thereafter every successive *i*-th recursion stage requires  $\binom{n-i}{\downarrow d}$  additional memory for all  $1 \le i \le n - d$ . The final stage can use **Expmob1/Expmob2** to perform Möbius Transform in-place and no additional memory is required. However in our experiments we preferred to use **Expmob1** because it is slightly faster. Hence the total space requirement of this procedure is given by (for a proof of the following please see Appendix B):

$$S(n,d) = \sum_{i=0}^{n-d} \binom{n-i}{\downarrow d} \in O(n^{d+1}).$$

$$\tag{2}$$

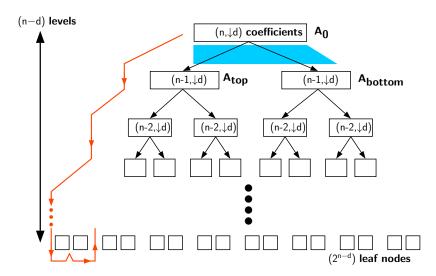

Notionally speaking the algorithm listed above describes a depth first recursion tree as shown in Figure 4, where each node in tree are connected to its two butterfly outputs. The depth first nature of the structure gives rise to complications even while implementing it in software. The problem with implementing such a routine, even in software, is the high number of context switches, that is needed to traverse one level down. In layman's terms, before we can do a downward dive in the tree, the current state information, variables etc has to be stored in a separate memory location (usually denoted as "call-stack"). This costs time/energy and makes the algorithm less attractive from a practical point of view.

Figure 4: Recursion tree for the Möbius Transform algorithm. The blue shaded component roughly represents one arm of the butterfly unit. Note here  $(x, \downarrow d) := \begin{pmatrix} x \\ \downarrow d \end{pmatrix}$ .

### 3.3 Hardware circuit Polymob1

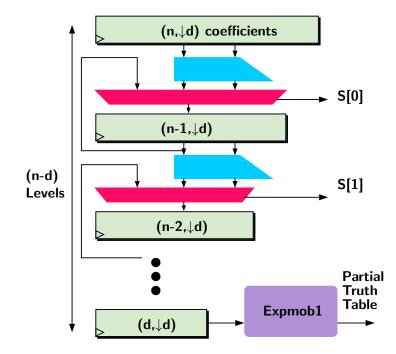

The goal obviously is to construct a circuit that does not take more than a total of S(n, d) bits of register space. As such we are looking at a circuit architecture similar to the one shown in Figure 5.

To understand the challenges in this circuit, note that one needs to follow the flow given by the orange line in the recursion tree in Figure 4. Now there is one top-level register of size  $\binom{n}{\downarrow d}$  storing the initial ANF vector  $A_0$ . There is only one  $\binom{n-1}{\downarrow d}$  size register to store the second level coefficients  $A_{top}$  and  $A_{bottom}$ . This implies that if in the first clock cycle the 2nd register stores  $A_{top}$ , it must preserve this state till the entire left sub-tree rooted at this node is executed before it overwrites its state to  $A_{bottom}$ . Similarly there is only one  $\binom{n-2}{\downarrow d}$  register to store potentially four ANF vectors (two each from the butterfly operation on  $A_{top}$  and  $A_{bottom}$ ). Thus the engineering challenge is to ensure that each register at the successive levels store and preserve appropriate state vectors till it is time to overwrite them, and so this in a manner that minimizes the total number of clock cycles required to execute the Möbius Transform.

Thus we arrive at the architecture in Figure 5. Each *i*-th level has a single register of size  $\binom{n-i}{\downarrow d}$  (for  $0 \le i \le n-d$ ), and from i = 1 onwards each register is preceded by a 3:1 multiplexer of size  $\binom{n-i}{\downarrow d}$ . This is because each register must be able to accept 3 different inputs:

- 1. Its own output state, or in other words it must be able to preserve its state.

- 2. Either of the 2 outputs of the butterfly stage preceding it.

#### 3.3.1 Architectural Details:

We begin by noting that a 3:1 multiplexer is not necessary for the above architecture unless we add other functionalities to the circuit like the one described in Section 4.3. For executing the basic Möbius Transform a 2:1 multiplexer will also serve the purpose. We explain this with the first couple of registers but the same principle holds for the registers in the lower levels too. Note that the second register in its lifetime can only store two vector values  $A_{top}$  and  $A_{bottom}$  depending on how far the execution has reached in the

Figure 5: Hardware architecture **Polymob1** for the Möbius Transform algorithm. The blue shaded part roughly represents one arm of the butterfly unit. Note here  $(x, \downarrow d) := \begin{pmatrix} x \\ \downarrow d \end{pmatrix}$ .

process of the traversal of the recursion tree. Both of these are obtained from the butterfly operation on  $A_0$  which resides on the register at the level just above. Thus the idea is to have a single 2:1 multiplexer separating the two registers, which takes as input the two outputs of the butterfly operation. When the 2nd level register would need to preserve state ( $A_{top}$  or  $A_{bottom}$ ), it can be done by appropriately setting the select signal of the multiplexer: for example to preserve  $A_{bottom}$  we just need to set the select signal of the preceding mux so that it accepts the  $A_{bottom}$  signal from the previous butterfly stage.

It remains to be seen how one can effectively set the multiplexer signals. In order to do that let us try to observe a small example. We will make use of a more general notation for the successive ANF vectors instead of just  $A_{top}/A_{bottom}$ , since we have to accommodate ANFs at different levels. We use the notation  $A[\ell]_b$  to denote the ANF vector at some level of the recursion tree: the  $\ell$  term in the square braces denotes the level of the ANF vector in the recursion tree, and the term b which can be seen as a binary string or integer contains information about the coordinates over which the derivatives have been computed to obtain the function.

**Example 3.** For example, take the case when n = 5, d = 2. The ANF of original function  $f(x_0, x_1, x_2, x_3, x_4)$ , we denote by the notation  $A[0]_{000}$ : note that the subscript is a binary string of length n - d (which is 3 in this example). This is because there are n - d levels in the recursion tree, each obtained by taking derivative over some co-ordinate variable. The level 1 ANFs corresponding to the functions  $f(0, x_1, x_2, x_3, x_4)$  and  $\frac{\delta f}{\delta x_0} = f(0, x_1, x_2, x_3, x_4) \oplus f(1, x_1, x_2, x_3, x_4)$  are denoted by  $A[1]_{000}$  and  $A[1]_{100}$  respectively (thus  $A_{\text{top}}$  and  $A_{\text{bottom}}$  defined earlier are equal to  $A[1]_{000}$  and  $A[1]_{100}$  respectively in this new notation). Similarly the two level 2 functions obtained by applying the butterfly layer on  $A[1]_{000}$  (by taking derivative over  $x_1$ ) are denoted as  $A[2]_{000}$  and  $A[2]_{010}$ . Similarly butterfly over  $A[1]_{100}$  yields the two vectors  $A[2]_{100}$  and  $A[2]_{110}$ .

Generalizing this: if  $A[\ell]_b$  is the ANF vector at some level  $\ell$  of the tree, then after applying the butterfly over the coordinate  $x_\ell$ , the two output vectors are denoted as

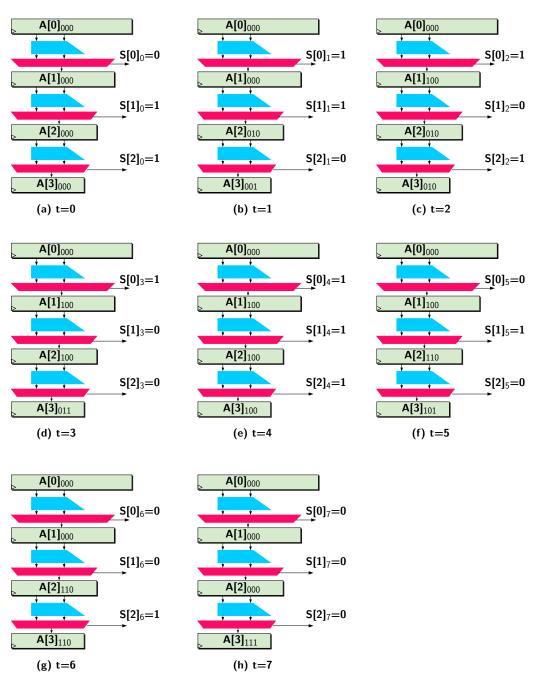

$A[\ell+1]_b$  and  $A[\ell+1]_{b\oplus e_\ell}$ , where  $e_t$  is the unit vector of length n-d with 1 at the *t*-th position, eg.  $e_0 = 100 \dots 0, e_1 = 010 \dots 0$  etc. At this moment, let us turn towards the example in Figure 6, where we have manipulated the select signals of each multiplexer so that the entire Möbius Transform is computed in  $2^{n-d} = 8$  cycles, i.e. in each of the 8 cycles we get one partial truth table of size  $\binom{d}{\downarrow d} = 2^d = 4$ . Initially the top-level register would be initialized with  $A[0]_{000}$  and the remaining registers would stay uninitialized. In the 2 cycles following this, the select signals of each multiplexer, is set to zero so that, after this each level  $\ell$  register contains  $A[\ell]_{000}$ . Figure 6 shows us the flow of data in each of the 8 cycles succeeding this.

We introduce an additional notation: let  $S[\ell]_t$  be the select signal of the multiplexer between the registers at levels  $\ell$  and  $\ell + 1$  at time t. Which is to say that if  $S[\ell]_t = 0$  and the ANF vector at level  $\ell$  at time t is  $A[\ell]_b$ , then at time t + 1, the ANF vector at level  $\ell + 1$  is  $A[\ell + 1]_b$ , and if  $S[\ell]_t = 1$  then the corresponding vector is  $A[\ell + 1]_{b \oplus e_\ell}$  (this can also be written as  $A[\ell+1]_{b+e_{\ell}}$  since by design the coordinates of b at positions larger than  $\ell$  are all 0). The two expressions can obviously be combined to give the single compact expression  $A[\ell+1]_{b+S[\ell]_t \cdot e_\ell}$  that caters for both values of  $S[\ell]_t$ . In Figure 6, we have done a series of assignments to the variables  $S[\ell]_t$  (for  $0 \le \ell < n-d$  and  $0 \le t < 2^{n-d} - 1$ ) so that the vector at the bottommost level of the register chain is always  $A[n-d]_t$  for all  $0 \le t < 2^{n-d}$ . Since **Expmob1** is connected to the bottommost register, this ensures that the all the partial truth tables are faithfully computed and the circuit indeed computes the Möbius Transform of any five variable Boolean function of degree up to 2. However we are more interested in engineering the multiplexer signals for general values of n, d. To do so, equivalently consider the subscripts of the ANF vectors as integers, and return to the example in Figure 6. Initially all the subscripts at all the levels are zeros: thereafter we have the following subscripts assuming that all the  $S[\ell]_t$ 's are unknowns.

| t | $\ell = 0$ | $\ell = 1$       | $\ell = 2$                        | $\ell = 3$                                 |

|---|------------|------------------|-----------------------------------|--------------------------------------------|

| 0 | 0          | 0                | 0                                 | 0                                          |

| 1 | 0          | $4 \cdot S[0]_0$ | $2 \cdot S[1]_0$                  | $S[2]_{0}$                                 |

| 2 | 0          | $4 \cdot S[0]_1$ | $4 \cdot S[0]_0 + 2 \cdot S[1]_1$ | $2 \cdot S[1]_0 + S[2]_1$                  |

| 3 | 0          | $4 \cdot S[0]_2$ | $4 \cdot S[0]_1 + 2 \cdot S[1]_2$ | $4 \cdot S[0]_0 + 2 \cdot S[1]_1 + S[2]_2$ |

| 4 | 0          | $4 \cdot S[0]_3$ | $4 \cdot S[0]_2 + 2 \cdot S[1]_3$ | $4 \cdot S[0]_1 + 2 \cdot S[1]_2 + S[2]_3$ |

| 5 | 0          | $4 \cdot S[0]_4$ | $4 \cdot S[0]_3 + 2 \cdot S[1]_4$ | $4 \cdot S[0]_2 + 2 \cdot S[1]_3 + S[2]_4$ |

| 6 | 0          | $4 \cdot S[0]_5$ | $4 \cdot S[0]_4 + 2 \cdot S[1]_5$ | $4 \cdot S[0]_3 + 2 \cdot S[1]_4 + S[2]_5$ |

| 7 | 0          | $4 \cdot S[0]_6$ | $4 \cdot S[0]_5 + 2 \cdot S[1]_6$ | $4 \cdot S[0]_4 + 2 \cdot S[1]_5 + S[2]_6$ |

Table 1: An example table of the subscripts at al levels, with respect to time.

Note that the above follows since  $e_{\ell} = 2^{n-d-1-\ell}$  as an integer, and therefore  $b + S[\ell]_t \cdot e_{\ell} = b + S[\ell]_t \cdot 2^{n-d-1-\ell}$ . We have already seen that for this to serve our purpose, the integer values of the last column of the above table should be 0 to 7. In other words we need  $S[\ell]_t$ 's from the set  $\{0, 1\}$  which are solutions of the following system of equations over the integers.

$$\begin{split} S[2]_0 &= 1\\ 2 \cdot S[1]_0 + S[2]_1 &= 2\\ 4 \cdot S[0]_0 + 2 \cdot S[1]_1 + S[2]_2 &= 3\\ 4 \cdot S[0]_1 + 2 \cdot S[1]_2 + S[2]_3 &= 4\\ 4 \cdot S[0]_2 + 2 \cdot S[1]_3 + S[2]_4 &= 5\\ 4 \cdot S[0]_3 + 2 \cdot S[1]_4 + S[2]_5 &= 6\\ 4 \cdot S[0]_4 + 2 \cdot S[1]_5 + S[2]_6 &= 7 \end{split}$$

Figure 6: Dataflow for the first 8 cycles.

It can be verified that the assignments to the  $S[\ell]_t$ 's in Figure 6 satisfy the above equation system. We address the issue of the general case with the following theorem.

**Theorem 1.** Given the circuit **Polymob1** in Figure 5, in which each of the registers have been initialized with the ANF vectors  $A[\ell]_{0^{n-d}}$  for all  $0 \le \ell \le n-d$  of an n-variable Boolean function f of degree less than or equal to d. Then it is possible to design the multiplexer signals  $S[\ell]_t$  for  $0 \le t \le 2^{n-d} - 2$  using logic gates efficiently, so that the circuit computes the Möbius Transform of f in exactly  $2^{n-d}$  clock cycles.

*Proof.* We essentially have to prove that we can engineer the multiplexer signals  $S[\ell]_t$  efficiently so that the subscripts of the ANF vectors at the bottommost i.e. level n - d, at  $t = 0 \rightarrow 2^{n-d} - 1$  are each equal to t itself. Generalizing the observations made above, we need  $S[\ell]_t$ 's from the set  $\{0, 1\}$  which are solutions of the following system of equations over the integers. Let u := n - d. Let i be a sequence variable and set j := u - 1 - i for conciseness, then we have

|                                                |                                                 |                        |                                                                         | $2\!\cdot\!S[u\!-\!2]_0$ | $S[u-1]_0 + S[u-1]_1$            | = 1 = 2.                                                            |

|------------------------------------------------|-------------------------------------------------|------------------------|-------------------------------------------------------------------------|--------------------------|----------------------------------|---------------------------------------------------------------------|

|                                                |                                                 |                        | $2^i \cdot S[j]_0$                                                      | + ···                    | $+ S[u-1]_i$                     | $\stackrel{\cdot}{=} i+1$                                           |

| $2^{u-1} \cdot S[0]_0 \\ 2^{u-1} \cdot S[0]_1$ | $+ 2^{u-2} \cdot S[1]_1 + 2^{u-2} \cdot S[1]_2$ | + · · · +<br>+ · · · + | $\begin{array}{c}2^{i}\cdot S[j]_{j}\\2^{i}\cdot S[j]_{j+1}\end{array}$ | +<br>+                   | + $S[u-1]_{u-1}$<br>+ $S[u-1]_u$ | $ \begin{array}{l} \vdots \\ = u \\ = u + 1 \\ \vdots \end{array} $ |

| $2^{u-1} \cdot S[0]_{2^u-u-1}$                 | $+ 2^{u-2} \cdot S[1]_{2^{u-u}}$                | + · · · +              | $2^i \cdot S[j]_{-i+2^u-2}$                                             | + ···                    | $+ S[u-1]_{2^{u}-2}$             | :<br>= $2^u - 1$                                                    |

To solve the above equation system, observe that the right side always has a *u*-bit integer i.e. between 1 and  $2^u - 1$ . Not only that, the left side of each equation resembles the decimal expansion of a *u*-bit binary string. For example the LHS of the last equation is the decimal expansion of the *u*-bit binary string  $S[0]_{2^u-u-1}$ ,  $S[1]_{2^u-u}$ ,  $\cdots$ ,  $S[u-1]_{2^u-2}$ . Thus a trivial way to solve the above equation system is to assign to the unknowns the values obtained from the binary representation of the corresponding integer in the right side. For example, since the binary form of  $2^u - 1$  is the *u*-bit string of all 1s we can assign  $S[0]_{2^u-u-1} = S[1]_{2^u-u} = \cdots = S[u-1]_{2^u-2} = 1$ .

Thus we can see that a solution to the above equation system exists: however we will further show that each of the signals  $S[\ell]_t$  can be efficiently generated using a reasonable amount of logic circuits. Using the method outlined above, we can immediately see that  $S[u-1]_t = t + 1 \mod 2$  for all t. With some misuse of notation the above can be written as **NOT** (t mod 2), i.e. if we have a decimal up-counter implementing t, then the  $S[u-1]_t$  signal can be implemented by inverting the least significant bit of t. Similarly the sequence  $S[u-2]_t$ ,  $t = 0, 1, 2, \ldots$  is the second lsb of the sequence  $2, 3, 4, \ldots$ , i.e. the second lsb of t + 2. For the general case, let us look at the *i*-th column from the end of the above equation system which has been highlighted in green. It can be seen that the sequence  $S[j]_t = S[u-1-i]_t$ ,  $t = 0, 1, 2, \ldots$  is the *i*+1-th lsb of the sequence  $(i+1), (i+2), (i+3), \ldots$ , i.e. the (i + 1)-th lsb of t + i + 1. Thus to construct all the signals  $S[\ell]_t$  all we need are the following circuit elements:

- 1. A u-bit decimal up-counter for the variable t.

- 2. A series of u incrementers (i.e. add by 1 circuits) to generate  $t + 1, t + 2, \ldots, t + u$ .

This proves the theorem statement.

**Theorem 2.** Furthermore it is possible to design a control circuit that generates all the select signals of the multiplexers in the **Polymob1** circuit, incurring a total delay of  $2\log_2(n-d)$  gates.

*Proof.* As noted in the proof of Theorem 1, the control circuit consists of a u-bit decimal up-counter (where u := n - d) for the variable t and a series of u incrementers. However constructing the whole incrementer leads to a wastage of gates since we are only interested in generating the (i + 1)-th lsb of t + i + 1 for  $i = 0, 1 \dots, u - 1$ .

Consider any *p*-bit string  $\vec{w} = w_{p-1}, w_{p-2}, \ldots, w_1, w_0$  (note that the indexing with starts from right side in this definition). Define the *p*-variable Boolean function  $g_{p,\vec{w}}$  as follows

$$g_{p,\vec{w}} = \begin{cases} \prod_{w_i=0} \left[ x_i \lor \bigvee_{j=i+1:w_j=1}^{p-1} x_j \right] \\ 1, \text{ when } p = 0 \text{ or } \vec{w} = 1^p. \end{cases}$$

For example the function  $g_{8,\ 0001\ 0100} = (x_0 \lor x_2 \lor x_4) \cdot (x_1 \lor x_2 \lor x_4) \cdot (x_3 \lor x_4) \cdot x_5 \cdot x_6 \cdot x_7$ and  $g_{3,111} = 1$ . Each product term begins with a min index that has 0 in the sting  $\vec{w}$ . In the first example, in  $\vec{w}$  indices 0,1,3,5,6,7 have 0. Then each min index is **OR**ed with indices larger than it that have 1 in  $\vec{w}$ . Further, if the length of  $\vec{w}$  is more than p, we truncate  $\vec{w}$  to its p least significant bits. We will prove that the (i+1)-th lsb of x+i+1 is given by the Boolean function  $x_i \oplus g_{i,bin_i(i)}$ , where  $bin_i(i)$  is the binary encoding of i using i bits, i.e. prepended with leading zeros when necessary. For small i, this is easy to verify. Denoting  $x_j$  as the Boolean variable for the j-th bit of x, we know that for i = 0, the 1st lsb of x + 1 is given by  $x_0 \oplus 1 = x_0 \oplus g_{0,0}$ . For i = 1, the 2nd lsb of x + 2 can be computed thus: when we add with 2, i.e. the string "10" the 1st lsb location generates no carry. The result of addition in the 2nd lsb location is therefore  $x_1 \oplus 1 \oplus 0 = 1 \oplus x_1 = x_1 \oplus g_{1,1}$ .

For general values of *i*, we proceed as follows. Let  $bin_i(i) = c_{i-1}, c_{i-2}, \ldots, c_0$ , where each  $c_j \in \{0, 1\}$ . Of these let the locations  $0 \le n_1 < n_2 < \cdots < n_s \le i - 1$  be such that  $c_{n_k} = 1$  for k = 1 to *s*, and the remaining  $c_j$ 's be 0. When adding two strings *a*, *b*, the carry out bit in the *j*-th position can be written as  $maj(a_j, b_j, carry_{j-1})$  (where maj is the majority function). We use two properties of this function: (1) maj(x, y, 0) = xyand (2)  $maj(x, y, 1) = x \lor y$ . Figure 7 visually represents the process of addition by the constant i + 1. Using the above property of the majority function, the figure becomes self explanatory: however we still have to explain the symbols  $z_j$  for j = 1 to *s*, which are the carry-outs for the position  $n_j$ . By using the second property, we have

$$z_1 = x_{n_1} \vee \prod_{k=0}^{n_1-1} x_k = \prod_{k=0}^{n_1-1} (x_{n_1} \vee x_k) = g_{n_1,i}(x)$$

The above follows because of the Boolean identity  $A \vee BC = (A \vee B)(A \vee C)$ , and *i* in the subscript of *g* is the truncation of  $bin_i(i)$  to the appropriate number of bits. Following the same logic we now have

$$z_{2} = x_{n_{2}} \vee \left(z_{1} \cdot \prod_{k=n_{1}+1}^{n_{2}-1} x_{k}\right)$$

=  $(x_{n_{2}} \vee z_{1}) \cdot \prod_{k=n_{1}+1}^{n_{2}-1} (x_{n_{2}} \vee x_{k}) = \left(x_{n_{2}} \vee \prod_{k=0}^{n_{1}-1} (x_{n_{1}} \vee x_{k})\right) \cdot \prod_{k=n_{1}+1}^{n_{2}-1} (x_{n_{2}} \vee x_{k})$

=  $\prod_{k=0}^{n_{1}-1} (x_{n_{2}} \vee x_{n_{1}} \vee x_{k}) \cdot \prod_{k=n_{1}+1}^{n_{2}-1} (x_{n_{2}} \vee x_{k}) = g_{n_{2},i}(x)$

Following this chain of arguments, it is straightforward to show that  $z_s = g_{n_s,i}(x)$  and that the carry out of the (i-1)-th location is  $z_s \cdot \prod_{k=n_s+1}^{i-1} x_k = g_{i,bin_i(i)}(x)$ . Thus it follows that the sum we are looking for is  $x_i \oplus g_{i,bin(i)}(x)$ .

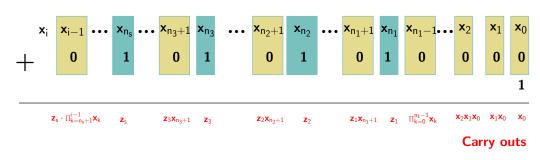

Figure 7: Visual representation of the addition

The expression for  $g_{i,bin(i)}(x)$  naturally has the longest circuit depth for i = u - 1 = n - d - 1. The number of product terms in the expression is bounded by n - d. Therefore the depth required to construct the product terms, if the and gates were arranged in a binary tree like manner is around  $\log_2(n - d)$ . Furthermore, each collection of bracket containing terms that are **OR**-ed together can also have a maximum of n - d terms, which implies each such term can also be constructed using  $\log_2(n - d)$  depth. Putting this together we arrive at  $2 \cdot \log_2(n - d)$ . We also have to account for the decimal up-counter t which counts from  $0 \rightarrow 2^{n-d} - 1$  in steps of 1. But it is well known in circuit theory that the maximum depth required in this up-counter is only  $\log_2(n - d)$  (i.e. for the update bit of the msb flip-flop which is  $t_{n-d-1} \oplus \prod_{k=0}^{n-d-2} t_k$ ).

#### 3.3.2 Representation of the ANF vector

So far we have avoided some of the finer operational details of the circuit to concentrate on the macro-level issues of dataflow through the circuit. One of the important topics we have not dealt with so far, is the issue of representing any degree-limited ANF coefficient set as a bit vector. The uncompressed ANF vector of an *n*-variable Boolean function has  $2^n$  entries and mapping each coefficient into an array can be done canonically as explained earlier in Section 2 and further shown in Figure 2. For example the  $x_0x_2$  term has coefficient 1: since the term can be written as  $x^{101} := x_0^1 \cdot x_1^0 \cdot x_2^1$ , the exponent vector 101 (5 in decimal) denotes the position where a one is inserted in the array. However when we are dealing with functions of a small degree d, coefficients of all terms of degree larger than d are zero and so in order to accommodate the potentially  $\binom{n}{\frac{1}{4d}}$  non-zero coefficients we must be able to map them into an array of equal length, i.e. we need to decide which array location a given coefficient is going to reside in. This is important to decide for the following reasons

- 1. We have left the issue of the ordering in Lines 1,2 in Algorithm 1 open. The ANF vector should be so represented so that constructing the vectors  $A_{top}/A_{bottom}$  from  $A_0$  should be efficient at all levels of recursion.

- 2. The ANF representation should be such that we can efficiently use **Expmob1** at the leaf nodes of the recursion tree.

- 3. The circuit constructed for some  $n = n^*$ ,  $d = d^*$ , should produce correct result when used for all  $n < n^*$  and  $d < d^*$ , i.e. the circuit should work seamlessly for all smaller and lower degree Boolean functions.

Let H(n,d) be the set of all binary strings of length n whose hamming weight is less than or equal to d, where we will treat the elements of this set as both binary strings and integers. The goal is to construct a mapping  $\chi_{n,d}: H(n,d) \to \left[0, \binom{n}{\downarrow d} - 1\right]$ , so that the coefficient of the  $x^D$  term for any  $D \in H(n,d)$  is placed at location  $\chi_{n,d}(D)$  in the compressed ANF vector. From the description of **Expmob1** in Section 3, the following things can be seen

- a) if we are using a butterfly circuit to construct the derivative with respect to any variable  $x_{\ell}$ , then the two inputs to the circuit are the coefficients at  $x^D$  and  $x^{D \oplus e_{\ell}}$ . Without loss of generality, let us assume that the  $\ell$ -th bit of D is zero i.e.  $D \cdot e_{\ell} = 0$ .

- **b)** The coefficient of  $x^D$  is copied as is from  $A_0$  to  $A_{top}$  (or if we follow the terminology developed later: from  $A[\ell]_b$  to  $A[\ell+1]_b$ ). The coefficients of  $x^D$  and  $x^{D\oplus e_\ell}$  are added and copied to  $A[\ell+1]_{b+e_\ell}$ .

- c) If D be such that  $hw(D \oplus e_{\ell}) > d$ , then this last addition is not necessary since the coefficient of  $x^{D \oplus e_{\ell}}$  is 0 by assumption.

However note that the size of the vectors  $A[\ell]_b$  and  $A[\ell+1]_b$  are  $\binom{n-\ell}{\downarrow d}$  and  $\binom{n-\ell-1}{\downarrow d}$  respectively. So if any  $D \in H(n-\ell,d)$ , then we ought to not only decide what  $\chi_{n-\ell,d}(D)$  would be but also in which locations of  $A[\ell+1]_b/A[\ell+1]_{b+e_\ell}$ , the butterfly outputs would go to. It seems we need to determine a series of mappings  $\chi_{n-\ell,d}$ , however we will see how only unified mapping will take care of our requirements. Let  $\chi_{n,d}(D) = y$  if D be the y-th largest integer with hamming weight less than or equal to d. For example when n = 8, d = 2, we have  $\chi_{8,2}(u) = u$  for  $0 \le u \le 6$ , and  $\chi_{8,2}(8) = 7$ ,  $\chi_{8,2}(9) = 8$ ,  $\chi_{8,2}(10) = 9$ ,  $\chi_{8,2}(12) = 10$  etc. The example makes it clear that the map  $\chi_{n,d}$  induces a co-lexicographical (colex) ordering among all d and lesser hamming weighted binary strings of length n. In fact  $\chi_{n,d}$  acts as a rank function that assigns strings ranks in accordance with the colex ordering.

Note that we have  $f(x_0, x_1, x_2, \ldots) = x_0 \cdot \frac{\delta f}{\delta x_0}(x_1, x_2, \ldots) \oplus f(0, x_1, x_2, \ldots)$ . Rewrite this as  $x_0 \cdot f_1(x_1, x_2, \ldots) \oplus f_2(x_1, x_2, \ldots)$ , where  $f_1 = \frac{\delta f}{\delta x_0}$  and  $f_2 = (0, x_1, x_2, \ldots)$ . Note that  $A[1]_{00\ldots}$  gets the ANF vector of  $f_2$  and  $A[1]_{10\ldots}$  gets the ANF vector of  $f_1 \oplus f_2$  after the butterfly operation. Therefore we have the following transitions

- 1. Algebraically  $f_2$  is simply all terms of f with the terms containing  $x_0$  removed. In terms of ANF,  $f_2$  is therefore simply the terms contained at the indices of type  $0 \parallel s$  (where s is any (n-1)-bit string) in the uncompressed ANF vector. These are simply copied to the index s in  $f_2$ . In the compressed world, therefore, all entries at location  $\chi_{n,d}(0 \parallel s)$  of  $A[0]_{00...}$  should go to location  $\chi_{n-1,d}(s)$  of  $A[1]_{00...}$ . However note that when expanded as integers,  $0 \parallel s$  and s give rise to the same integer. Thus for ease of use  $\chi_{n-1,d}(s)$  can simply be denoted as  $\chi_{n,d}(0 \parallel s)$ , and if we view the arguments of these functions as integers we do not need to define any  $\chi_{n-i,d}$  separately.

- 2. Similarly for  $f_1 \oplus f_2$ , in the uncompressed form, all terms at indices  $0 \parallel s$  are added with terms at  $1 \parallel s$  and copied to  $0 \parallel s$ . Thus in the compressed form we should add terms at locations  $\chi_{n,d}(0 \parallel s)$ ,  $\chi_{n,d}(1 \parallel s)$  (if  $1 \parallel s$  has hamming weight less than or equal to d) of  $A[0]_{00...}$  and copy it to location  $\chi_{n,d}(s)$  of  $A[1]_{10...}$ .

- 3. The same idea applies to all the levels of the recursion tree.

- 4. Note that in  $\chi_{n,d}$  all integers of hamming weight less than or equal to d are mapped to itself. Thus at the lowest leaves of the recursion tree, we can apply the canonical version of Möbius Transform as used in **Expmob1**.

We are yet to determine if the mapping  $\chi_{n,d}$  can be computed efficiently. The following lemma addresses this computational issue.

**Lemma 1.** For positive integers n, d with  $d \le n$ , and  $s \in H(n, d)$ , let  $s = 2^{i_0} + 2^{i_1} + \cdots$ , be the binary expansion of the integer s, where  $i_0 > i_1 > \cdots \ge 0$ . Then we have

$$\chi_{n,d}(s) = \begin{pmatrix} i_0 \\ \downarrow d \end{pmatrix} + \begin{pmatrix} i_1 \\ \downarrow d-1 \end{pmatrix} + \cdots$$

where we extend the definition of  $\begin{pmatrix} x \\ \downarrow y \end{pmatrix}$  as follows:

$$\begin{pmatrix} x \\ \downarrow y \end{pmatrix} = \begin{cases} \sum_{i=0}^{y} \binom{x}{i} & \text{if } x \ge y, \\ 2^{x} & \text{otherwise.} \end{cases}$$

Proof. As per the definition of  $\chi_{n,d}$ , given s we have to count how many integers strictly less than s have hamming weight bound by d. It is obvious that this number for any  $2^m$ is simply  $\binom{m}{\downarrow d}$ , i.e. number of m-bit strings of hamming weight less than or equal to d. Hence the number of such strings in the range  $[0, 2^{i_0})$  is  $\binom{i_0}{\downarrow d}$ . The number of such integers in the range  $[2^{i_0}, 2^{i_0} + 2^{i_1})$  are strings which have 1 in the  $i_0$ -th position and of hamming weight less than or equal to d-1 in the last  $i_1$  bits, and therefore equal to  $\binom{i_1}{\downarrow d-1}$ . Taking this argument forward for the successive  $i_2, i_3, \ldots$ , we arrive at the required result.  $\Box$

### 3.4 Helping Circuit Compiler synthesize faster

The above lemma shows that the map  $\chi_{n,d}(\cdot)$  can be efficiently computed. However for ease of synthesis, one may want to precompute and store a few of the above values to help the circuit compiler construct an optimal circuit especially when n becomes larger. One could store all values of  $\chi_{n,d}(s)$ ,  $\forall s \in H(n,d)$  for this purpose, but note that the arguments "s" of this function are not exactly contiguous integers and thus we would not be able to store the function table in any continuous memory structure like an array. We could employ a hash table for this purpose, however designing a good collision free hash function for this purpose is an open problem.

Another method we could employ is to store the adjacency matrix of a graph that we describe below. Note that at the  $\ell$ -th recursion step, we need access to locations  $\chi_{n,d}(0 \parallel s)$ ,  $\chi_{n,d}(1 \parallel s)$  of the current register, where s is an  $n - \ell - 1$  bit string. Imagine the graph G = (V, E), in which the elements of  $\left[0, \binom{n}{\downarrow d} - 1\right]$  are nodes and each node  $\alpha$  in this set is connected with at most n - d types of edges to at most n - d neighbors. An edge of type  $\ell$ , (for  $0 \le \ell < n - d$ ) connects  $\alpha$  to  $\beta := \chi_{n,d} \left[\chi_{n,d}^{-1}[\alpha] \oplus e_\ell\right]$  if  $hw(\beta) \le d$  and unconnected otherwise. This is helpful because at step  $\ell$  of the recursion tree, if  $\alpha = \chi_{n,d}(0 \parallel s)$  then the two inputs to the butterfly circuit can be equivalently seen as the wires at locations  $\alpha$  and  $\beta$ , as it can be easily deduced that  $\beta = \chi_{n,d}(1 \parallel s)$ . One can now define the reduced adjacency matrix AM of size  $\binom{n}{\downarrow d} \times (n - d)$  such that

$$AM[\alpha, \ell] = \begin{cases} \chi_{n,d} \left[ \chi_{n,d}^{-1}[\alpha] \oplus e_{\ell} \right], & \text{if } hw(\chi_{n,d}^{-1}[\alpha] \oplus e_{\ell}) \le d \\ 0 & \text{otherwise.} \end{cases}$$

Thus the  $\ell$ -th recursion step can be re-written from:

• For all  $n - \ell - 1$  bit strings s with hw  $\leq d$

$$1 A[\ell+1]_{b}(\chi_{n,d}(s)) \leftarrow A[\ell]_{b}(\chi_{n,d}(0 || s))$$

$$2 \text{ If } hw(\chi_{n,d}(1 || s)) \leq d:$$

$$A[\ell+1]_{b+e_{\ell}}(\chi_{n,d}(s)) \leftarrow A[\ell]_{b}(\chi_{n,d}(0 || s)) \oplus A[\ell]_{b}(\chi_{n,d}(1 || s))$$

$$3 \text{ Else } A[\ell+1]_{b+e_{\ell}}(\chi_{n,d}(s)) \leftarrow A[\ell]_{b}(\chi_{n,d}(0 || s))$$

to the following equivalent form that uses the AM matrix:

• For  $\alpha = 0$  to  $\binom{n-\ell-1}{\downarrow d} - 1$ **1**  $A[\ell+1]_b(\alpha) \leftarrow A[\ell]_b(\alpha)$

**2** If

$$AM[\alpha, \ell] \neq 0$$

$A[\ell+1]_{b+e_{\ell}}(\alpha) \leftarrow A[\ell]_{b}(\alpha) \oplus A[\ell]_{b}(AM[\alpha, \ell])$

**3** Else  $A[\ell+1]_{b+e_{\ell}}(\alpha) \leftarrow A[\ell]_{b}(\alpha)$

Using the 2nd description is much easier to write an RTL code for describing the Möbius Transform circuit in any hardware description language. Additionally, the circuit compiler also outputs the optimized netlist faster. In Appendix A, we outline an algorithm to generate AM efficiently in polynomial time.

#### **3.5 Further Utilities**

Using the circuit for smaller functions: The circuit once constructed for some upper limit (n, d) also caters for Boolean functions for any number of variables  $n_0 < n$ . Since any  $n_0$ -variable Boolean function (for  $n_0 < n$ ) is also an *n*-variable Boolean function, i.e. with the additional variables set to zero, the only thing we need to do is to embed the ANF of the  $n_0$ -variable Boolean function as a the ANF of an *n*-variable Boolean function with appropriate zero padding. This is aided by the fact that  $\chi_{n,d}$  has been defined in a manner so that  $\chi_{n-1,d}(s)$  is the same as  $\chi_{n,d}(0 \parallel s)$  for any (n-1)-bit string *s*. Thus in order to embed any (n-1)-variable Boolean function we simply add the coefficient corresponding to *s* in  $\chi_{n,d}(0 \parallel s)$  and place 0 in  $\chi_{n,d}(1 \parallel s)$ . Since the function  $\chi_{n,d}$  is monotonous this would amount to filling up locations  $\left[0, \binom{n-1}{\downarrow d} - 1\right]$  with coefficients of the smaller Boolean function and padding the remaining i.e.  $\left[\binom{n-1}{\downarrow d}, \binom{n}{\downarrow d} - 1\right]$  locations with zeros. By induction on *i*, the same applies to any arbitrary (n-i)-variable function.

**Finding truth table when some variables are fixed to constants:** Often one is interested to find solutions to a system of equations in which a fraction of variables has been fixed to some given constant. Since our strategy in solving a system of polynomial equations is to compute the **OR** the respective truth tables (see Section 1.1), we would therefore be interested to find the truth table of a polynomial when some variables are fixed. To do this, we could either first simplify the given Boolean polynomial by fixing some individual variables to constants and then using the corresponding reduced ANF vector as input to the circuit, after appropriately zero padding it. However this naturally requires additional computations, i.e to simplify the original polynomial in the first place.

However if the t variables to be fixed are lexicographically the first t variables of the system (for any  $t \leq n-d$ ) then we can do better. We see from Figure 6, that at the *i*-th stage the ANF vector at the bottom most register is  $A[n-d]_{bin_{n-d}(i)}$ . As a result the truth table output after the **Expmobl** circuit is  $f(bin_{n-d}(i), \ldots)$ , i.e. in which the first (n-d) bits of f is already set to  $bin_{n-d}(i)$ . Thus one can use this method to extract the truth tables when the number of variables to be fixed are less than n-d. Note that one may think that one would need to wait exactly *i* cycles to obtain the tables, which can be counterproductive if *i* is large. Note that Figure 6 already starts with  $A[3]_{000}$  in the bottom most register at t = 0, as in the previous 3 cycles, i.e. t = -3, -2, -1, the corresponding  $S[i]_t$ 's were all set to zeros. Instead if all of these were set to 1, then at t = 0, the signal in the bottom most register would be  $A[3]_{111}$ , and we would get the truth table of f(1, 1, 1, ...) from the **Expmobl** circuit. Similarly by adjusting the initial select signals we can get the truth table where the first (n-d) variables are fixed to any arbitrary constant in the first cycle itself.

#### 3.6 Synthesis Results

For the actual synthesis, we can do some optimizations as follows: In Figure 6, we can see that the topmost register of size  $\binom{n}{\downarrow d}$  essentially holds a constant value throughout

|    |        |          | d = 4     |        |          |       |          | d = 3     |        |          |

|----|--------|----------|-----------|--------|----------|-------|----------|-----------|--------|----------|

| n  | Area   | $T_{cr}$ | $T_{min}$ | Power  | Energy   | Area  | $T_{cr}$ | $T_{min}$ | Power  | Energy   |

|    | GE     | (ps)     | (ns)      | (mW)   | (nJ)     | GE    | (ps)     | (ns)      | (mW)   | (nJ)     |

| 8  | 2078   | 40.57    | 0.811     | 0.707  | 0.014    | 1468  | 41.11    | 1.521     | 0.479  | 0.018    |

| 9  | 3535   | 44.87    | 1.660     | 1.121  | 0.041    | 2265  | 41.47    | 2.903     | 0.721  | 0.050    |

| 10 | 5780   | 46.77    | 3.274     | 1.749  | 0.122    | 3338  | 45.48    | 6.134     | 1.043  | 0.141    |

| 11 | 9040   | 66.95    | 9.038     | 2.715  | 0.366    | 4682  | 60.25    | 15.906    | 1.461  | 0.386    |

| 12 | 13525  | 75.95    | 20.051    | 4.020  | 1.061    | 6563  | 48.69    | 25.367    | 2.029  | 1.057    |

| 13 | 20024  | 61.74    | 32.167    | 5.800  | 3.022    | 8900  | 74.46    | 76.992    | 2.740  | 2.834    |

| 14 | 28754  | 73.61    | 76.113    | 8.375  | 8.661    | 11792 | 72.00    | 148.248   | 3.620  | 7.453    |

| 15 | 40706  | 73.18    | 150.678   | 11.854 | 24.409   | 15228 | 74.82    | 307.361   | 4.729  | 19.428   |

| 16 | 56683  | 79.71    | 327.449   | 16.385 | 67.311   | 19457 | 68.95    | 565.735   | 6.091  | 49.976   |

| 17 | 77402  | 78.07    | 640.564   | 22.305 | 183.016  | 24253 | 83.31    | 1366.117  | 7.748  | 127.051  |

| 18 | 102916 | 90.26    | 1480.084  | 29.821 | 489.015  | 30839 | 81.32    | 2665.014  | 9.718  | 318.573  |

| 19 | 134835 | 93.46    | 3063.899  | 39.289 | 1288.025 | 37781 | 76.57    | 5019.317  | 11.988 | 785.846  |

| 20 | 174268 | 101.48   | 6652.217  | 51.141 | 3352.416 | 45653 | 83.87    | 10994.434 | 14.695 | 1926.389 |

|    |        |          | d = 2     |        |          |       |          |           |        |          |

| n  | Area   | $T_{cr}$ | $T_{min}$ | Power  | Energy   |       |          |           |        |          |

|    | GE     | (ps)     | (ns)      | (mW)   | (nJ)     |       |          |           |        |          |

| 8  | 856    | 49.24    | 3.445     | 0.284  | 0.020    | ]     |          |           |        |          |

| 9  | 1160   | 51.82    | 6.996     | 0.394  | 0.053    |       |          |           |        |          |

| 10 | 1506   | 47.20    | 12.461    | 0.490  | 0.129    |       |          |           |        |          |

| 11 | 1984   | 58.09    | 30.265    | 0.630  | 0.328    |       |          |           |        |          |

| 12 | 2552   | 69.16    | 71.511    | 0.802  | 0.829    |       |          |           |        |          |

| 13 | 3123   | 65.45    | 134.761   | 0.986  | 2.030    |       |          |           |        |          |

| 14 | 3817   | 70.22    | 288.464   | 1.183  | 4.860    |       |          |           |        |          |

| 15 | 4584   | 70.96    | 582.227   | 1.429  | 11.727   |       |          |           |        |          |

| 16 | 5445   | 71.81    | 1177.540  | 1.720  | 28.208   |       |          |           |        |          |

| 17 | 6495   | 74.33    | 2346.761  | 2.057  | 67.440   |       |          |           |        |          |

| 18 | 7575   | 75.33    | 4938.032  | 2.420  | 158.639  |       |          |           |        |          |

| 19 | 8766   | 86.07    | 11282.830 | 2.819  | 369.585  |       |          |           |        |          |

| 20 | 10168  | 81.94    | 21481.554 | 3.286  | 861.349  |       |          |           |        |          |

Table 2: Results for d = 2, 3, 4 for the **Polymob1** circuit. Power reported at 1 GHz.

the lifetime of the Möbius Transform operation, and as such it can be removed from the circuit if the ANF signal is assumed as available on the input wires to the circuit. Using this tweak, we again synthesized the **Polymob1** circuit using the Nangate 15 nm open cell library for various values of  $n \in [8, 20]$  and  $d \in [2, 4]$ . Note that the values of d chosen apply to a number of instances of cryptanalytic problems known in literature as mentioned in the introduction.

The results are presented in Table 2. As stated earlier, the circuits were synthesized to minimize the total critical path, which allows us to clock them using higher frequencies. The minimum time  $T_{min}$  taken to compute the transform is calculated as  $[2^{n-d} + (n-d)] \cdot T_{cr}$ where  $T_{cr}$  is the critical path of the circuit. Since the depth of the circuit (and therefore to some extent also  $T_{cr}$ ) increases logarithmically and the number of cycles increases exponentially with respect to (n-d), some interesting tradeoffs can be observed: for example to compute the Möbius Transform of quadratic Boolean functions one may either use the circuit for d = 2, 3 or 4. Because of the exponential dependence on n - d, the total physical time taken to compute the transform undoubtedly decreases with increase in d: however it has to be paid for with larger circuit area and energy consumption. Furthermore, it can also be seen that for the range  $8 \le n \le 14$  for which we have experimental data for the Expmob1, Expmob2, Polymob1 circuits, the energy consumed by the Polymob1 circuits is larger than the corresponding Expmob1/Expmob2 circuits. This is to be expected primarily because **Polymob1** is essentially a serialized circuit that performs the transform using exponential amount of time (in n-d) whereas **Expmob1/Expmob2** either take constant or linear time to execute.

#### 3.7 Energy Analysis of the Polymob1 Circuit

We will try to construct an analytical model of the energy consumed in the circuit. It is important to recall that two components are primarily responsible for the amount of energy dissipated in CMOS circuits:

- Dynamic power dissipation due to the charging and discharging of load capacitances and the short-circuit current. Each  $0 \rightarrow 1/1 \rightarrow 0$  transition contributes to the dynamic dissipation, and hence this component varies directly as the clock frequency.

- Static power dissipation due to leakage current and other current drawn continuously from the power supply. This type of power is generally not dependent on the frequency of the clock driving the circuit.

Thus the total energy dissipation can be written as  $E_{total} = E_{dynamic} + E_{static}$ . Since static power is independent of clock frequency we can write  $E_{static} = P_{static} \cdot T_d$ , where  $P_{static}$  is the static power consumption and  $T_d$  is the total physical time taken to compute the Möbius Transform.

It is not altogether unreasonable to assume that  $P_{static}$  is related to the circuit area. In this respect let us look at the combinatorial and sequential elements of the circuit separately. The total number of flip-flops in the circuit can be estimated easily to be equal to  $F(n,d) = \sum_{i=1}^{n-d} {n-i \choose \downarrow d}$ . The total static power due to this component can be estimated to be around  $P_{static,seq} = F(n,d) \cdot \alpha_s$ , where  $\alpha_s$  is the leakage power due to a single flip-flop. To estimate the static power due to the combinatorial portion as an expression is trickier since as n increases the compiler does various optimizations (which involves including in final netlist, cells with higher number of inputs and drive strength) to reduce the combinatorial circuit area. As a result, as n increases, the ratio between (a) the actual combinatorial circuit area as reported by the compiler and (b) the area estimated by counting the number of two input multiplexers and xor gates, continually decreases. While the combinatorial static power  $P_{static,comb}$  can still be estimated as the product of some constant  $\alpha_c$  and the combinatorial area  $A_c$ , there is no good way of estimating  $A_c$  in terms of n, d. As a loose upper bound we can estimate  $A_c$  by counting the number of multiplexers and xor gates, but this overestimates the static power as n increases.

Regarding the dynamic power, the lion's share of the consumption is due to the register writes. In our simulation results for  $(n, d) \in [8, 20] \times [2, 4]$  the dynamic power contribution due to the combinatorial portion of the circuit has been less than 10% of the total dynamic power. Hence  $P_{dynamic} \approx P_{dynamic,seq} = F(n, d) \cdot \beta_s$ , for some constant  $\beta_s$ . Combining the above three expressions the energy consumed in the circuit can be written as:

$$E_{\text{Polymob1}} = T_d \cdot \left( F(n,d) \cdot \alpha_s + A_c \cdot \alpha_c + F(n,d) \cdot \beta_s \right)$$

(3)

We can estimate  $A_c = F(n,d) \cdot A_{mux} + (F(n,d) + d \cdot 2^{d-1}) \cdot A_{xor}$ , where  $A_{mux}/A_{xor}$  are the silicon areas of the 2 input multiplexer/xor gate respectively. The values of  $\alpha_c, \alpha_s, \beta_s$  can be estimated using power simulation for n = 8, d = 2, or any other data point.

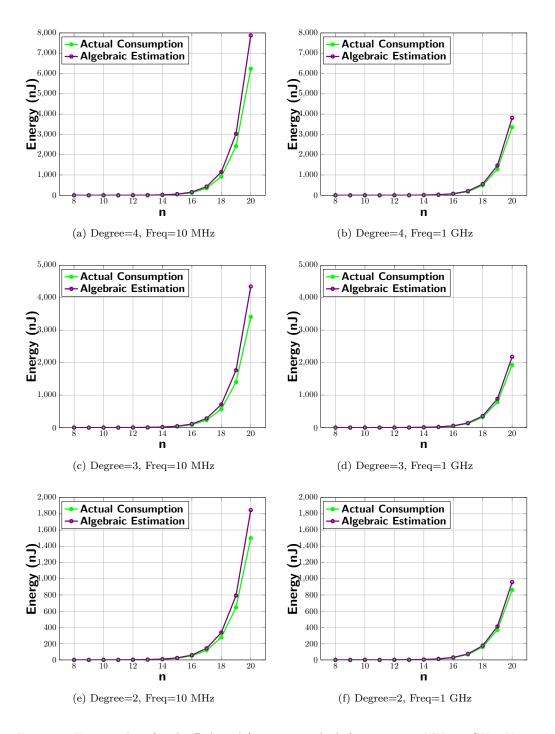

At higher frequencies: The left side plots in Figure 8 show the comparison of the actual energy consumption as reported by the power compiler and that estimated by the algebraic expression in Equation (3), when the clock frequency is 10 MHz. The purple plot which represents the figures obtained by Equation 3, clearly overestimates the energy. However consider the case when the clock frequency is increased to 1 GHz: a) since the static power is independent of the clock frequency, it remains the same, and b) the value of  $T_d$  decreases by a factor of 100. Both these factors ensure that the contribution of the static power to the total energy consumption decreases 100-fold. The contribution of the dynamic power however remains the same, since this is proportional to the clock frequency, i.e  $P_{dynamic}$  itself increases 100-fold so that  $P_{dynamic} \cdot T_d$  remains constant. Then the total energy is almost entirely dynamic in nature, and so the numbers estimated by Equation (3) more closely matches the actual consumption as shown by the right side plots in Figure 8.

Figure 8: Energy plots for the **Polymob1** circuit at clock frequency 10 MHz, 1 GHz. Note that "actual consumption" refers to the energy obtained after timing simulation on the synthesized circuit.

## 4 Solving Polynomial equations of degree $\leq d$

One of the primary uses of the Möbius Transform circuit is in finding solutions of a system of Boolean polynomials bounded by some algebraic degree d. Recapitulating, if  $f_1, f_2, f_3, \ldots, f_m$  are the m polynomials whose common root we are aiming to find, then the root  $r \in \{0, 1\}^n$  is an *n*-bit vector which simultaneously satisfies  $f_1(r) = f_2(r) = \cdots = f_m(r) = 0$ . We can combine the above in a single equation:

$$\bigvee_{i=1}^{m} f_i(r) = 0$$