Jakob Feldtkeller Ruhr University Bochum Horst Görtz Institute for IT Security Bochum, Germany jakob.feldtkeller@rub.de

Pascal Sasdrich Ruhr University Bochum Horst Görtz Institute for IT Security Bochum, Germany pascal.sasdrich@rub.de

# ABSTRACT

Observation and manipulation of physical characteristics are wellknown and powerful threats to cryptographic devices. While countermeasures against passive side-channel and active fault-injection attacks are well understood individually, combined attacks, i.e., the combination of fault injection and side-channel analysis, is a mostly unexplored area. Naturally, the complexity of analysis and secure construction increases with the sophistication of the adversary, making the combined scenario especially challenging. To tackle complexity, the side-channel community has converged on the construction of small building blocks, which maintain security properties even when composed. In this regard, Probe-Isolating Non-Interference (PINI) is a widely used notion for secure composition in the presence of side-channel attacks due to its efficiency and elegance. In this work, we transfer the core ideas behind PINI to the context of fault and combined security and, from that, construct the first trivially composable gadgets in the presence of a combined adversary.

# CCS CONCEPTS

$\bullet$  Security and privacy  $\rightarrow$  Side-channel analysis and countermeasures.

# **KEYWORDS**

Side-Channel Analysis; Fault-Injection Analysis; Combined Attacks; Gadgets; Probe-Isolating Non-Interference

## **1** INTRODUCTION

In contrast to standard assumptions in theoretical models of cryptography, physical devices are not black boxes that perfectly hide internal computations. Instead, an adversary can observe and manipulate physical characteristics to reveal and determine intermediates, ultimately violating given security guarantees. To capture *passive* Side-Channel Analysis (SCA), which exploits dependencies between secrets and characteristics such as timing [29], instantaneous power consumption [30], or electromagnetic emanations [23], Jan Richter-Brockmann Ruhr University Bochum Horst Görtz Institute for IT Security Bochum, Germany jan.richter-brockmann@rub.de

Tim Güneysu Ruhr University Bochum Horst Görtz Institute for IT Security Bochum, Germany tim.gueneysu@rub.de

the theoretical models were extended with access to intermediates [11, 18, 25]. A well researched countermeasure against SCA is *masking* [11] that randomizes intermediate values via secret sharing and benefits from a broad theoretical and formal foundation. In contrast, for *active* Fault Injection Analysis (FIA), which manipulates physical characteristics for example through clock glitches [16], voltage glitches [44], electromagnetic pulses [14, 19], or focused laser beams [42], theoretical models were extended with the ability to manipulate internal computations [38]. Here, a well researched countermeasure is *redundancy*, either in time, space, or information [1, 32].

*Combined Attacks.* After reaching a deep understanding of theoretical models for both passive and active attacks separately, the research community is now ready to combine both models and consider an adversary able to launch SCA and FIA simultaneously, denoted by the term Combined Analysis (CA). Already existing research in this area has shown that the trivial combination of masking and redundancy is insufficient to protect against such a powerful adversary [35] and, hence, dedicated and formal methods are required that consider reciprocal effects, e.g., inspired by Multi-Party Computation (MPC) [34].

Composable Gadgets. The complexity of security analysis and verification increases with the power of the adversary and the size of the design under consideration and rapidly becomes prohibitive. Nevertheless, to construct formally proven systems, the research community in SCA focuses on the construction of secure building blocks, so called gadgets, that maintain their security properties when composed to larger circuits. Unfortunately, the broadly used security guarantees of Ishai-Sahai-Wagner (ISW) probing security [25] are not sufficient for secure composition and additional notions needed to be introduced. In essence, those composability notions restrict the propagation of leakage by a combination of isolation and re-randomization. For this, Barthe et al. introduced Non-Interference (NI) [3] and Strong Non-Interference (SNI) [4] which achieve composition by preventing the propagation of leakage between different gadgets. Later, Cassiers and Standaert proposed Probe-Isolating Non-Interference (PINI) [10] which introduces and isolates so called share domains. For most cases, PINI has proven to be more efficient, as it allows the trivial implementation and composition of linear functions.

CCS '22, November 7–11, 2022, Los Angeles, CA, USA

<sup>2022.</sup> This is the author's version of the work. It is posted here for your personal use. Not for redistribution. The definitive Version of Record was published in *Proceedings of the 2022 ACM SIGSAC Conference on Computer and Communications Security (CCS '22), November 7–11, 2022, Los Angeles, CA, USA, https://doi.org/10.1145/3548606.3560614.*

Jakob Feldtkeller, Jan Richter-Brockmann, Pascal Sasdrich, and Tim Güneysu

Table 1. Notations used throughout this work.

| Notation |               | Description                                                                                        |  |  |  |  |  |

|----------|---------------|----------------------------------------------------------------------------------------------------|--|--|--|--|--|

| SA       | d<br>s        | Security order of a masking scheme (countermeasure).<br>Number of shares used by a masking scheme. |  |  |  |  |  |

| SC       | i, j          | Index of share domain                                                                              |  |  |  |  |  |

|          | k             | Security order of redundancy scheme (countermeasure).                                              |  |  |  |  |  |

| FIA      | n             | Number of duplications used by a redundancy scheme.                                                |  |  |  |  |  |

| Ē        | $\ell, \ell'$ | Index of redundancy domain                                                                         |  |  |  |  |  |

|          | t             | Fault type                                                                                         |  |  |  |  |  |

|          | C, G          | Represents a digital logic circuit or gadget, respectively.                                        |  |  |  |  |  |

| Misc     | F             | Functions are written in sans serif font.                                                          |  |  |  |  |  |

| Mi       | $\mathcal{S}$ | Sets are denoted as upper-case characters in calligraphic font                                     |  |  |  |  |  |

|          | Reg[a]        | Hardware register with input a.                                                                    |  |  |  |  |  |

Similarly, definitions of composability notions for FIA and CA, based on NI and SNI, were proposed by Dhooghe and Nikova [15] and later refined by Richter-Brockmann et al. [35]. Those notions come in different variants, a simpler version where the order of FIA security is dependent on the order of SCA protection and a stronger variant with independence between SCA and FIA. However, there are currently no composable hardware gadgets for CA as the first proposal by Dhooghe and Nikova is not transferable to hardware and their second proposal has been shown to be flawed by Richter-Brockmann et al. [35].

*Contributions*. In this work, we provide multiple composability notions, inspired by PINI, for both FIA and CA. As a warm-up, we introduce Fault-Isolating Non-Interference (FINI) (Section 3) for FIA that formalizes the well known security and composability guarantees from spacial replication. For CA, we define a *Shared Re-dundancy Domain (SRD)* and introduce two different composability notions based on the isolation of both share domains and SRDs. While the first notion, Combined-Isolating Non-Interference (CINI) (Section 4), introduces a dependency between the order of SCA and FIA security, the stronger Independent Combined-Isolating Non-Interference (CINI<sub>ind</sub>) (Section 5) eventually achieves independence between SCA and FIA security.

For all three composability notions we provide practical gadgets and formally prove their security. Here, we focus on the combination of masking with spacial replication in the context of CA. Further, we integrated our notions into a state-of-the-art verification tool for CA [35] and provide an easily extendable tool for the transformation of unprotected to protected circuits (Section 6)<sup>1</sup>. Finally, we provide a rigorous evaluation of all proposed gadgets both for security and implementation costs in hardware (Section 7).

## 2 PRELIMINARIES

## 2.1 Notation

Important notations are given in Table 1. We use subscripts to denote the share index and superscripts to denote the replication index. Further, we use the notion of a *faulty value* as shorthand for a fault that was injected in the gate that produces the corresponding value.

# 2.2 Circuit Model

For the sake of simplicity, but without loss of generality, we restrict the set of combinational gates to  $G_c = \{\text{not}, \text{and}, \text{nand}, \text{xor}, \text{xnor}\}$ and the set of memory gates to clocked registers  $G_m = \{\text{reg}\}$ . In addition, we define a randomness gate  $G_{\text{rand}} = \{\text{rand}\}$  that has no input and for each clock cycle outputs an independent and uniformly chosen random value.

Then, we model a digital logic circuit C as a *directed acyclic* graph  $\mathcal{D} = \{\mathcal{V}, \mathcal{E}\}$ , where vertices  $v \in \mathcal{V}$  represent logical gates  $g \in \mathcal{G}_{c} \cup \mathcal{G}_{m} \cup \mathcal{G}_{rand}$  and edges  $e \in \mathcal{E}$  represent wires connecting two gates and carrying an element of the finite field  $\mathbb{F}_2$ . Please note, as we do not consider leakage from transitions<sup>2</sup>, it is sufficient to analyze unrolled implementations even when there are loops in a circuit.

## 2.3 Security via Simulation

Simulation is a proof technique for security arguments that is useful for statements about composability [8, 33]. For that, we define a *real* and an *ideal* game, where the ideal game is trivially secure (under some adversary model). The real game is secure iff there exists no adversary who can distinguish the real from the ideal game with a probability higher than  $\frac{1}{2}$ . We will define the ideal game as a probabilistic polynomial-time simulator that reproduces the view of the adversary without access to any secret.

#### 2.4 Side-Channel Security

Adversary Model. An adversary  $\mathcal{A}_p$  in the context of stateless probing security [25], is given access to a circuit C that can be invoked multiple times. Prior to each invocation,  $\mathcal{A}_p$  can select up to *d* wires of C, so called *probes*. The view of the adversary  $\mathcal{A}_p$  is defined by the glitch-extended probes [20], i.e., by the exact values of all registers a probed wire directly depends on<sup>3</sup>. Further, a probe propagates into another wire whenever this wire is required for simulation of the probe [10].

Probing Security. In this context, probing security [25] is defined as the view of the adversary  $A_p$  always being independent of any secret, i.e., all probes can be simulated without any knowledge apart from the structure of C. Please note, that probing security does not capture horizontal attacks [5].

*Masking*. A promising and well studied countermeasure against SCA is *Boolean masking* [11], where each value  $x \in \mathbb{F}_2$  is replaced by a vector  $\langle x_0, \ldots, x_{s-1} \rangle \in \mathbb{F}_2^s$  such that each  $x_i$  is uniform random from  $\mathbb{F}_2$  for  $i \leq s - 2$  and  $x_{s-1} = \bigoplus_{i=0}^{s-2} x_i \oplus x$ . We call  $x_i$  a *share* of x with *share index i*. The construction ensures that all subsets of up to s - 1 shares are independent of x. We say a share  $x_i$  violates the *independence property* of Boolean sharing iff the subset of all other shares is not independent of x. Similarly, a circuit is transformed to a *shared circuit* by transferring each operation to a representation that operates over the share vector of its inputs and outputs a share vector of its output. Hence, the initial sharing and final unsharing

<sup>&</sup>lt;sup>1</sup>We provide both tools in the supplementary material for review and will make them publicly available on GitHub after publication.

$<sup>^2</sup>$ Transitions are physical defaults that occur due to switching activities within a circuit.  $^3$ Glitches are physical defaults that occur when there are timing differences in the propagation path of signals. Hence, providing  $\mathcal{A}_p$  with all stable inputs of a probed wire captures all possible leakage via glitches [20].

operation is not part of the shared circuit and cannot be probed by  $\mathcal{A}_{p}$  [2, 25].

*Probe-Isolating Non-Interference.* The notation of probing security is not composable on its own, i.e., combining two probing secure circuits does not necessarily result in a probing secure circuit itself. For this, additional composability notations are introduced that define how to construct atomic building blocks, so called *gadgets*, that can be securely combined to larger circuits. PINI [10] ensures composability by dividing the circuit into *share domains*:

Definition 2.1 (Share Domain). The share domain *i* of a shared circuit is defined by all wires with share index *i*.

Given this, PINI ensures that information leakage cannot propagate from one share domain into another, i.e., isolating share domains and, hence, allows trivial composition as long as the inputs and outputs are a valid Boolean sharing. The efficiency of PINI comes from the fact that the share-wise implementation of the addition (xor) is PINI.

Definition 2.2 (Probe-Isolating Non-Interference [10]). A gadget G is *d*-PINI iff for any set of  $d_1$  internal probes and any set  $S_2$  of  $d_2$  share domains, such that  $d_1 + d_2 \le d$ , there exists a set  $S_1$  of at most  $d_1$  share domains such that the outputs of the share domains in  $S_2$  and the probes can be simulated with the inputs of the share domains in  $S_1 \cup S_2$ .

*Hardware Private Circuits.* Cassiers et al. [9] propose two multiplication gadgets fulfilling PINI, namely HPC<sub>1</sub> and HPC<sub>2</sub> (Algorithm 2 and 4 without highlighted parts, respectively). Intuitively, both gadgets stop cross-domain leakage by refreshing the masked input *b* before performing a shared multiplication. However, HPC<sub>2</sub> requires less randomness as it avoids a refreshing in the multiplication step via the *masked shares multiplication trick* [10], computing  $(a_i + 1) \cdot r_{i,j} + a_i \cdot (b_j + r_{i,j})$  instead of  $a_i \cdot (b_j + \tilde{r}_{i,j}) + r_{i,j}$ , as is done in HPC<sub>1</sub> (cf. Algorithm 2). For that, the security of HPC<sub>2</sub> rests on the fact that if  $a_i = 0$  then  $r_{i,j}$  is only observable in  $(a_i + 1) \cdot r_{i,j}$  (as  $a_i \cdot (b_j + r_{i,j}) = 0$ ) and otherwise  $r_{i,j}$  is only observable in  $a_i \cdot (b_j + r_{i,j})$ , which ensures a proper masking of  $b_j$ . Recently, Knichel and Moradi [27] proposed HPC<sub>3</sub> as a latency optimized alternative, similarly based on the masked shares multiplication trick.

#### 2.5 Fault-Injection Security

Adversary Model. An adversary  $\mathcal{A}_f$  in the context of fault security [35] is given access to a circuit C that can be invoked multiple times. Prior to each invocation,  $\mathcal{A}_f$  selects up to k gates in C and a fault type from the set of allowed fault types  $\mathcal{T}$  for each gate. Faults are modeled by transforming the selected gates to a different gate type which is specified by the fault type  $t \in \mathcal{T}$  [38]. Typical fault types are *set, reset* (replacing the targeted gate with a constant one or zero, respectively), or *bit flips* (inversion of the gate). A fault propagates into another wire whenever the value of the wire is influenced by the fault. The view of the adversary  $\mathcal{A}_f$  is defined by the abort signal (if existent) and the correctness of the outputs. Correctness is defined by equivalence to the *golden circuit*, which is a fault-free version of C.

*Fault Security.* Let  $G^D$  be a circuit realizing a fault detection or correction mechanism for up to *k* faults. Then *fault security* is defined as the output of the concatenation  $G^D(C(\cdot))$  always being equal to the output of the golden circuit of C or aborting [35]. Please note, that fault security is not composable on its own.

Redundancy. Protection mechanisms against fault attacks usually depend on redundancy (e.g., in time, space, or information). The simplest form of redundancy is *replication*, where all data and operations are implemented multiple times in parallel. When using k + 1 instances of a circuit C, up to k faults can be detected by comparing all instances and aborting when one instance is different. Similarly, 2k + 1 instances allow the correction of up to k faults via a majority function correcting to the value that occurs most often in the different instances. Again, the initial replication and final error detection/correction is not part of the replicated circuit and cannot be faulted by  $\mathcal{A}_f$  [35]. Naturally, redundancy can be applied at the level of single bits. Please note, that all replications share the same random values wherever fresh randomness is required.

# 2.6 Combined Security

Adversary Model. An adversary  $A_c$  in the context of combined security [35] is the combination of the adversaries  $\mathcal{A}_p$  and  $\mathcal{A}_f$ . Hence,  $A_c$  is given access to a circuit C that can be invoked multiple times and prior to each invocation  $\mathcal{A}_c$  can select up to d wires of C that are probed and up to k gates of C that are faulted according to a fault type  $t \in \mathcal{T}$ . The view of the adversary  $\mathcal{A}_c$  is defined by the glitch-extended probes, the abort signal (if existent), and the correctness of the outputs of the concatenation  $G^{D}(C(\cdot))$ , where  $G^D$  is a circuit realizing a fault detection or correction mechanism for up to k faults. Correctness is again defined by equivalence to the golden circuit of C. Here, however, the golden circuit of C incorporates the faults targeting randomness gates  $g \in \mathcal{G}_{rand}$ , i.e.,  $g \in \mathcal{G}_{rand}$  are replaced by some g' according to the fault model (see [35] for more details). Please note, that faulting some gates gives A<sub>c</sub> knowledge about the changed distribution of the dependent values, however, not necessarily the concrete values. This knowledge of changed distributions can cause additional probes that need to be simulated when the independence property of an intermediate Boolean sharing is violated. In general, value distributions are sufficient for simulation and the changed distribution is given to  $\mathcal{A}_c$  for faulty gadget inputs. A detailed discussion and justification of this model is given by Richter-Brockmann et al. [35].

Combined Security. Given some adversary  $\mathcal{A}_c$  combined security is defined as the view of  $\mathcal{A}_c$  being independent of any secret, i.e., the abort signal and the probes can be simulated only with the knowledge of the faults and the structure of C (*privacy*), and the concatenation  $G^D(C(\cdot))$  always being equal to the output of the golden circuit of C or aborting (*correctness*) [35]. In accordance with probing and fault security,  $\mathcal{A}_c$  is not allowed to probe or fault the initial sharing and replication nor the final unsharing and error detection/correction. Again, combined security is not sufficient for composition.

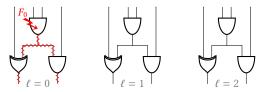

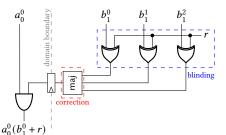

Figure 1. Isolation of fault propagation within redundancy domains.

## 3 Fault-Isolating Non-Interference

When considering circuits, hardened against fault attacks by replication, we can observe that each injected fault can only propagate within the affected redundant part. Then, having more replications than allowed adversarial faults (maximum fault cardinality) can ensure the desired level of fault security. In addition, we observe that this property is inherently composable as long as the isolation of different redundant parts remains intact. Breaking this down to the core principles, namely the isolation of domains with regard to faults, replication reveals a strong similarity with PINI [10]. While PINI isolates probe propagation within share domains, replication isolates fault propagation within *redundancy domains*.

Definition 3.1 (Redundancy Domain). The redundancy domain  $\ell$  of a redundant circuit is defined by all gates and wires with replication index  $\ell$ .

In order to generalize the core principle of replication and allow a formal treatment, we now introduce the notion of Fault-Isolating Non-Interference. FINI is the dual to PINI in that it introduces redundancy domains and requires them to be isolated in terms of fault propagation (as illustrated in Figure 1). Then, assuming sufficient redundancy domains, detection or correction is always possible by comparing the values in different redundancy domains, regardless of the fault propagation within a single redundancy domain.

In this work, we focus on a realization of FINI via replication since it is an obvious match and transports the ideas and principles more easily. However, we intentionally construct FINI as a general notion that can be applied to other redundancy-based countermeasures with an appropriate definition of redundancy domains. When considering replication, the redundancy domain is defined by the replication index, i.e., all values with replication index  $\ell$  belong to the redundancy domain  $\ell$ .

As FINI, similar to PINI, introduces an isolation between different redundancy domains instead of an isolation between gadgets, faults at inputs are allowed to propagate to outputs of the same redundancy domain. Further, faults injected inside the gadget are restricted to only propagate to outputs belonging to a single redundancy domain. We now give a more formal definition in Definition 3.2.

*Definition 3.2 (Fault-Isolating Non-Interference).* A gadget G is *k*-FINI iff the following holds:

(i) For any set  $\mathcal{F}_1$  of  $k_1$  faulty redundancy domains and every set of  $k_2$  faults injected in gates of G, with  $k_1 + k_2 \leq k$ , there exists a set of at most  $k_2$  redundancy domains  $\mathcal{F}_2$ , such that the gadget either aborts or gives an output where all values, except those belonging to the redundancy domains  $\mathcal{F}_1 \cup \mathcal{F}_2$ , are equal to the values of the golden circuit. Jakob Feldtkeller, Jan Richter-Brockmann, Pascal Sasdrich, and Tim Güneysu

| Algorithm | 1: FINI-secure | correction gadget. |

|-----------|----------------|--------------------|

|-----------|----------------|--------------------|

1 function Correct<sub>FINI</sub>  $(a^0, ..., a^{n-1})$ : Require: n = 2k + 12 for  $\ell = 0$  to n - 1 do 3  $\ b^\ell \leftarrow maj(a^0, ..., a^{n-1})$ 4 return  $b^0, ..., b^{n-1}$

(ii) There exists a decoding gadget G<sup>D</sup>, such that given an input with at most k faulty redundancy domains and an abort signal, G<sup>D</sup> either aborts or outputs a correct result.

# 3.1 FINI Security and Composition

FINI formalizes the intuitive security and compositional properties of replication codes. Here, the main argument for fault security comes from the fact that at most k redundancy domains can be manipulated while up to k manipulated redundancy domains can be detected or corrected by the corresponding decoding function.

## THEOREM 3.3. A k-FINI gadget is k-fault secure.

The proof is given in Appendix A. Now we argue that an arbitrary composition of FINI gadgets results in a (larger) FINI gadget. Again, this follows from the properties of replication codes, which introduce a natural isolation of different replications, i.e., a fault injected to one redundancy domain cannot propagate to another redundancy domain. This ensures that the upper bound of faulty redundancy domains remains unchanged after composition. Again we give a formal proof of this statement in Appendix A.

THEOREM 3.4. The composition of two k-FINI gadgets is k-FINI.

REMARK 1. The connection of gadgets has do be consistent, i.e., redundancy domain  $\ell$  of a gadget is connected only to redundancy domain  $\ell$  of subsequent gadgets. However, we can permute the index of domains when necessary.

#### 3.2 FINI Gadgets

The construction of FINI gadgets for combinational gates follows a simple method: replication of the gate. By applying the compositional property of Theorem 3.4, the construction method can be generalized to all combinational or sequential circuits (which also includes the simple case of a single gate).

THEOREM 3.5. The (k+1)-times replication of any circuit is k-FINI.

The proof is given in Appendix A. In Theorem 3.5 we instantiate the number of replications with k + 1, which is the minimum number required for fault detection via comparison. It is trivial to see that the same claim is true for implementations with more then k + 1 replications, as the comparison still detects faulty values. Similar, when using at least 2k + 1 replications, we can use a majority function as decoding gadget additionally resulting in error correction.

The only gadgets that cannot be trivially constructed according to Theorem 3.5 are gadgets that combine different redundancy domains. The most prominent examples of this category are detection and correction modules. Here, the logic for detection/correction needs to be replicated for each redundancy domain, such that faults

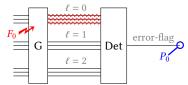

Figure 2. Insecure fault propagation in combined attack model. If all shares within one redundancy domain are faulty with a known biased distribution then the error flag indicates whether the faults represent a valid guess of the shares.

injected into this logic only affect one redundancy domain at the output [1, 41]. We show an example for this in Algorithm 1 considering a correction module<sup>4</sup>.

# 4 Combined-Isolating Non-Interference

Combining both PINI and FINI is an obvious step to construct a composability notation for CA that is based on the isolation of domains. However, due to reciprocal effects and the dual nature of faults, which can both manipulate internal values and serve as a probe [12, 43], it is insufficient to isolate faults in redundancy domains (FINI) and probes in share domains (PINI) and a more complex notion is required. Those reciprocal effects can be easily seen when considering any HPC gadget where some randomness is faulted to a known value which nullifies the provided security guarantees. Similarly, with known faults, identifying correct guesses of shares becomes possible. Consider the example illustrated in Figure 2, where a gadget G with three shares and three redundancy domains is connected to a detection module. Further, assume that all shares in the first redundancy domain are faulty with a known and biased distribution (e.g., set/reset), representing an implicit guess on those shares. Then the error flag leaks information about all faulted shares, since it indicates the correctness of the guess, regardless of how the detection module is realized.

As a result the domain definition for fault propagation in the CA setting has to be more restrictive than given pure fault attacks. In particular, faults are restricted to propagate only in the combination of both share and redundancy domain. This ensures that a fault can leak at most one share domain even in circumstances where it can be used to learn values (similar to placing a probe).

Definition 4.1 (Shared Redundancy Domain). The Shared Redundancy Domain (SRD)  $(i, \ell)$  of a replicated and shared circuit is defined by all gates and wires with share index i and replication index  $\ell$ .

Here, in contrast to faults, it is not necessary to further restrict the propagation of probes. On the contrary, as all replicated wires carry the same value, it is sufficient to probe one of those wires to learn all those values. Hence, each share domain (Definition 2.1) consists of multiple SRDs.

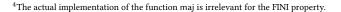

We now define CINI as a composability property for combined security, where faults are isolated within SRDs and probes within share domains. That is, for every set of probes and faults the number of input share domains  $A_c$  can learn is bounded by the sum of the cardinality and position of the probes and faults, and the number

Replication Index  $\ell = 0$   $4^{3^2}$   $f_1$   $f_2$   $\ell = n - 1$   $4^{3^2}$   $\ell = n - 1$   $4^{3^2}$   $\ell = n - 1$   $4^{3^2}$   $\ell = n - 1$  $4^{3^2}$

Figure 3. Propagation of probes and faults in the CINI context. While probes leak entire share domains (all inputs with same share index), faults are restricted to influence at most one output SRD. Further, probes at outputs restrict the leaked share domain of the inputs to be the same. Similar, input faults are restricted to affect the same SRD at the output.

of faulty output SRDs is bounded by the cardinality and position of the faults, as visualized in Figure 3.

Definition 4.2 (Combined-Isolating Non-Interference). A gadget G is (d, k)-CINI iff for any set  $\mathcal{F}_1$  of  $k_1$  faulty SRDs, every set of  $k_2$  faults injected in gates of G, any set of  $d_1$  probes placed on intermediate values, and any set  $\mathcal{S}_2$  of  $d_2$  share domains, such that  $k_1 + k_2 \leq k$  and  $d_1 + d_2 + k_1 + k_2 \leq d$ , there exists a set  $\mathcal{F}_2$  of at most  $k_2$  SRDs and a set  $\mathcal{S}_1$  of at most  $d_1 + k_2$  share domains such that the following holds:

| Correctness: | The gadget either aborts or gives an output where                   |

|--------------|---------------------------------------------------------------------|

|              | all values, except those belonging to the SRDs $\mathcal{F}_1 \cup$ |

|              | $\mathcal{F}_2$ , are equal to the golden circuit, and there exists |

|              | a decoding gadget G <sup>D</sup> , such that given an input         |

|              | with at most $k$ faulty SRDs and an abort signal, $G^{D}$           |

|              | either aborts or outputs a correct result.                          |

| Privacy:     | The abort signal, the outputs of the share domains                  |

in  $S_2$ , the outputs violating the independence property of Boolean sharing, and the probes can be simulated with the inputs of the share domains in  $S_1 \cup S_2$ and knowledge of the faults both injected and on inputs in  $\mathcal{F}_1$ .

Please note, that CINI restricts the number of probes and faults together to be smaller than or equal to the order of probing security *d*. Hence, the order of fault security is always dependent on the order of probing security. In Section 5 we show how to achieve independence between fault and probing security.

## 4.1 CINI Security and Composition

Intuitively, the security of CINI comes from the fact, that there are always more share domains than the amount of probes and faults an adversary is allowed to place or inject. This is sufficient for security, as the isolation of probe and fault propagation within share domains and SRDs, respectively, restricts the possible leakage.

THEOREM 4.3. A (d, k)-CINI gadget is (d, k)-combined secure.

PROOF. Let G be a (d, k)-CINI gadget, with notation as in Definition 4.2. Further, let G<sup>D</sup> be a gadget realizing a decoding function D,

such that, given an input with at most k faults and an abort signal,  $G^{D}$  either aborts or outputs a correct result.

*Correctness:* By definition of CINI, G either aborts or outputs a result where all values are correct, except for those belonging to the SRDs  $\mathcal{F}_1 \cup \mathcal{F}_2$ . Further, by definition it holds that  $|\mathcal{F}_1 \cup \mathcal{F}_2| \le k_1 + k_2 \le k$ . Hence, the concatenation  $G^D(G(\cdot))$  either aborts or outputs a correct result.

*Privacy*: By definition of CINI the abort signal, the outputs of the share domains in  $S_2$ , and the probes can be simulated with the inputs in the share domains in  $S_1 \cup S_2$  and knowledge of the faults injected and on inputs in  $\mathcal{F}_1$ . Knowledge of the input faults does not reveal any additional information about the corresponding nonfaulted value, as only distributions are leaked (a fault with biased distribution erases the original value and non-biased faults leak nothing on its own). It holds that  $|S_1 \cup S_2| \leq d_1 + d_2 + k_2 \leq d < s$ . Therefore, due to the independence of the input encoding of the shares, the inputs in the share domains  $S_1 \cup S_2$  are independent of any sensitive signals.

We continue by showing that the arbitrary combination of CINI gadgets again construct a CINI gadget, as long as there is no loop in the design. This is trivially true for all combinational circuits. Sequential logic with potential loops can be reduced to this case by unrolling the design for the analysis, which is valid when transitional leakage [20] is not considered (as for this work).

THEOREM 4.4. The loop-free composition of two (d, k)-CINI gadgets is (d, k)-CINI.

**PROOF.** Let  $G_1$  and  $G_2$  be arbitrary (d, k)-CINI gadgets and  $G_3$  an arbitrary composition of  $G_1$  and  $G_2$ , such that there is no loop within  $G_3$ . Without loss of generality, we say no output of  $G_2$  is connected to an input of  $G_1$  (as there is no loop).

Let  $\mathcal{F}_1$  be a set of  $k_1$  SRDs with faulty inputs to G<sub>3</sub> and  $\mathcal{S}_2$  a set of  $d_2$  share domains with probed outputs of G<sub>3</sub>. Further, let there be  $k_2$  faults injected in gates of G<sub>3</sub>, of which  $k_2^1$  target gates in G<sub>1</sub> and  $k_2^2$  target gates in G<sub>2</sub>. In addition, assume  $d_1$  probes placed on wires in G<sub>3</sub>, of which  $d_1^1$  target wires in G<sub>1</sub> and  $d_1^2$  target wires in G<sub>2</sub>. As the gadgets G<sub>1</sub> and G<sub>2</sub> are disjoint it holds that  $k_2^1 + k_2^2 = k_2$  and  $d_1^1 + d_1^2 = d_2$ . We chose  $d_1, d_2, k_1$ , and  $k_2$  such that  $k_1 + k_2 \leq k$  and  $d_1 + d_2 + k_1 + k_2 \leq d$ . We first prove correctness and then privacy of G<sub>3</sub>.

*Correctness:* As no output of  $G_2$  is connected to an input of  $G_1$ , the set  $\mathcal{F}_1$  contains all SRDs with faulty inputs to  $G_1$  and there are  $k_2^1$  faults injected in gates of  $G_1$ . It holds that  $k_1 + k_2^1 \le k_1 + k_2 \le k$ . Hence, with CINI of  $G_1$  it follows that  $G_1$  either aborts or there exists a set  $\mathcal{F}_2^1$  of  $k_2^1$  SRDs, such that at most the outputs belonging to the SRDs  $\mathcal{F}_1 \cup \mathcal{F}_2^1$  are faulty.

Outputs of G<sub>1</sub> can be connected to inputs of G<sub>2</sub>, thus, the set of SRDs with possible faulty inputs to G<sub>2</sub> is the set  $\mathcal{F}_1 \cup \mathcal{F}_2^1$ . Further, there are  $k_2^2$  faults injected in gates of G<sub>2</sub>. It holds that  $k_1 + k_2^1 + k_2^2 = k_1 + k_2 \leq k$ . Hence, with CINI of G<sub>2</sub> it follows that G<sub>2</sub> either aborts or there exists a set  $\mathcal{F}_2^2$  of  $k_2^2$  SRDs, such that at most the outputs belonging to the SRDs  $\mathcal{F}_1 \cup \mathcal{F}_2^1 \cup \mathcal{F}_2^2$  are faulty.

The outputs of  $G_3$  can be both outputs of  $G_1$  and  $G_2$  and, therefore, at most the SRDs in  $\mathcal{F}_1 \cup \mathcal{F}_2^1 \cup \mathcal{F}_2^2$  carry faulty outputs or  $G_3$  aborts (if  $G_1$  or  $G_2$  abort). It holds that  $|\mathcal{F}_1 \cup \mathcal{F}_2^1 \cup \mathcal{F}_2^2| \leq$   $k_1 + k_2^1 + k_2^2 = k_1 + k_2 \le k$ . In addition, as G<sub>1</sub> and G<sub>2</sub> are (d, k)-CINI there exists a decoding gadget G<sup>D</sup>, such that given an input with at most *k* faulty SRDs and an abort signal, G<sup>D</sup> either aborts or outputs a correct result. From this follows correction of G<sub>3</sub>.

*Privacy*: As all outputs of G<sub>2</sub> are outputs of G<sub>3</sub> the set of probed output share domains of G<sub>2</sub> is S<sub>2</sub>. In addition, there are  $d_1^2$  probes placed on wires in G<sub>2</sub>,  $k_1 + k_2^1$  SRDs with faulty inputs, and  $k_2^2$  faults injected to G<sub>2</sub>. It holds that  $d_1^2 + d_2 + k_1 + k_2^1 + k_2^2 \le d_1 + d_2 + k_1 + k_2 \le d$ . Hence, with CINI of G<sub>2</sub> there exists a set  $S_1^2$  of  $d_1^2 + k_2^2$  share domains, such that the abort signal of G<sub>2</sub>, the outputs of G<sub>2</sub> belonging to S<sub>2</sub>, and the probes placed on wires in G<sub>2</sub> can be simulated with the inputs of G<sub>2</sub> belonging to the share domains  $S_1^2 \cup S_2$  and knowledge of the faults. Denote this simulator with S<sub>2</sub>. Please note, the knowledge of the faults at inputs to G<sub>2</sub> can be derived by fault propagation.

Outputs of  $G_1$  can be connected to inputs of  $G_2$  and a simulator for  $G_1$  needs to simulate all inputs of  $G_2$  required for  $S_2$ . Hence, the set of probed output share domains is  $S_1^2 \cup S_2$ . In addition, there are  $d_1^1$  probes placed on wires within  $G_1$ ,  $k_1$  SRDs with faulty inputs, and  $k_2^1$  faults injected to  $G_1$ . It holds that  $d_1^1 + d_1^2 + k_2^2 + d_2 + k_1 + k_2^1 =$  $d_1 + d_2 + k_1 + k_2 \leq d$ . Hence, with CINI of  $G_1$  there exists a set  $S_1^1$  of  $d_1^1 + k_2^1$  share domains, such that the abort signal of  $G_1$ , the outputs of  $G_1$  belonging to the share domains  $S_1^2 \cup S_2$ , and the probes placed on wires in  $G_1$  can be simulated with inputs of  $G_1$  in the share domains  $S_1^1 \cup S_1^2 \cup S_2$  and knowledge of the faults. We call this simulator  $S_1$ .

Together,  $S_1$  and  $S_2$  build a simulator such that the abort signal of  $G_3$ , the outputs of  $G_3$  belonging to the share domains in  $S_2$ , and the probes placed on wires in  $G_3$  can be simulated with the inputs of  $G_3$  belonging to the share domains in  $S_1^1 \cup S_1^2 \cup S_2$  and knowledge of the faults. It holds that  $|S_1^1 \cup S_1^2| \le d_1^1 + k_2^1 + d_1^2 + k_2^2 = d_1 + k_2$ .  $\Box$

#### 4.2 CINI Gadgets

One explicit goal of CINI is the trivial implementation of linear functions, e.g., addition, by simply sharing and replicating them. This is possible, as replication and Boolean sharing are linear themselves.

THEOREM 4.5. An implementation with d + 1 shares and (k + 1)times replication of a linear function is (d, k)-CINI in the glitch-robust probing model.

PROOF. Let G be the trivial gadget implementation of a linear function, i.e., the linear function is replicated both in the dimension of fault and share domains. Then it holds that each SRD is functionally separated.

*Correctness:* Due to the separation of SRDs, a fault in a SRD  $(i, \ell)$  can only propagate to an output in the SRD  $(i, \ell)$ . Hence,  $\mathcal{F}_2$  is the union of all SRDs a fault is injected in and it always holds that  $|\mathcal{F}_2| \leq k_2$ . As input faults can also only propagate within the same SRD, all outputs are correct except for those belonging to the SRDs  $\mathcal{F}_1 \cup \mathcal{F}_2$ . In addition, as there are k + 1 replications up to k faults can be detected by a equivalence check and, hence, a decoding gadget exists.

*Privacy:* Due to the separation of SRDs, each probe and output is only dependent on inputs of one SRD. As a SRD is a part of a share domain, the same is true for share domains. Hence, the outputs belonging to  $S_2$  can be simulated with the inputs belonging to  $S_2$ .

Figure 4. CINI requires all values crossing a domain boundary to be both correct and blinded.

Similarly, the probes can be simulated with the inputs belonging to the probed share domain. Hence, the simulator requires the inputs in  $S_1 \cup S_2$  and knowledge of the faults, where  $S_1$  is the set of probed share domains (it trivially holds that  $|S_1| \le d_1 \le d_1 + k_2$ ).

Implementing non-linear functions, e.g., multiplication, is more complex since values need to be combined across share-domain boundaries. Hence, similar to PINI, we have to ensure that the masks of such terms are refreshed beforehand. In addition, a faulty value is not allowed to cross SRD boundaries, which requires fault detection or correction for terms combining different share domains. Both principles are illustrated in Figure 4. As no fault is allowed to affect more than one SRD, each intermediate value is only allowed to be used in one SRD (except for generated randomness), requiring detection/correction within gadgets for values that are used across SRD boundaries.

Based on those design principles, we can extend the refresh-thenmultiply technique, used in the HPC<sub>1</sub> gadget [9] (originally PINI), to a refresh-and-correct-then-multiply technique to construct a CINI gadget (given in Algorithm 2). The major difference to the original HPC<sub>1</sub> gadget is the replication of the logic and the majority function for correction in Line 12. Also, and in contrast to HPC<sub>1</sub>, all intermediate values are only allowed to be used once (see Remark 3). In the following we prove CINI for the derived gadget.

THEOREM 4.6. The gadget HPC<sup>C</sup><sub>1</sub> as defined in Algorithm 2 with a register-free majority function is (d, k)-CINI in the glitch-robust probing model.

PROOF. Let  $\mathcal{F}_1$  be a set of  $k_1$  SRDs and  $\mathcal{S}_2$  a set of  $d_2$  share domains. Further, let there be  $k_2$  faults injected to the gates of the gadget and  $d_1$  probes placed on internal wires. Without loss of generality, we restrict the probes to only capture  $v_{i,j}^{\ell}$ ,  $w_i^{\ell}$ ,  $z_{i,j}^{\ell}$ , and  $c_i^{\ell}$  as other glitch-extended probes are less powerful. In particular, all probes within the majority function (Line 12) are less powerful than probes on  $v_{i,j}^{\ell}$  as the majority function is implemented register free. We first show correctness and then privacy of the gadget.

*Correctness:* For correctness, faults in a random value  $r_{i,j}$  can be ignored, as otherwise the correctness without any fault would depend on the concrete value of  $r_{i,j}$  and the gadget would output a wrong result half of the time. By construction of the gadget each value with three indices  $i, j, \text{ and } \ell$  only influences the output  $c_i^\ell$ and, hence, faults injected to those values can only influence the SRD  $(i, \ell)$ . This is true for  $v_{i,j}^\ell, z_{i,j}^\ell$ , and each intermediate value in maj $(\tilde{v}_i^0 \dots \tilde{v}_i^{n-1})$  (regardless of the implementation of the majority

| Alg  | <b>gorithm 2:</b> HPC <sup>C</sup> <sub>1</sub> : CINI multiplication                                                         |  |  |  |  |  |  |  |  |

|------|-------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| (wit | h difference to $HPC_1$ highlighted).                                                                                         |  |  |  |  |  |  |  |  |

| 1 fu | $P_{1} = (a_{0}^{0}, \dots, a_{d}^{n}, b_{0}^{0}, \dots, b_{d}^{n}):$                                                         |  |  |  |  |  |  |  |  |

|      | Require: $n = 2\kappa + 1$                                                                                                    |  |  |  |  |  |  |  |  |

|      | <b>Require:</b> $a_i^{\ell} = a_i^{\ell'}$ and $b_i^{\ell} = b_i^{\ell'}$ for $0 \le \ell, \ell' \le n, 0 \le i \le d$        |  |  |  |  |  |  |  |  |

|      | <b>Require:</b> $\sum_{j=0}^{d} a_{j}^{\ell} = a$ and $\sum_{j=0}^{d} b_{j}^{\ell} = b$ for $0 \leq \ell \leq n$              |  |  |  |  |  |  |  |  |

|      | // Initialize randomness                                                                                                      |  |  |  |  |  |  |  |  |

| 2    | for $i = 0$ to $d$ do                                                                                                         |  |  |  |  |  |  |  |  |

| 3    | <b>for</b> $j = i + 1$ to $d$ <b>do</b>                                                                                       |  |  |  |  |  |  |  |  |

| 4    | $\tilde{r}_{i,j} \stackrel{\$}{\leftarrow} \mathbb{F}_2; \tilde{r}_{j,i} \leftarrow \tilde{r}_{i,j}$                          |  |  |  |  |  |  |  |  |

| 5    | $\left[\begin{array}{c} & \\ & r_{i,j} \stackrel{\$}{\leftarrow} \mathbb{F}_2; r_{j,i} \leftarrow r_{i,j} \end{array}\right]$ |  |  |  |  |  |  |  |  |

|      | // Refreshing                                                                                                                 |  |  |  |  |  |  |  |  |

| 6    | for $\ell = 0$ to $n - 1$ do                                                                                                  |  |  |  |  |  |  |  |  |

| 7    | for $j = 0$ to $d$ do                                                                                                         |  |  |  |  |  |  |  |  |

| 8    | $\tilde{v}_j^{\ell} \leftarrow b_j^{\ell} + \sum_{i=0, i \neq j}^d \tilde{r}_{i,j}$                                           |  |  |  |  |  |  |  |  |

|      | // Correction                                                                                                                 |  |  |  |  |  |  |  |  |

| 9    | for $\ell = 0$ to $n - 1$ do                                                                                                  |  |  |  |  |  |  |  |  |

| 10   | for $i = 0$ to d do                                                                                                           |  |  |  |  |  |  |  |  |

| 11   | <b>for</b> $j = 0$ to d <b>do</b>                                                                                             |  |  |  |  |  |  |  |  |

| 12   | $\left[ v_{i,j}^{\ell} \leftarrow maj(\tilde{v}_i^0 \dots \tilde{v}_i^{n-1}) \right]$                                         |  |  |  |  |  |  |  |  |

|      | // Multiplication                                                                                                             |  |  |  |  |  |  |  |  |

| 13   | for $\ell = 0$ to $n - 1$ do                                                                                                  |  |  |  |  |  |  |  |  |

| 14   | for $i = 0$ to d do                                                                                                           |  |  |  |  |  |  |  |  |

| 15   | $w_i^{\ell} \leftarrow a_i^{\ell} \cdot \operatorname{Reg}[v_{i,i}^{\ell}]$                                                   |  |  |  |  |  |  |  |  |

| 16   | <b>for</b> $j = 0$ to $d, j \neq i$ <b>do</b>                                                                                 |  |  |  |  |  |  |  |  |

| 17   |                                                                                                                               |  |  |  |  |  |  |  |  |

| 18   | $c_i^{\ell} \leftarrow \operatorname{Reg}[w_i^{\ell}] + \sum_{j=0; j \neq i}^d \operatorname{Reg}[z_{i,j}^{\ell}]$            |  |  |  |  |  |  |  |  |

|      | <b>Ensures:</b> $c_i^{\ell} = c_i^{\ell'}$ for $0 \leq \ell, \ell' \leq n, 0 \leq i \leq d$                                   |  |  |  |  |  |  |  |  |

|      | <b>Ensures:</b> $\sum_{i=0}^{d} c_i^{\ell} = a \cdot b \text{ for } 0 \leq \ell \leq n$                                       |  |  |  |  |  |  |  |  |

| 19   | return $c_0^0, \ldots, c_d^n$                                                                                                 |  |  |  |  |  |  |  |  |

|      |                                                                                                                               |  |  |  |  |  |  |  |  |

as it is true for  $v_{i,j}^{\ell}$ ). Similar, the values  $a_i^{\ell}$ ,  $w_i^{\ell}$ , and  $c_i^{\ell}$  are only used for the computation of  $c_i^{\ell}$  and can only influence the SRD  $(i, \ell)$ . The only values influencing more than one SRD are  $b_j^{\ell}$  and  $\tilde{v}_j^{\ell}$ . However at most k of those values can be faulted and, hence, are corrected by the majority function. Therefore, the only way how a fault in  $b_j^{\ell}$  or  $\tilde{v}_j^{\ell}$  can have an impact on a SRD  $(i, \ell)$ , with  $i \neq j$ , is by manipulating the computation of  $v_{i,j}^{\ell}$  in which case there is an additional fault for the SRD  $(i, \ell)$ .

In conclusion, each fault in a SRD at the input can cause a fault at the same SRD at the output. In addition, the set  $\mathcal{F}_2$  is the union of all SRDs  $(i, \ell)$  such that the computation of an intermediate value containing the indices *i* and  $\ell$  was faulted. Then it holds that  $|\mathcal{F}_2| \leq k_2$  as each faulty intermediate value can influence at most one SRD. As there are 2k+1 repetitions of each output, the decoding gadget G<sup>D</sup> can be constructed as a majority function.

*Privacy:* Algorithm 3, given a set of probes  $\mathcal{P}$ , a set of share domains  $\mathcal{S}_2$ , and a set of faults  $\mathcal{F}$  returns a set of share domains  $\mathcal{X}$  required for the simulation of the probes, the outputs belonging to  $\mathcal{S}_2$ , and the outputs that violate the independence property of

**Algorithm 3:** Share-Domain Chooser for the Simulator of  $HPC_1^C$ .

| 1 ft | unction DomainChooser <sup>HPC<sup>C</sup></sup> $(\mathcal{P}, \mathcal{S}_2, \mathcal{F}_2)$ :               |  |  |  |  |  |  |  |  |

|------|----------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 2    | $\mathcal{X} \leftarrow \emptyset$                                                                             |  |  |  |  |  |  |  |  |

| 3    | for $\ell = 0$ to $n - 1$ do                                                                                   |  |  |  |  |  |  |  |  |

| 4    | for $i = 0$ to d do                                                                                            |  |  |  |  |  |  |  |  |

| 5    | if $w_i^\ell$ or $c_i^\ell$ is probed or $i \in S_2$ then                                                      |  |  |  |  |  |  |  |  |

| 6    | $\left[\begin{array}{c}\mathcal{X}\leftarrow\mathcal{X}\cup\{i\}\end{array}\right]$                            |  |  |  |  |  |  |  |  |

| 7    | <b>for</b> $j = 0$ to $d, j \neq i$ <b>do</b>                                                                  |  |  |  |  |  |  |  |  |

| 8    | if $z_{i,j}^{\ell}$ is probed then                                                                             |  |  |  |  |  |  |  |  |

| 9    | $\left\lfloor \begin{array}{c} \mathcal{X} \leftarrow \mathcal{X} \cup \{i\} \end{array}\right]$               |  |  |  |  |  |  |  |  |

| 10   | <b>if</b> $v_{i,j}$ is probed $\land$ $(i \in \mathcal{X} \text{ or } j \in \mathcal{X})$ <b>then</b>          |  |  |  |  |  |  |  |  |

| 11   | $\left[\begin{array}{c} \mathcal{X} \leftarrow \mathcal{X} \cup \{i, j\} \right]$                              |  |  |  |  |  |  |  |  |

| 12   | else if $v_{i,j}^{\ell}$ is probed then                                                                        |  |  |  |  |  |  |  |  |

| 13   | $\left[\begin{array}{c}\mathcal{X}\leftarrow\mathcal{X}\cup\{i\}\end{array}\right]$                            |  |  |  |  |  |  |  |  |

| 14   | <b>if</b> $\tilde{r}_{i,j}$ is faulted $\land$ $(i \in \mathcal{X} \text{ or } j \in \mathcal{X})$ <b>then</b> |  |  |  |  |  |  |  |  |

| 15   | $\left\lfloor \begin{array}{c} \mathcal{X} \leftarrow \mathcal{X} \cup \{i, j\} \end{array}\right.$            |  |  |  |  |  |  |  |  |

| 16   | <b>if</b> $\forall j : r_{i,j}$ is faulted <b>then</b>                                                         |  |  |  |  |  |  |  |  |

| 17   | $\left[ \begin{array}{c} \mathcal{X} \leftarrow \mathcal{X} \cup \{i\} \end{array} \right]$                    |  |  |  |  |  |  |  |  |

| 18   | $\_$ return $\mathcal{X}$                                                                                      |  |  |  |  |  |  |  |  |

Boolean sharing. We set  $S_1 \leftarrow \mathcal{X} \setminus S_2$ . Then all required intermediate values and outputs (with manipulation according to faults) can be computed exactly as in Algorithm 2 using the inputs belonging to the share domains in  $\mathcal{X}$ , except for some  $\tilde{v}_i^{\ell}$ .

First, we see that Algorithm 3 adds at most one share domain per probe, share domain in  $S_2$ , and internal fault. Therefore, it always holds that  $|S_1| \leq d_1 + k_2$ . We continue, by showing that the share domains in  $\mathcal{X}$  and knowledge of the faults are sufficient to simulate the probes in  $\mathcal{P}$ , the outputs in  $S_2$ , and the outputs that violate the independence property of Boolean sharing. (Please note, that Algorithm 2 has no abort signal).

We define a simulator that computes all required values exactly as defined in Algorithm 2 (required randomness is generated), except for  $\tilde{v}_j^{\ell}$ . For this value, we distinguish between the following cases: (i) if  $j \in \mathcal{X}$  compute  $\tilde{v}_j^{\ell}$  according to Algorithm 2. (ii) if  $j \notin \mathcal{X}$  then draw a fresh random value r and set  $\forall \ell : \tilde{v}_j^{\ell} \leftarrow r$ . Afterwards, all values are manipulated according to the given faults.

Please note, if some  $\tilde{v}_j^{\ell}$  is replaced by randomness then there is no fault injected in  $\tilde{r}_{i,j}$ , since then  $j \notin \mathcal{X}$  and there is a probe dependent on  $\tilde{v}_j^{\ell}$ . Faults in  $b_j^{\ell'}$  or  $\tilde{v}_j^{\ell'}$ , for  $\forall \ell'$ , have no impact on  $v_{i,j}^{\ell}$ , since there can be at most k faults and there are at least k + 1correct values. All other faults are either not observable by the probes or the faulted values are used exactly as in Algorithm 2 and the simulator can do the same manipulation as the fault in the gadget.

This simulator results in the same output distribution as the probes for the following reason: All values are computed exactly as in the gadget (Algorithm 2) except for  $\tilde{v}_j^{\ell}$  in Case (ii). In this case, we argue that  $\tilde{r}_{i,j}$  is only observable through one intermediate value and, hence, the simulation is correct. This is true for the following reason: Assume some  $\tilde{v}_i^{\ell}$  is replaced by some randomness.

This means  $j \notin \mathcal{X}$  and some value dependent on  $\tilde{v}_j^{\ell}$  is probed (i.e.,  $\tilde{v}_j^{\ell}, v_{i,j}^{\ell}, w_i^{\ell}, z_{i,j}^{\ell}$ , or  $c_i^{\ell}$ ). From  $j \notin \mathcal{X}$  follows that there is no probe placed on any  $\tilde{v}_j^{\ell'}, v_{j,i}^{\ell'}, w_j^{\ell'}, z_{j,i}^{\ell'}$ , or  $c_j^{\ell'}$ , for  $\forall i, \ell'$  and, hence,  $\tilde{r}_{i,j}$  is only observable through  $\tilde{v}_j^{\ell}$  and the simulation is correct.

Note that the output of Algorithm 2 is always a valid Boolean sharing due to the mask refreshing in Line 17 except when all random values  $r_{i,j}$ ,  $\forall j$  are faulted. In this case  $c_i^{\ell}$ ,  $\forall \ell$  violate the independence property, however, can be simulated as  $i \in \mathcal{X}$ . With the given simulator follows privacy of Algorithm 2.

REMARK 2. We emphasize that faults targeted at randomness count as internal faults, i.e., contribute to  $k_2$ .

REMARK 3. For security it is essential, that the majority function (Line 12) is computed for each SRD individually.

REMARK 4. For security it is also essential that the mask refreshing in Line 8 is done one by one, i.e.,  $\tilde{v}_i^{\ell} \leftarrow (((b_j^{\ell} + r_{j,0}) + ...) + r_{j,d}).$

REMARK 5. The assumption that the majority function is implemented register free is done for simplicity and readability of the proof. In fact, when there are register in maj then probes on  $v_{i,j}^{\ell}$  and potential probes within maj are strictly less powerful as a probe on  $v_{i,j}^{\ell}$  without registers in maj.

As mentioned, the security of  $HPC_2$  [9] relies on the fact that cross-domain leakage is prevented by some  $r_{i,j}$  that is observable in only one of  $(a_i+1) \cdot r_{i,j}$  or  $a_i \cdot (b_j+r_{i,j})$  and, hence, ensures a proper masking of  $b_i$  (if  $b_i$  is not an input to the simulator). However, this only holds because both terms get the same  $a_i$  as input and one of them is using the negated form. Now, when replicating the gadget there exist some terms  $(a_i^0 + 1) \cdot r_{i,j}$  and  $a_i^1 \cdot (b_j^1 + r_{i,j})$  such that  $a_i^{\ell}$  comes from different replications. Hence, by faulting  $a_i^0$ or  $a_i^1$  it is possible to force both  $(a_i^0 + 1)$  and  $a_i^1$  to be true and, hence,  $r_{i,j}$  is observable in both corresponding terms. However, in a combined attack setting this flaw cannot be exploited for  $d \leq 3$  and  $k \leq 3$ , as the corresponding attack requires one fault (at  $a_i^0$ ) and two probes (at  $c_i^0$  and  $c_i^1$ ). Hence, for the remaining cases, we describe an HPC2-based CINI gadget in Algorithm 4 and prove the security in Section 7.1 via a tool-based analysis. As HPC3 [27] also depends on the masked shares multiplication trick it suffers from the same limitations. Interestingly, HPC<sup>C</sup><sub>2</sub> achieves a tight realization of CINI, meaning that a well placed fault indeed reduces the order of probing security by one (cf. Section 7.3). In contrast, HPC<sup>C</sup><sub>1</sub> actually achieves a higher security level than strictly required for some orders, e.g., the (2, 2)-HPC<sub>1</sub><sup>C</sup> gadget is also (2, 1)-CINI<sub>ind</sub> and (1, 2)-CINI<sub>ind</sub> (see Section 5). This indicates some overhead in terms of randomness for  $HPC_1^{\dot{C}}$ .

While potentially more efficient, gadgets based on detection have to avoid SCA leakage caused by fault propagation and construct a SCA-secure tree of detection flags. Both are non-trivial problems that we leave for future work.

# 5 Independent Combined-Isolating Non-Interference

The presented CINI definition requires that the number of probes and faults together is smaller than or equal to the order of probing

**Algorithm 4:** HPC<sub>2</sub><sup>C</sup>: CINI multiplication for  $d \le 2, k \le 2$  (with difference to HPC<sub>2</sub> highlighted).

```

1 function HPC<sub>2</sub><sup>C</sup> (a_0^0, ..., a_d^n, b_0^0, ..., b_d^n):

Require: d \le 2, k \le 2, n = 2k + 1

Require: a_i^{\ell} = a_i^{\ell'} and b_i^{\ell} = b_i^{\ell'} for 0 \le \ell, \ell' \le n, 0 \le i \le d

Require: \sum_{j=0}^d a_j^{\ell} = a and \sum_{j=0}^d b_j^{\ell} = b for 0 \le \ell \le n

// Initialize randomness

for i = 0 to d do

2

for j = i + 1 to d do

3

r_{i,j} \stackrel{\$}{\leftarrow} \mathbb{F}_2; r_{j,i} \leftarrow r_{i,j}

4

// Masking

for \ell = 0 to n - 1 do

5

for i = 0 to d do

6

for j = 0 to d, j \neq i do

7

\tilde{v}_{i,j}^{\ell} \leftarrow b_j^{\ell} + r_{i,j}

8

for \ell = 0 to n - 1 do

9

// Correction and partial products

for i = 0 to d do

10

w_i^{\ell} \leftarrow a_i^{\ell} \cdot \operatorname{Reg}[b_i^{\ell}]

11

for j = 0 to d, j \neq i do

12

u_{i,j}^{\ell} \leftarrow (a_i^{\ell} + 1) \cdot \operatorname{Reg}[r_{i,j}]

13

\begin{bmatrix} v_{i,j}^{\ell} \leftarrow \operatorname{maj}(\tilde{v}_{i,j}^{0} \dots \tilde{v}_{i,j}^{n-1}) \\ z_{i,j}^{\ell} \leftarrow a_{i}^{\ell} \cdot \operatorname{Reg}[v_{i,j}^{\ell}] \end{bmatrix}

14

15

// Reduction

for i = 0 to d do

16

c_i^{\ell} \leftarrow \operatorname{Reg}[w_i^{\ell}] + \sum_{j=0, j \neq i}^d (\operatorname{Reg}[u_{i,j}^{\ell}] + \operatorname{Reg}[z_{i,j}^{\ell}])

17

Ensures: c_i^{\ell} = c_i^{\ell'} for 0 \leq \ell, \ell' \leq n, 0 \leq i \leq d

18

Ensures: \sum_{j=0}^{d} c_j^{\ell} = a \cdot b for 0 \leq \ell \leq n

return c_0^0, \ldots, c_d^n

19

```

security *d*. This means that it is of course possible to build a gadget that can resist d' probes together with k' faults for arbitrary d', and k', however, it requires an implementation with at least d' + k' + 1 shares and is, hence, effectively a (d' + k', k') gadget. This results in a significant overhead in the number of shares and in consequence also in other metrics.

To avoid this overhead, we define  $\text{CINI}_{\text{ind}}$ , a composability notion for CA security where the order of probing and fault security can be selected independently. This independence requires only a small change compared to the CINI definition, namely that we now have  $d_1 + d_2 \le d$  instead of  $d_1 + d_2 + k_1 + k_2 \le d$ , separating the number of injected faults and the order of probing security.

Definition 5.1 (Independent Combined-Isolating Non-Interference). A gadget G is (d, k)-CINI<sub>ind</sub> iff for any set  $\mathcal{F}_1$  of  $k_1$  faulty SRDs, every set of  $k_2$  faults injected in gates of G, any set of  $d_1$  probes placed on intermediate values, and any set  $S_2$  of  $d_2$  share domains, such that  $k_1 + k_2 \le k$  and  $d_1 + d_2 \le d$ , there exists a set  $\mathcal{F}_2$  of at most  $k_2$  SRDs and a set  $S_1$  of at most  $d_1$  share domains such that the following holds:

Correctness: The gadget either aborts or gives an output where all values, except those belonging to the SRDs  $\mathcal{F}_1 \cup \mathcal{F}_2$ , are equal to the golden circuit, and there exists

a decoding gadget  $G^{D}$ , such that given an input with at most k faulty SRDs,  $G^{D}$  outputs a correct result.

*Privacy:* The outputs of the share domains in  $S_2$  and the probes can be simulated with the inputs of the share domains in  $S_1 \cup S_2$  and knowledge of the faults both injected and on inputs in  $\mathcal{F}_1$ .

Please note, that in contrast to CINI the parameters for probing and fault security are now clearly separated. This also requires the use of correction countermeasures, as detection violates this separation [15]. To see this, assume an intermediate value that gets randomized by some randomness, i.e.,  $x_i^{\ell} + r$ , where a reset fault is injected on  $x_i^{\ell}$ . The detection then removes the *r* in some other fault domain  $\ell'$  and an appropriate probe leaks  $x_i$  (cf. Figure 5 in [35]).

# 5.1 CINI<sub>ind</sub> Security and Composition

The security and composition of  $\text{CINI}_{\text{ind}}$  relies on the same fundamental properties as for CINI, i.e., more domains than allowed attack points and isolation of probe and fault propagation within the respective domains.

THEOREM 5.2. A(d, k)-CINI<sub>ind</sub> gadget is (d, k)-combined secure.

THEOREM 5.3. The loop-free composition of two (d, k)-CINI<sub>ind</sub> gadgets is (d, k)-CINI<sub>ind</sub>.

The proofs of both theorems follow closely the argumentation for their CINI counterparts (Theorem 4.3 and Theorem 4.4), where for *privacy* aspects related to injected faults are removed. We, therefore, omit the proofs here and refer the interested reader to Appendix B for more details.

# 5.2 CINI ind Gadgets

One can observe that the provided CINI gadget for linear functions already adheres to the more restrictive CINI<sub>ind</sub> property. The reason is the natural isolation of each SRD when implementing the function for each share and replication individually.

THEOREM 5.4. An implementation with d + 1 shares and (2k + 1)times replication of a linear function is (d, k)-CINI<sub>ind</sub> in the glitchrobust probing model.

Again, the proof follows closely the argumentation from Theorem 4.5 and we refer the reader to Appendix B for details.

As with PINI and CINI, implementing a non-linear gadget is more complex and requires careful separation of probe and fault propagation. Of course, the same design principles as for CINI apply also for CINI<sub>ind</sub>, namely (i) the masking of values crossing share-domain boundaries need to be refreshed, and (ii) values crossing SRD boundaries need to be corrected. In addition CINI<sub>ind</sub> requires (iii) remasking is done with more than *k* random values. This ensures that an attacker cannot remove the randomness from a refreshed value.

Interestingly, increasing the amount of randomness is sufficient to make the CINI multiplication gadget CINI<sub>ind</sub> in the case of HPC<sup>C</sup><sub>1</sub>.

THEOREM 5.5. The gadget  $HPC_1^l$  as defined in Algorithm 5 with a register-free majority function is (d, k)-CINI<sub>ind</sub> in the glitch-robust probing model.

**Algorithm 5:** HPC<sup>1</sup><sub>1</sub>: CINI<sub>ind</sub> multiplication.

```

<sup>1</sup> function HPC<sup>1</sup><sub>1</sub>(a_0^0, ..., a_d^n, b_0^0, ..., b_d^n):

| Require: n = 2k + 1

Require: a_i^{\ell} = a_i^{\ell'} and b_i^{\ell} = b_i^{\ell'} for 0 \le \ell, \ell' \le n, 0 \le i \le d

Require: \sum_{j=0}^d a_j^{\ell} = a and \sum_{j=0}^d b_j^{\ell} = b for 0 \le \ell \le n

// Initialize randomness

for i = 0 to d do

2

for j = i + 1 to d do

3

for m = 0 to k - 1 do

4

\tilde{r}_{i,j,m} \stackrel{\$}{\leftarrow} \mathbb{F}_2; \tilde{r}_{j,i,m} \leftarrow \tilde{r}_{i,j,m}

5

r_{i,j,m} \stackrel{\$}{\leftarrow} \mathbb{F}_2; r_{j,i,m} \leftarrow r_{i,j,m}

6

// Refreshing

for \ell = 0 to n - 1 do

7

for j = 0 to d do

\begin{bmatrix} \tilde{v}_j^\ell \leftarrow b_j^\ell + \sum_{i=0, i \neq j}^d \sum_{m=0}^{k-1} \tilde{r}_{i,j,m} \end{bmatrix}

8

9

// Correction

for \ell = 0 to n - 1 do

10

11

for i = 0 to d do

for j = 0 to d do

12

v_{i,j}^{\ell} \leftarrow \mathsf{maj}(\tilde{v}_i^0 \dots \tilde{v}_i^{n-1})

13

// Multiplication

for \ell = 0 to n - 1 do

14

for i = 0 to d do

15

w_i^\ell \leftarrow a_i^\ell \cdot \operatorname{Reg}[v_{i,i}^\ell]

16

17

18

c_i^{\ell} \leftarrow \operatorname{Reg}[w_i^{\ell}] + \sum_{j=0; j \neq i}^d \operatorname{Reg}[z_{i,j}^{\ell}]

19

Ensures: c_i^{\ell} = c_i^{\ell'} for 0 \le \ell, \ell' \le n, 0 \le i \le d

Ensures: \sum_{i=0}^{d} c_i^{\ell} = a \cdot b for 0 \le \ell \le n

return c_0^0, \ldots, c_d^n

20

```

The proof can be found in Appendix B.

Remark 3, Remark 4, and Remark 5 also hold for the CINI<sub>ind</sub> gadget in Algorithm 5 with the majority function in Line 13 and the masking in Line 9 and 19. Please note, the gadget  $HPC_2^C$  can not be easily transferred to  $CINI_{ind}$  since the contradiction mentioned in Section 4.2 then also occurs for smaller orders ( $d \ge 2$  and  $k \ge 1$ ).

# 6 TOOL SUPPORT

In the last years, many tools supporting the verification and construction of circuits were presented in the literature. We extend the recently published tool VERICA<sup>5</sup> [35] with our novel composability notions. Additionally, we added support for our gadgets to SAIREDA<sup>6</sup> to construct secure cryptographic primitives from insecure implementations using the proposed comparability notions.

Integration into a Verification Tool. VERICA is a verification tool for combined countermeasures which has been coalesced from the SCA verification tool SILVER [28] and the FIA verification tool FIVER [37]. Hence, the tool analyzes a given gate-level netlist with Jakob Feldtkeller, Jan Richter-Brockmann, Pascal Sasdrich, and Tim Güneysu

respect to the protection against physical attacks. More precisely, VERICA can verify stand-alone protection against SCA and FIA but also combined protection considering reciprocal effects between fault-injections and side-channel analysis. These reciprocal effects are analyzed by applying a *active-then-passive* verification approach meaning that the tool injects a valid fault combination followed by a passive side-channel analysis. In this context, VERICA is limited to analyze combined composability only for the C-NI, C-SNI, and C-SNI<sub>ind</sub> security notions [35]. In order to extend VERICA to support our novel security notion, we first extend the fault verification strategies (i.e., error detection and error correction) with a feature to support verification of the FINI notion. Hence, the inputs and outputs require an additional annotation to identify the different redundancy domains. This information is used to track the redundancy domains of erroneous outputs and faulted inputs of a design under test. Based on Definition 3.2, we remove all input redundancy domains from the set of output redundancy domains and check if the cardinality of the resulting set exceeds the number of internal faults (if not, the design is FINI). So far, VERICA only supported two fault composability notions relying on ideas of non-accumulation (see [15, 35] for more details).

Similarly, we extend VERICA to support the verification of the CINI notion introduced in Section 4. In order to check the correctness, we implemented a similar strategy as for FINI but instead of relying on redundancy domains, we use SRDs as defined in Definition 4.1. Note that all faults on randomness are treated as internal faults, as discussed before. To verify the privacy, we modify the integrated PINI strategy of VERICA such that the number of allowed probes depends on the number of injected faults (cf. Definition 4.2).

For the integration of the  $\mathrm{CINI}_{\mathrm{ind}}$  notion, we independently inject faults and subsequently check the the composability in the PINI model. The composability with respect to fault injections is accomplished by applying the same checks as for CINI (i.e., determining the number of faults in different SRDs).

*Gadget Insertion.* To automate the process of integrating the proposed gadgets into a hardware netlist, we added support for the gadgets to the SAIREDA project, which is based on the Multi-Level Intermediate Representation (MLIR) compiler framework [31]. As input serves an unprotected Flexible Internal Representation for RTL (FIRRTL) [26] design restricted to netlist operations (which can be derived from Chisel or Verilog) while the tool produces a protected Verilog description. Here, we support the composability notions of FINI, PINI, CINI, and CINI<sub>ind</sub>.

In a preparation phase, we first transfer the design into an XOR-AND Graph (XAG). Afterwards, the tool operates in two steps: (i) The tool identifies all non-linear and gates and replaces them with abstract gadget operations. All majority functions are realized via the median of a sorting network. In addition, it assigns the required random elements to the gadgets. This is done for all gadget types except for FINI, which does not require additional randomness and only results in a simple replication. (ii) Then, the tool replaces all operations with their secure implementation, i.e., replicating the logic and replacing the abstract gadget operations with their actual logic. Thereby, it adds additional input/output ports for shares, replication, and randomness to the design.

<sup>&</sup>lt;sup>5</sup>Available at https://github.com/Chair-for-Security-Engineering/VERICA

<sup>&</sup>lt;sup>6</sup>Available at https://github.com/Chair-for-Security-Engineering/SAIREDA

Table 2. Number of elements (without implementation of maj).

|      | HPC <sup>C</sup> <sub>1</sub>         | HPC <sup>1</sup>                      |

|------|---------------------------------------|---------------------------------------|

| and  | $(2k+1)(d+1)^2$                       | $(2k+1)(d+1)^2$                       |

| xor  | 3(2k+1)d(d+1)                         | $(2k+1)^2 d(d+1)$                     |

| reg  | $(2k+1)(d+1)^2$                       | $(2k+1)(d+1)^2$                       |

| maj  | $(2k+1)(d+1)^2$ [input size: $2k+1$ ] | $(2k+1)(d+1)^2$ [input size: $2k+1$ ] |

| rand | d(d+1)                                | d(d+1)k                               |

# 7 EVALUATION

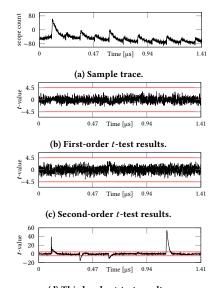

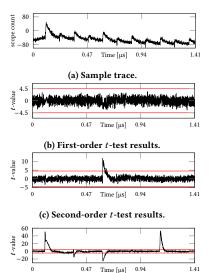

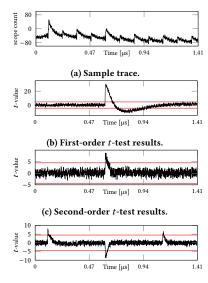

We continue with a practical evaluation of the proposed designs. First, we provide implementation and verification results for the individual gadgets. Afterwards, we use these gadgets to construct cryptographic primitives (i.e., S-boxes) and analyze their security and implementation costs. Eventually, we instantiate a protected PRESENT S-box on an Field-Programmable Gate Array (FPGA) and confirm our theoretical approaches by practical measurements.

## 7.1 Gadget Verification

We start our evaluation by describing the different implementations and highlighting important details that need to be considered when implementing combined gadgets on hardware.

7.1.1 Implementation. We construct FINI gadgets according to Section 3, i.e., the target design is instantiated k + 1 times for detectionbased and 2k + 1 times for correction-based implementations. In addition, detection and correction gadgets follow the *independence property* with respect to redundancy domains by replicating the respective logic as well (cf. Algorithm 1).

For CINI and CINI<sub>ind</sub> linear functions are constructed by instantiating the function (d + 1)(2k + 1) times, i.e., for each SRD one instance, while multiplications are implemented according to Algorithm 2, Algorithm 4, and Algorithm 5. Please note, that an implementation has to adhere to Remark 3 and Remark 4. In Table 2 we provide the number of logic elements, dependent on the order of fault and probing security, required to instantiate the multiplication gadgets HPC<sup>C</sup><sub>1</sub> and HPC<sup>1</sup><sub>1</sub>. Those numbers are without considering the implementation of the majority function, as there is no closed formula for the related implementation cost. Please note that the gadgets have the same implementation cost except for required randomness and the number of xor gates.

7.1.2 *Results.* The implementations and verification results are shown in Table 3. We instantiated and analyzed a FINI and gadget equipped with a detection and a correction gadget for  $k \in \{1, 2, 3, 4\}$ , respectively. All designs fulfill the FINI security notion while the evaluation of the correction gadget for k = 4 requires a notably verification time of 6.24 h.

Next, we analyze the introduced CINI gadget from Algorithm 2 for  $d \in \{1, 2, 3\}$  and  $k \in \{1, 2, 3\}$  and report the required resources. We could verify the security for all gadgets except for the (3, 3)-CINI gadget, as VERICA was not able to finish the analysis in a reasonable time. As already discussed in Section 4.2, we can construct for some parameters *d* and *k* a more tight CINI gadget applying Algorithm 4. Table 3 verifies the security for  $d \in \{1, 2\}$  and  $k \in \{1, 2\}$  while it reveals security flaws for a (3, 1) configuration. We confirm in

| Gadget           | Design |   |       |       |      |           |          | Verification          |                                         |  |  |

|------------------|--------|---|-------|-------|------|-----------|----------|-----------------------|-----------------------------------------|--|--|

|                  | d      | k | rand. | comb. | reg. | area [GE] | Def.     | (d,k)                 | Time                                    |  |  |

| ÷                | -      | 1 | 0     | 3     | 0    | 4.7       |          | $(0,1)^{\checkmark}$  | 0.387 s                                 |  |  |

| Detect           | -      | 2 | 0     | 6     | 0    | 9         | FINI     | $(0,2)^{\checkmark}$  | 0.397 s                                 |  |  |

| Ď                | -      | 3 | 0     | 13    | 0    | 15        | FI       | (0,3)                 | 0.429 s                                 |  |  |

| _                | -      | 4 | 0     | 18    | 0    | 19.7      |          | $(0,4)^{\checkmark}$  | 1.280 s                                 |  |  |

| t                | -      | 1 | 0     | 15    | 0    | 17        |          | (0, 1) ⁄              | 0.383 s                                 |  |  |

| Correct          | -      | 2 | 0     | 75    | 0    | 98.3      | FINI     | $(0,2)^{\checkmark}$  | 0.445 s                                 |  |  |

| , Cor            | -      | 3 | 0     | 147   | 0    | 194.3     | FI       | (0,3)                 | 16.501 s                                |  |  |

| 0                | -      | 4 | 0     | 297   | 0    | 390       |          | $(0, 4)^{\checkmark}$ | 6.24 h                                  |  |  |

|                  | 1      | 1 | 2     | 78    | 24   | 238       |          | (1, 1) ⁄              | 0.409 s                                 |  |  |

|                  | 2      | 1 | 6     | 189   | 54   | 567       |          | (2, 1)                | 0.485 s                                 |  |  |

|                  | 3      | 1 | 12    | 356   | 96   | 1 0 3 2   |          | (3, 1)                | 39.544 s                                |  |  |

| ų                | 1      | 2 | 2     | 340   | 40   | 685       | CINI     | (1, 2)                | 1.490 s                                 |  |  |

| HPC <sup>C</sup> | 2      | 2 | 6     | 795   | 90   | 1 595     |          | (2,2)                 | 6.321 s                                 |  |  |

| I                | 3      | 2 | 12    | 1420  | 160  | 2860      |          | (3, 2)                | 4.662 min                               |  |  |

|                  | 1      | 3 | 2     | 590   | 56   | 1087      |          | (1,3)                 | 16.817 mir                              |  |  |