# When the Decoder Has to Look Twice: Glitching a PUF Error Correction

Jonas Ruchti D, Michael Gruber D and Michael Pehl

Chair of Security in Information Technology Technical University of Munich, Munich, Germany {j.ruchti|m.gruber|m.pehl}@tum.de

**Abstract.** Physical Unclonable Functions (PUFs) have been increasingly used as an alternative to non-volatile memory for the storage of cryptographic secrets. Research on side channel and fault attacks with the goal of extracting these secrets has begun to gain interest but no fault injection attack targeting the necessary error correction within a PUF device has been shown so far. This work demonstrates one such attack on a hardware fuzzy commitment scheme implementation and thus shows a new potential attack threat existing in current PUF key storage systems. After presenting evidence for the overall viability of the profiled attack by performing it on an FPGA implementation, countermeasures are analysed: we discuss the efficacy of hashing helper data with the PUF-derived key to prevent the attack as well as codeword masking, a countermeasure effective against a side channel attack. The analysis shows the limits of these approaches. First, we demonstrate the criticality of timing in codeword masking by confirming the attack's effectiveness on ostensibly protected hardware. Second, our work shows a successful attack without helper data manipulation and thus the potential for sidestepping helper data hashing countermeasures.

**Keywords:** physical unclonable function  $\cdot$  fuzzy commitment scheme  $\cdot$  fault attack  $\cdot$  safe error attack  $\cdot$  clock glitch  $\cdot$  masking

## 1 Introduction

Suppose you find yourself in the shoes of a vendor needing to protect a device's firmware against unauthorised copying and modification. As your product does not have a protected non-volatile memory (NVM) suitable for the secure storage of an encryption key, you turn your attention to Physical Unclonable Function (PUF) key storage schemes. PUFs have gained much attention for similar applications in the last two decades as they can sidestep the problems of storing a secret in NVM.

By exploiting unavoidable tolerances of the manufacturing process, a PUF provides a device-unique secret. These variations are measured with a PUF circuit, such as SRAM cells [HBF07], ring oscillators (ROs) [Gas+02; SD07; YD10b], or concurrent delay chains like in Arbiter PUFs [Gas+04]. In any case, the PUF circuit measurement under different challenges or of PUF circuits in different positions in a device results in a set of noisy PUF responses, which—in case of key storage systems—are then error-corrected to arrive at a sufficiently stable secret.

One big benefit of a PUF-based key storage system is that the secret generated from a PUF is only made available on the chip on demand. As a consequence, countermeasures such as tampering sensors can focus on protecting the time window in which the secret is derived and processed. The existence of invasive attacks such as the ones presented in [Hel+13; Mer+11a] shows that such countermeasures are needed. However, sensors are

hardly able to detect non-invasive attacks and a variety of possible attacks have thus to be considered in the PUF context.

State of the art regarding attacks on PUFs. Attacks on PUFs encompass a large variety of different attack vectors. The likely most popular attacks are related to machine learning, e.g. [Rüh+10; Bec15; Gan+16]. Attacks in this domain mostly focus on the challenge-response behaviour of a PUFs and are therefore not of relevance when storing a secret key with a PUF, where the response is usually not available from outside of the chip. Even though few works have shown that PUFs with challenge-response behaviour are also vulnerable through exploiting public helper data needed to enable error correction in the system [BWG15; SFP21], such attacks are not critical for the majority of key storage schemes today, which only use single-challenge PUFs.

Another class of attacks hinges on observing the PUF measurement through side channels, including invasive attacks exploiting the photon emission of SRAM cells and Arbiter PUFs [Hel+13; Taj+14] as well as attacks using localised electromagnetic measurements of RO PUFs [Mer+11a; SF20]. The latter are not limited to invasive attacks; successful side-channel attacks on the TERO PUF [TPI19] and on the Loop PUF [TDP20] show that even non-invasive attacks are feasible and have to be taken into account through some protection mechanism when implementing a PUF system.

As for any cryptographic algorithm processing a secret, the algorithm deriving a noise-free key from a noisy PUF response is also subject to hardware-related attacks. For example, the two-metric helper data scheme can enable the derivation of response bits from side-channel measurements [Teb+21]. In addition, the error correction code (ECC) decoder circuit itself can also be subject to side channel attacks [Mer+11b; MSS13; TPS17].

While the feasibility of side-channel attacks (SCAs) on PUFs has already been proven, Fault Injection Analysis (FIA) of a PUF-based key storage systems has been mostly out of scope for the community. Only few works like the fault attacks on RO- and Arbiter-based PUF primitives [Taj+15; DV14b] investigated the feasibility of such attacks.

Yet, none of the existing works focused on attacks on the PUF error correction. The focus of this work lies in the feasibility of Fault Injection Analysis of the error correction code of PUF-based key storage systems, which has so far not been explored.

Another potential attack vector in a PUF-based key storage system are the public helper data required for error correction [Del+15]. Deliberate helper data manipulation can be used to extract secrets due to inherent weaknesses of some helper data algorithms [Hil+13; DV14a; DV14c] or to force the output of an attacker-controlled key if particular ECCs are used [Bec19].

Helper data manipulation also plays a central role in hardware-oriented attacks on the ECC. For example, the Differential Power Analyses (DPAs) of [MSS13; TPS17] depend on the ability to influence intermediary states via the helper data. Comparable to [DV14c], our FIA extracts secrets bit-wise after using helper data manipulation to make an induced fault observable. However, the former exploits algorithmic weaknesses to cause a data-dependency in the failure rate of the key recovery via helper data manipulation; our attack achieves this via a clock glitch, exploiting implementation effects in a hardware decoder.

In contrast to [Hil+13; DV14a; DV14c; Bec19], where helper data manipulation is the only attack vector, it is merely an enabler for our fault attack. Attack possibilities without helper data manipulation are thus also possible and are discussed later.

**Contributions.** This work is focused on one concrete implementation of a PUF-based key storage system. Nevertheless, our conclusions are applicable to a more general scope. The contributions are:

• We introduce a theoretical model for a FIA on an error correcting scheme.

- We demonstrate the practical feasibility of the FIA using a code concatenation of a (7,1,3) repetition code and a (127,64,10) Bose–Chaudhuri–Hocquenghem (BCH) code.<sup>1</sup> implemented on an field-programmable gate array (FPGA)

- We discuss the impact of long-term PUF response drift and methods to compensate it for the attack. We also demonstrate the attack's feasibility under a range of PUF noise conditions.

- We discuss the applicability of two possible countermeasures, namely of codeword masking and helper data hashing. We demonstrate the attack in the presence of masking, as well as in a cross-device profiling scenario without helper data manipulation. Given these results, we suggest further basic countermeasures.

- We demonstrate the impact of different guessing strategies for a base-line case as well as in the presence of codeword masking, as well as for an attack without helper data manipulation.

**Outline.** The rest of this work is structured as follows. Section 2 provides preliminaries on PUF-based key storage systems and fault attacks. In particular, it motivates error correction code choices and introduces the PUF noise model used in this work. In addition, it summarises glitch-based Fault Injection Analysis and introduces the notation for this work. After providing the attacker and fault models, Section 3 describes the attack itself. Section 4 justifies the hardware set-up used for validating the attack experimentally, after which Section 5 presents the experiment results for a range of different scenarios. After the results' implications have been discussed in Section 6, this work ends with a conclusion and an outlook in Section 7.

## 2 Preliminaries

Before describing the actual fault attack, the fundamentals of the underlying system are defined. This section discusses how keys are stored with PUFs and summarises fault attacks with a focus on glitch-based attacks.

## 2.1 Notation

Upright bold-face variables denote bit vectors, as they are used within the device under attack for storage and transmission of messages and secrets.  $\mathbf{a}_i$  is the *i*-th bit of the vector  $\mathbf{a}$  and can either be 0 or 1. The bits are defined to be numbered from left to right, in their order of transmission, i.e.  $\tilde{\mathbf{c}}_0$  will be the first codeword bit to be transmitted to an ECC decoder and  $\tilde{\mathbf{c}}_{n-1}$  the last.  $\mathbf{e}_i = [0, \dots, 1, \dots, 0]$  denotes the bit vector which is 1 at the position *i* and 0 elsewhere. HW( $\mathbf{a}$ ) refers to the hamming weight of  $\mathbf{a}$ , i.e. the number of 1s in the bit vector.

Important constants for the secret recovery algorithms outlined later in this section are the parameters of the attacked ECC decoder, which are often written as a triplet (n, k, t). n is the codeword length, coinciding with the length of the PUF secret, while k is the length of the encoded secret. t denotes the number of bit errors the ECC is guaranteed to recover from.

$<sup>^{1}\</sup>mathrm{The}$  code parameters are taken from [MSS13] to allow for a better comparability of the impact of the attack.

## 2.2 PUF-based key storage

A PUF allows for low-cost key storage solutions, which are useful e.g. for Internet of Things (IoT) devices. However, PUF responses are subject to noise, environmental effects, and ageing. While a few approaches like [DGS19] promise error-correction-free key storage with PUFs, in practical implementations error correction is used to reliably reproduce a secret key from a noisy PUF response.

To allow for using an error correcting code, however, a helper data algorithm is needed to map the PUF response to an ECC codeword. In this work we focus, for the sake of simplicity of our explanation, on the fuzzy commitment scheme [JW99], which this section introduces. We discuss the equivalence of the code-offset fuzzy extractor and the principal applicability to syndrome construction in Appendix A.

As we focus on key storage, approaches like the reverse fuzzy extractor [Van+12], which are used for authentication and require only an error correction encoder on the device, are out of scope for this work. We also do not consider pointer-based helper data algorithms like [YD10a; Hil+12; HYS16], though they can still enable our attack if they are only the first stage of an helper data algorithm.

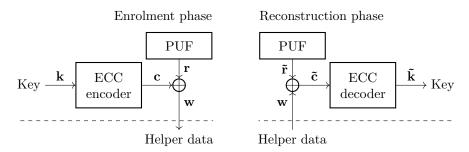

**Fuzzy Commitment Scheme.** Figure 1 depicts a sketch of the resulting system when using the Fuzzy Commitment Scheme. It is based on two phases: the *enrolment* phase and the *reconstruction* phase.

Figure 1: Fuzzy commitment scheme

During the one-time enrolment, the key to be stored  $\mathbf{k}$  is encoded to a codeword  $\mathbf{c}$ . XORing  $\mathbf{c}$  with a reference measurement of the PUF response  $\mathbf{r}$  yields the so called *helper data*  $\mathbf{w}$ , which is then stored for later usage.

When the secret  $\mathbf{k}$  is needed at a later point in time, it is reconstructed from helper data and PUF response. This process begins with a PUF measurement  $\tilde{\mathbf{r}}$ . As this measurement differs from the reference  $\mathbf{r}$  due to noise and environmental effects, its combination with the helper data,  $\tilde{\mathbf{c}} = \tilde{\mathbf{r}} + \mathbf{w}$  is also not exactly the same as the codeword calculated during the enrolment phase. However, the error in  $\tilde{\mathbf{c}}$  is compensated by the system's ECC, deriving a key  $\tilde{\mathbf{k}}$  which is correct with high probability  $\Pr[\tilde{\mathbf{k}} = \mathbf{k}]$ .

All values above the dashed line in Figure 1 are secrets and only exist within the device during its operation. The helper data  $\mathbf{w}$ , on the other hand, can be stored in a publicly accessible manner, while ensuring sufficient entropy remains in the secrets.

To extract the secrets from the system, the attack described in this work manipulates the transmission of the ECC codeword  $\tilde{\mathbf{c}}$  during a reconstruction phase. By introducing faults during this transmission and observing the system's behaviour, information about  $\tilde{\mathbf{c}}$  and thus  $\tilde{\mathbf{r}}$  is recovered. Consequently, the attack is also applicable to other helper data schemes which process PUF and helper data in a comparable manner, like it is the case for the *code-offset fuzzy extractor* [Dod+08] (cf. Appendix A).

Choice of error correction code. Importantly, the design of a PUF key storage system includes the choice of an error correction code and its concrete implementation. Next to the PUF's noise performance and acceptable decoding failure rate determining the ECC's error correction capability, other factors have to be taken into account, e.g. the area usage of the decoder within the key storage system.

As the review of error correcting codes for PUFs in [HKS20] shows, one of the most frequently used designs for decoders in this domain is a concatenated code with a repetition as the inner and a BCH code as the outer code. This is motivated by the requirements for PUF key storage: since most frequently, the demand for low cost leads to the choice of a PUF key storage system, low area overhead for the error correction is a requirement; the concatenation of repetition and BCH codes is well-suited in this regard.

The output of the PUF can be processed in blocks of the size of the repetition code, which the repetition code decoder then processes using only a few logic gates. A BCH decoder takes the repetition decoder's output as its input in a bit-serialised way and derives the syndromes by using few small linear-feedback shift registers (LFSRs) before the error in the codeword is computed from the syndromes, typically using the Berlekamp–Massey and the Chien search algorithms (cf. Section 4.2).

While bit-parallel solutions for BCH decoders exist, they are more complex, i.e. require more area, and would demand for multiple parallel instantiations of the repetition code in the concatenation. Naturally, this work focuses on a code concatenation of repetition and BCH code and uses a bit-serial BCH decoder. The impact of bit-parallel decoders on our attack will be described in our discussion, Section 6.

#### 2.3 PUF noise model

The long-term deviation and short-term noise affecting the PUF response are key to the system performance. As any PUF will be subject to environmental influences, the impact of non-perfect PUF reliability on the attack will have to be considered, too.

While the designer of a PUF key storage system mostly has to consider the worst-case total difference between enrolment-time PUF response  $\mathbf{r}$  and the reconstruction-time  $\tilde{\mathbf{r}}$  for the ECC design, we will further split this deviation into two parts:

$$\tilde{\mathbf{r}} = \mathbf{r} \oplus \Delta \mathbf{r} \oplus \delta \mathbf{r}. \tag{1}$$

$\Delta \mathbf{r}$  is an *offset*, e.g. due to ageing or a temperature difference between enrolment and reconstruction. This offset can be thought of as caused by longer-term drift and is assumed to be constant throughout the attack. The remaining part of the difference is captured by the *noise* term  $\delta \mathbf{r}$ , which can be different from each reconstruction phase to the next.

This split is of particular importance due to the fuzzy commitment scheme construction: if  $\Delta \mathbf{r}$  becomes known to the attacker, they can compensate it by manipulating the helper data, since any helper data offset is propagated to a codeword offset. With  $\Delta \mathbf{r}$  compensated, the total PUF noise becomes significantly smaller, simplifying the attack. A method for determining  $\Delta \mathbf{r}$  through helper data manipulation will be discussed later, in Section 3.4.

Note that an attacker with physical access to the device can, in part, influence the PUF noise terms. The reliability of RO-based PUFs, for example, is known to have a strong temperature dependency [WBG17]. With full access to the device under attack and knowledge of the PUF design, the attacker can set the ambient temperature, supply voltage, or other environmental parameters to effect the best- or worst-case PUF performance.

If the device uses, as mentioned in the previous section, a concatenated code, an attacker might want to target the outer decoder. Since only one decoder is attacked in our work, we will use the symbols  $\Delta \mathbf{r}$  and  $\delta \mathbf{r}$  for the offset and noise at the input of the attacked decoder, after the inner decoder in this case. Note that the preceding inner code can be a significant advantage to the attacker: since a large portion of the PUF noise and

offset are already compensated by the inner decoder,  $\Delta \mathbf{r}$  and  $\delta \mathbf{r}$  as present at the attacked outer decoder's input will have less impact on the secret extraction.

## 2.4 Glitch-based Fault Injection Analysis

Fault Injection Analysis is the generic term for a class of physical attacks as introduced by Boneh et al. in their seminal work [BDL00]. The underlying principle of these attacks is a deliberate violation of a device's specifications to introduce erroneous behaviour. A low-cost way to cause a violation of the critical path is glitching [Bar+06; Exi14], either using a voltage drop or a temporary increase of the clock frequency. Both approaches intentionally cause a violation of the set-up time requirement  $t_{\rm p}+t_{\rm su} < T$  [Sap06], by either raising the propagation time  $t_{\rm p}$  or lowering the clock period T so that a critical path's output signal is no longer stable in a register's set-up time window  $t_{\rm su}$ .

Several physical glitching set-ups have been proposed [OC15; Kud+18; SMC20]. Furthermore, Krautter et al. were even able to show that on-chip power glitching is feasible even without a physical glitching set-up [KGT18].

In this work we will focus on on-chip clock glitching, which enables a high temporal precision by inserting a precisely timed additional clock edge within a regular clock cycle [BGV11]. Our glitch generator design is discussed in detail in Appendix B.

## 3 The proposed attack

This section first outlines our attacker model, describes the fault model used in this work, and sketches the attack on a PUF key storage system. Thereafter, the process of the attack and all necessary algorithms are described in detail.

#### 3.1 Attacker Model

The nominal device under attack is a low-cost device, e.g. used in an IoT application, which uses a PUF as a replacement for secure NVM to store a secret key. This requires a secure sketch as well as an error correction decoder on the device as it was discussed in Section 2.2. We assume that the inner construction of the device is known to the attacker.

Similar to the side-channel attacks discussed above, we assume that the attacker has direct access to the device containing the PUF. This allows for modifications of the device clock and, in particular, the insertion of a clock glitch.

With direct access to the device, the attacker can also influence its operating environment, e.g. through ambient temperature or supply voltage. This is useful in two directions: either an optimal environment can be constructed, where the PUF has very low noise, or a hostile environment can be enforced, operating the device outside its specifications. The former case limits the influence PUF noise naturally has on the attack, while the latter allows for the insertion of additional bit flips.

We further assume that the helper data is public. This assumption is in line with the use of a PUF: the existence of secure memory to store helper data would allow for storing a key directly without the need for a PUF. If not explicitly stated otherwise, we further assume that manipulation of helper data is possible. This is the case if helper data are, e.g., stored in external NVM and the attacker manipulates the transmission from the NVM to the device. The prevention of helper data manipulation is one of the suggested potential countermeasure against FIAs but does not render the attack completely infeasible, as will be shown in the experiments.

The most secure ways to store a key with a PUF are to store a key encryption key or a private key. The goal of the attacker is to retrieve this secret key—to which they have no direct access—or to reduce the key's entropy in order to corrupt e.g. confidentiality of

previous or future data. The attacker can observe if the tampered-with device correctly performs key-based cryptographic operations or not. From these observations the attacker can conclude if the secret key was correctly derived from the PUF or not.

**Base-line attacker.** Summarising, the most powerful attacker—our base-line attacker—can manipulate the input to the error-correcting code via the helper data and observe the output in a pass/fail manner.

In their most powerful form, this attacker can do on-device profiling, i.e. determine the optimal timing for the glitch on the same device which is later under attack. In the attacker's ideal case, the input to the decoder also is perfectly reliable and constant during the course of the experiments (without the attacker's intervention), so that permanent faults can be compensated through helper data manipulation.

This assumption is related to the attacker's reach, since controlling the environmental conditions of the PUF, the attacker can bring it into a region where a very low number of bit errors occurs. The decoder, on the other hand, has to be designed for the worst-case error. In the case of a concatenated code, like it was motivated above, the inner repetition code might filter out most of the PUF noise so that the attacked outer BCH code sees next to no noise.

**Restricted attacker.** The described, very powerful attacker is used in the following to showcase the general principle and feasibility of the attack. To converge towards a more realistic use case, we decrease the attacker's power and analyse the following cases:

- We consider the case where the BCH decoder input is noisy. The attacker does not have to control the PUF's environment in this case.

- We show results for the case where on-device profiling is not possible. Here, the attacker has to determine the glitch parameters on a distinct set of devices, possibly bought on the free market before applying the attack to the target device. Thus, they need to be in the possession of the device for a significantly shorter time and do not need to tamper with it as much.

- Finally, we consider the case where the attacker cannot perform helper data manipulation. In this case, protections against helper data manipulation, e.g. through hashing the error corrected PUF derived secret with the helper data, do not hinder the attack anymore. This is the most powerful attacker we consider.

#### 3.2 Fault model

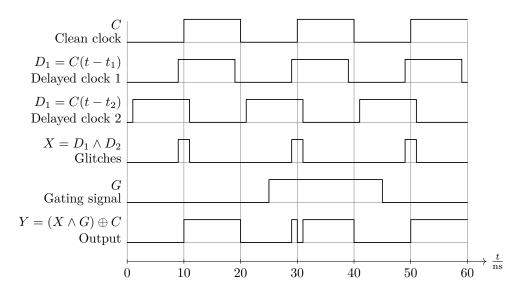

On a fundamental level, the reconstruction of the key from a PUF and in particular the error correction is carried out by *sequential logic*, whose memory is provided by registers capturing their inputs at a clock line's rising edge.

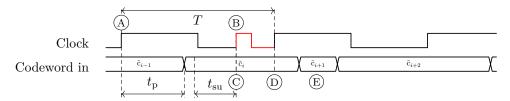

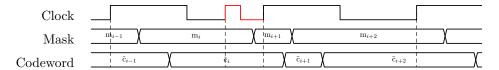

Figure 2: Codeword transmission as received by the decoder, exhibiting exemplary fault effect. The clock glitch is highlighted in red.

A possible effect of a set-up time violation is that the register stores the state of its input *before* the transition. Figure 2 shows this in an exaggerated fashion by adding a clock glitch during the propagation time of the previous clock cycle's signal.

Evidently, in the example in Figure 2, the time between the first rising clock edge  $\widehat{\mathbb{A}}$  and the glitch's rising clock edge  $\widehat{\mathbb{B}}$  is sufficiently long, the codeword is stable for a sufficient time, and set-up time is not violated when sampling codeword bit  $\widetilde{c}_i$  at time point  $\widehat{\mathbb{C}}$ . However, the glitch is too close to the following rising clock edge and the driving signal cannot propagate to the decoder's input quickly enough—the *i*-th codeword bit is captured again at time point  $\widehat{\mathbb{D}}$ . The value  $\widetilde{c}_{i+1}$  arriving at the decoder input is only available for a short time  $\widehat{\mathbb{E}}$  as it is quickly replaced by  $\widetilde{c}_{i+2}$ , which began propagating to the decoder at the rising clock edge  $\widehat{\mathbb{D}}$  after the glitch. Effectively, the decoder samples  $\widetilde{c}_i$  twice and skips  $\widetilde{c}_{i+1}$ .

The fault model assumed in this work is similar to the one of a Safe Error Analysis (SEA) as proposed by Yen et al. [YJ00]. In the context of a SEA an attacker gains knowledge from the observation if the induced fault does alter the output of e.g. a cryptographic algorithm. In order to achieve such a fault model, the intermediate value under attack is always set to a known value i.e. set to one or reset to zero. An attacker can successively deduce the intermediate state by repeating this approach while observing whether the output changes under fault or not. In our proposed attack we utilise this approach in a similarly way where the attacker can gain knowledge about the equality of two successively transmitted bits.

#### 3.3 Attack sketch

To justify the relevance of the attack, we outline an exemplary system where we consider a device with application code stored in unprotected NVM.

The manufacturer wants to prevent unauthorised copying, and modification of the memory contents even for an attacker with physical access to the device and thus encrypts them using a device-unique key. For the key storage, a PUF system as sketched in Figure 1 is employed. Required helper data for the PUF system is considered public and stored together with the encrypted application code, where it can be read and modified by the attacker as per attacker model.

During boot-up, the device reconstructs the secret key from a PUF measurement and the helper data and uses it to decrypt the memory contents. Because all secrets only exist during runtime, tamper protection measures have to be active only as long as the device is powered, which allows the attacker to modify the hardware in a powered-down state in order to introduce a clock glitch later.

The attacker now manipulates the helper data in such a way that the error-correcting code under attack is at its correction limit, i.e. such that the output key is still correctly derived but is influenced as soon as a fault injection changes a single codeword bit, e.g. using the later introduced Algorithm 1.

For consistent results, the attacker extracts any static offset the PUF might have accumulated due to ageing using Algorithm 2's helper data manipulation. Additionally, to exploit the previous section's fault model, allowing them to replace one codeword bit<sup>2</sup> with the preceding bit's value, the attack will require profiling in most scenarios: optimal glitch parameters are first determined e.g. using Algorithm 3.

Then, the attacker applies power to the device and introduce a clock glitch while the codeword is transferred to the ECC decoder. By observing the outcome of the reconstruction phase (i.e. pass or fail) after inserting a glitch, the attacker can then reason about the two bits' difference. If the device still boots, the recovered key was unaffected

<sup>&</sup>lt;sup>2</sup>This work assumes a bit-serial transmission. The attack is also adaptable to larger bus widths, in a straight-forward way up to the ECC's error correction capability and even further with additional effort, see Section 6.

by the bit replacement and both codeword bits can be concluded to be the same. If the device fails to boot, replacing the targeted codeword bit with its predecessor evidently changed the codeword and with the ECC at its error correction limit also the key.

The attacker repeats this experiment, as Algorithm 4 summarises, targeting different codeword bits through repeatedly power-cycling the device, modifying the helper data, and introducing clock glitches. This way, they finally recover all bit differences of the ECC codeword and thus the PUF secret.

## 3.4 Secret extraction algorithms

The following describes required procedures to extract PUF-generated secrets from a device using the previously described mechanisms. For brevity's sake, all algorithms in this section at first assume a perfectly reproducible glitch effect and no PUF measurement noise or environmental variation, i.e.  $\tilde{\bf r} \equiv {\bf r}$  and  $\tilde{\bf c} \equiv {\bf c}$ , which makes all interactions with the device under attack deterministic. This assumption does not limit the applicability, since PUF measurement noise or independent extraction errors can be compensated by averaging multiple codeword extractions.<sup>3</sup>

To represent an interaction with the device under attack, the algorithms below use a place-holder function Experiment( $\mathbf{w}'[,g,\theta]$ ): using the (modified) helper data word  $\mathbf{w}'$  and optionally a glitch position g and parameter set  $\theta$ , a reconstruction phase is carried out on the target. After a usage of the reconstructed key, Experiment returns whether the reconstructed key matches the key programmed during enrolment of the PUF system.

Herein, g is the integer position of the glitch, i.e. the index of the codeword bit during whose transmission the clock glitch is introduced, while  $\theta$  contains other glitch parameters, e.g. alignment settings or the exact glitch timing to use.  $\theta$  is optimised during profiling; the other algorithms will use  $\theta^*$ , the optimal parameters found during the preceding profiling step. Consequently, Experiment( $\mathbf{w}', g, \theta^*$ ), which introduces a clock glitch during the transmission of bit g, returns false if replacing  $\tilde{\mathbf{c}}_{g+1}$  with  $\tilde{\mathbf{c}}_g$  leads to  $\tilde{\mathbf{k}} \neq \mathbf{k}$ .

The algorithms introduced in this section are generic regarding the actual ECC used in the implementation, as long as our attacker and fault models apply. If, like in our experiments below, only the outer decoder of a cascaded code is attacked, the code length n naturally refers to the decoder under attack's input, as do  $\mathbf{c}$ ,  $\Delta \mathbf{r}$ ,  $\delta \mathbf{r}$ , etc.

**Helper data manipulation.** According to our fault model, introducing a clock glitch at position g data-dependently influences the codeword bit at position g + 1. For this change to be observable, the ECC decoder needs to be at its *error correction limit*.

In general, an ECC can recover from more than t bit errors in some cases, which makes the necessary helper data manipulation dependent on the codeword and glitch position. To bring the ECC to its correction limit, an attacker can invert bit g+1, successively add more bit flips until EXPERIMENT always fails (without a glitch), and then revert the modification of g+1.

The special structure of the BCH code in the experiments, however, allows to add exactly t bit flips within the first k bits of the codeword to bring the decoder to its error correction limit, which simplifies the problem.<sup>4</sup> Algorithm 1, detailed below, constructs such a helper data manipulation vector, intelligently placing the bit flips to the attacker's advantage. As only the symbol part of the codeword is modified, the improvements do not hold for redundancy bits, which will become apparent later. However, we accept this compromise to allow for an easier choice of bit flips.

$<sup>^3</sup>$ We assume a bit error probabilities of below 50 %. Bit error probabilities above 50 % correspond to a PUF response offset and can be compensated by flipping the corresponding helper data bit.

<sup>&</sup>lt;sup>4</sup>This property follows from the systematic encoding with the first k bits of a codeword being equal to the encoded symbol and the usage of *Chien search*, which can find a maximum of t errors.

**Algorithm 1** Construct an n-bit vector  $\mathbf{f}$  which can be used to bring the (n, k, t)-decoder to its error-correction limit, given a glitch position g and the target hamming weight t.

```

1: procedure Correction Limit(q, t)

\mathcal{N} \leftarrow \{i : 0 \le i < k \land 0 \le |i - g| < \frac{t}{2}\}

\triangleright Define a set of positions near the glitch

f_i \leftarrow 0 \quad \forall i \in [0, n)

3:

\triangleright Initialise the bit flip vector {\bf f} to all-zeros

4:

Choose f_i uniform randomly from \{0,1\}

\forall i \in \mathcal{N} \setminus \{g+1\}

5:

while HW(\mathbf{f}) < t \ \mathbf{do}

\triangleright Increase hamming weight to t

f_i \leftarrow 1 with i random from [0, k) \setminus \mathcal{N}

6:

7:

return f

▶ Return bit flip vector

```

As a first step, bit positions 'near' the glitch position are chosen i.i.d. uniform in line 4, ensuring that there are at most t bit flips. This set  $\mathcal{N}$  of 'neighbours' is chosen in line 2 such that all bit flips are placed within the first k codeword bits and thus varies in size. Choosing  $f_g$  in particular at random has an advantage, because a helper data bit flip at position g, changing the codeword bit before the glitch, inverts the outcome of EXPERIMENT( $\mathbf{w}', g, \theta^*$ ). If, for some glitch position, the fault effect is not data-dependent, its behaviour will then become apparent during the attack: for such positions the outcome of EXPERIMENT is static, i.e. always failing or always succeeding, while it would be expected to differ depending on the choice of  $f_g$  in case of a data dependency.

Randomising a range of bit positions also helps to counteract the effects of glitch position jitter: as the codeword bits neighbouring the glitch position are now unbiased and independent of the codeword, measurement noise caused by imprecisely placed glitches is independent as well and can be compensated by averaging multiple trials as long as the glitch still falls within  $\mathcal{N}$ .

Finally, the loop beginning with line 5 ensures the correct hamming weight of  $\mathbf{f}$  with additional bit flips at random positions. Bit positions from the set of neighbours  $\mathcal{N}$  are excluded here to preserve the previously sampled uniform distribution.

If PUF noise is to be considered, this algorithm mostly stays the same, since it does not require any interaction with the device under attack. However, the target hamming weight has to be lowered from the decoder's t: since the PUF noise will introduce, on average,  $E[HW(\delta \mathbf{r})]$  bit flips,  $HW(\mathbf{f})$  has to be decreased by this amount to avoid immediately bringing the ECC over its error correction limit. This number can also be determined with helper data manipulation by testing which hamming weight helper data modification is, on average, required to make a reconstruction fail (without a glitch).

**PUF offset extraction.** Due to ageing or temperature differences, the PUF's response during the reconstruction phases the attacker initiates might have a constant offset with respect to its enrolment-time value. If this offset is known to the attacker, they can compensate it via the helper data, ensuring that, in the absence of PUF noise and any further helper data manipulation, the decoder's input is a valid codeword.

Algorithm 2 extracts this offset by, after adding bit flips to **w** until the ECC is over its error correction limit and reconstruction fails (line 9), testing if a single bit flip in a remaining position lets it succeed again (line 12). If that is the case, the added single bit flip has collided with an existing offset bit flip and reduced the total difference to a valid codeword, moving it into the error correction region again.

Instead of choosing the checked bit positions at random, the algorithm uses a stack in order to reach all positions more quickly. If this stack has to few positions to guarantee a failing reconstruction in the worst case (t bit flips all hitting positions i with  $\Delta \mathbf{r}_i = 1$ ), it is refilled once per average (line 7). The positions in the stack are shuffled so that all bits are covered and to avoid always checking the same combinations of bit flips.

To be able to test all n bits and to combat PUF noise, the process of first bringing the decoder to a reconstruction failure and then detecting successes due to individual bit

**Algorithm 2** Recover a constant difference  $\Delta \mathbf{r}$  between the PUF responses at enrolment and reconstruction time, given the helper data  $\mathbf{w}$  and using N averaged iterations.

```

1: procedure PUF Offset(\mathbf{w}, N)

2:

\Delta \mathbf{r}_i \leftarrow 0 \quad \forall i \in [0, n)

\triangleright Initialise offset to zero

3:

\operatorname{cnt}[i] \leftarrow 0 \quad \forall i \in [0, n)

\triangleright Set experiment counters zero

4:

positions \leftarrow []

▷ Initialise empty bit position stack

for N iterations do

5:

if length(positions) \leq 2t then

6:

7:

positions \leftarrow shuffle([0, n))

▶ Refill stack of positions if too few

\mathbf{f}_i \leftarrow 0 \quad \forall i \in [0, n)

8:

▷ Start with no HD manipulation

9:

while Experiment(\mathbf{w} \oplus \mathbf{f}) succeeds do

▶ Add bit flips until reconstruction fails

10:

\triangleright Draw bit flip position, removing it from the stack

\mathbf{f}_i \leftarrow 1 \text{ with } i = \mathbf{pop}(\text{positions})

11:

for i \in [0, n) \setminus \{i : f_i = 1\} do

▶ Use all positions without bit flips

12:

if Experiment(\mathbf{w} \oplus \mathbf{f} \oplus \mathbf{e}_i) succeeds then

\triangleright Try with an extra flip at position i

13:

\Delta \mathbf{r}_i \leftarrow \Delta \mathbf{r}_i + 1

\triangleright Reconstruction succeeds again, so there is an offset at position i

14:

\operatorname{cnt}[i] \leftarrow \operatorname{cnt}[i] + 1

▶ Increment counter for averaging

15:

\Delta \mathbf{r}_i \leftarrow \Delta \mathbf{r}_i/\mathrm{cnt}[i]

▷ Divide by counters to finalise the estimate

16:

return \Delta r

```

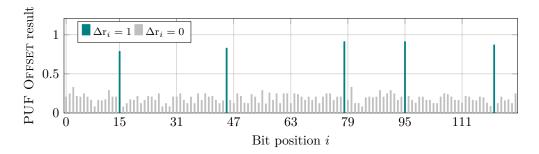

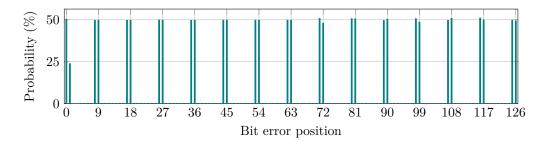

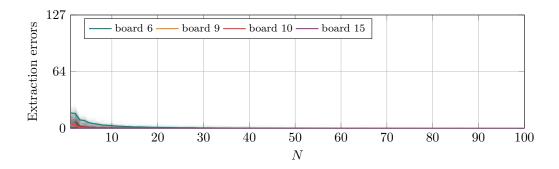

Figure 3: Result of Algorithm 2 with N=25 averaged iterations. A 127-bit BCH decoder was simulated with an error rate of BER<sub>BCH</sub> = 0.5 %. The bar colour indicates the bit value of the original  $\Delta \mathbf{r}$ , which can be fully recovered from the average.

flips is repeated a number of times, averaging the results for each codeword bit position. Figure 3 shows an exemplary simulation result based on the decoder later introduced for the experiments, where the offset was recovered using 25 averaged iterations.

In the following, we will assume that the attacker has extracted and compensated any PUF offset in all cases where helper data manipulation is available.

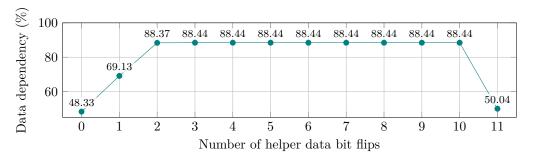

**Profiling.** For a successful attack, the best parameters, e.g. for alignment and timing of the clock glitch, need to be determined first. To estimate the exploitable data dependency, given a parametrisation  $\theta$ , Algorithm 3 carries out four fault injections, modifying two adjacent helper data bits in all four bit patterns.

If an exploitable data dependency is present for a parametrisation  $\theta$ , either the first two or the second two conditions in lines 6 to 9 will be fulfilled, regardless of the actual codeword. In this case, r will accumulate an absolute value of 1. If the results of EXPERIMENT do not depend on whether a bit difference at the glitch position is present, the contributions to r will cancel out.

Take, for example, the case where the two consecutive bits  $c_g$  and  $c_{g+1}$  differ. With optimum parameters and thus a fault effect in line with our model, EXPERIMENT in line 6, where neither of the bit positions g and g+1 around the glitch is modified and t errors are introduced via the helper data, fails. In line 7, t+1 helper data bit flips are introduced, which would, without a glitch, lead to a reconstruction failure. If the glitch replaces  $c_{g+1}$  with  $c_g$ , it offsets the change to  $c_{g+1}$ , effecting a reconstruction success. Lines 8 and 9

**Algorithm 3** Determine a fitness measure of a point  $\theta$  in the parameter space at a glitch position g, using the original helper data  $\mathbf{w}$ .

```

1: procedure FITNESS(\mathbf{w}, q, \theta)

\mathbf{f} \leftarrow \text{Correction Limit}(g, t-2)

3:

Pick x,y at random from [0,n)\setminus\{g,g+1\} such that x\neq y and \mathbf{f}_x=\mathbf{f}_y=\mathbf{0}

4:

\mathbf{w}' \leftarrow \mathbf{w} \oplus \mathbf{f}

5:

if Experiment(\mathbf{w}' \oplus \mathbf{e}_x \oplus \mathbf{e}_y, g, \theta) fails then r \leftarrow r + \frac{1}{2}

6:

if Experiment(\mathbf{w}' \oplus \mathbf{e}_g \oplus \mathbf{e}_{g+1} \oplus \mathbf{e}_y, g, \theta) succeeds then r \leftarrow r + \frac{1}{2}

7:

if Experiment(\mathbf{w}' \oplus \mathbf{e}_g \oplus \mathbf{e}_y, g, \theta) fails then r \leftarrow r - \frac{1}{2}

8:

if Experiment (\mathbf{w}' \oplus \mathbf{e}_x \oplus \mathbf{e}_{g+1} \oplus \mathbf{e}_y, g, \theta) succeeds then r \leftarrow r - \frac{1}{2}

9:

10:

return |r|

```

result in a success and failure, respectively, and do not affect r, leading to a total value of 1. For a codeword with equal  $c_g$  and  $c_{g+1}$ , the behaviour is reversed and r accumulates a value of -1 before the absolute value is taken.

Averaging multiple calls to FITNESS thus provides an estimate of the observable data dependency as a value between 0 and 1. An attacker can use this information for a numeric optimisation of the parameter point. In the simplest case, they evaluate FITNESS averages for random glitch positions over a grid in the parameter space and then pick the optimal  $\theta$ . This approach was used for the experiments; the results of the profiling step are detailed in Appendix C.

**Codeword extraction.** Having ensured that the ECC is at its correction limit, Algorithm 4 extracts the codeword by iterating through all bit positions and placing a glitch before each in turn, observing the result of the fault injection. The first codeword bit is extracted based on the assumption that the state of the data line before the transmission  $\hat{c}_{-1} = 0$ , i.e.  $\hat{c}_0$  is 1 if the first glitch experiments with the clock glitch inserted before the transmission of bit 0 leads to a reconstruction failure.

**Algorithm 4** Recover the n-bit codeword  $\mathbf{c}$  assuming a set-up time violation glitch effect model, given the original helper data  $\mathbf{w}$ .

```

1: procedure Attack(w)

\hat{c}_{-1} \leftarrow \textbf{0}

▷ Assumption: Data line is 0 before the transmission

2:

3:

for g \leftarrow -1 \dots n-2 do

4:

\mathbf{f} \leftarrow \text{Correction Limit}(q, t)

▷ Find suitable helper data bit flip vector

5:

if Experiment(\mathbf{w} \oplus \mathbf{f}, g, \theta^{\star}) fails then

6:

\hat{\mathbf{c}}_{g+1} \leftarrow \mathbf{not} \ \hat{\mathbf{c}}_g \oplus \mathbf{f}_g

\triangleright Consecutive bits differ

7:

else

8:

\hat{\mathbf{c}}_{g+1} \leftarrow \hat{\mathbf{c}}_g \oplus \mathbf{f}_g

▷ Current bit is the same as the last one

9:

return [\hat{\mathbf{c}}_0, \dots, \hat{\mathbf{c}}_{n-1}]

```

The helper data modification of the codeword bit before the glitch position also has to be accounted for. Lines 6 and 8 invert the recovered bit if  $\mathbf{w}_g$  had been flipped.

This algorithm only attempts to extract each bit once. To compensate measurement noise and glitch position jitter, it is sensible to run multiple trials of ATTACK on the same device and then use a majority vote on the extracted codeword bit differences.

Still, skewed results might occur if the fault effect is imperfect, i.e. if EXPERIMENT sometimes either succeeds or fails without data dependency, unbeknownst to the attacker. A compensation technique, which was employed in the experiments, is to replace the strict majority vote after collecting multiple trials with an adaptive threshold: instead of comparing the per-bit mean recovered difference with a fixed value of  $\frac{1}{2}$ , the average of all experiment results is used. The threshold is thus automatically adjusted based

on the assumption of equally probable bit difference values and uniform probability of non-data-dependency.  $^5$

**Data error correction.** Due to measurement noise or other imperfections, a perfect codeword extraction might not be possible in a real-world scenario. Since the attacker has knowledge of the system's inner construction and thus knows the system's error correcting code, they can use it to recover from some bit extraction errors. In the following, ENCODE and DECODE denote an encoding and error-correcting decoding operation using an equivalent implementation of the code used in the system under attack.

Since the extraction procedure operates on bit differences instead of the codeword bits directly, we define a vector of codeword bit differences  $\mathbf{d}$ ,

$$d_i := c_{i-1} \oplus c_i \quad \text{for } 0 \le i < n, \tag{2}$$

where  $c_{-1}$  is the state of the data line before the transmission of the first codeword bit  $c_0$ , which we assume to be 0 for now; if this information is unavailable,  $d_0$  contains the attacker's guess of the first codeword bit instead. A vector  $\hat{\mathbf{d}}$  for the attacker's extracted values is similarly defined using  $\hat{\mathbf{c}}$ .

One might be tempted to say that up to t wrongly recovered bits can be recovered by employing the ECC directly, because the original codeword  $\mathbf{c}$  is a valid codeword after all. However, this is not necessarily possible in the general case: a wrong bit in  $\hat{\mathbf{d}}$  compared to  $\mathbf{d}$  corresponds to bit errors in  $\hat{\mathbf{c}}$  from its position onward, often far more than a single bit flip. Therefore, even a single wrong bit in  $\hat{\mathbf{d}}$  might not be correctable.

Still, a number of errors in  $\hat{\mathbf{d}}$  can be corrected, depending on the qualities of the employed error-correction code. An important code class, to which also the BCH code used in this work belongs to, are *cyclic codes*, a subset of *linear codes*. In these, not only every linear combination of two codewords but also every cyclic shift of a codeword is a valid codeword, too [Bla03].

Note that the construction of **d** in Equation (2) almost makes it a cyclic codeword: if  $d_0$  were defined as  $c_{n-1} \oplus c_0$ , **d** would be a linear combination of **c** and a cyclic shift of **c** and thus a valid codeword. In our case, however, we can think of **d** as a codeword with one possible bit error in position 0 (which occurs if  $c_{n-1} = 1$ ).

A simple procedure making use of this property is presented as Algorithm 5, which uses Decode and Encode directly on the vector of extracted codeword bit differences. To compensate for the possible error due to the 'imperfect' cyclic codeword, it attempts the error correction on two variants, with and without bit 0 flipped and returns the variant where the error correction changed fewer positions.

Algorithm 5 Error-correct a word  $\hat{\mathbf{d}}$  of extracted codeword bit differences for a cyclic code.

```

1: procedure CORRECT DIFFERENCES(\hat{\mathbf{d}})

2: \hat{\mathbf{d}}_0 \leftarrow \hat{\mathbf{d}}, \hat{\mathbf{d}}_1 \leftarrow \hat{\mathbf{d}} \oplus \mathbf{e}_0 \triangleright Copy to \hat{\mathbf{d}}_0, invert bit 0 for \hat{\mathbf{d}}_1

3: \hat{\mathbf{d}}'_i \leftarrow \text{ENCODE}(\text{DECODE}(\hat{\mathbf{d}}_i)) \quad \forall i \in \{0,1\} \triangleright Error-correct both variants

4: if \text{HD}(\hat{\mathbf{d}}'_0, \hat{\mathbf{d}}_0) \leq \text{HD}(\hat{\mathbf{d}}'_1, \hat{\mathbf{d}}_1) then \triangleright Pick the variant with fewer errors

5: return \hat{\mathbf{d}}'_0

6: else

7: return \hat{\mathbf{d}}'_1 \oplus \mathbf{e}_0

```

A flipped bit 0 in  $\hat{\mathbf{d}}$  corresponds to an inversion of  $\hat{\mathbf{c}}$ . If the all-ones word is part of the code,  $\hat{\mathbf{c}}$  is just as valid a codeword as its inverted counterpart and an extraction error at position 0 is thus not detectable. If we assume a bit difference extraction error probability

<sup>&</sup>lt;sup>5</sup>Non-uniformity can be detectable during the profiling step as position-dependent fitness and be used during post-attack guessing or error correction.

| Experiment                                              | PUF noise                                         | HD manip.                      | Profiling                                                                     | Implementations                                            | Results in                                                              |

|---------------------------------------------------------|---------------------------------------------------|--------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------|-------------------------------------------------------------------------|

| Glitch effect Attack Attack Attack Attack Attack Attack | none<br>none<br>none<br>none<br>variable<br>fixed | yes<br>yes<br>yes<br>yes<br>no | on-device<br>on-device<br>on-device<br>on-device<br>on-device<br>cross-device | base<br>base<br>masked I<br>masked II<br>all three<br>base | Section 5.1<br>Section 5.2<br>Section 5.2<br>Section 5.3<br>Section 5.4 |

Table 1: Summary of all conducted experiments.

below  $\frac{1}{2}$ , a correct extraction of bit 0 is more likely than an extraction error. Thus, the original value of bit 0 is restored with the flip in line 7.

In case of a code with even minimum distance, the modification of bit 0 cannot erroneously move the codeword to a point closer to the wrong reconstruction; Algorithm 5 can thus reliably correct t errors apart from any error in position 0. For an odd minimum distance d=2t+1, this cannot be guaranteed and the bit difference error correction capability drops to t-1 bits. In the case of the BCH code used in the experiments, Algorithm 5 was found to reliably correct t errors after bit 0 despite the odd minimum distance d because d>2t+1.

## 4 Experimental set-up

Since the attack is mainly concerned with the serial codeword transmission between PUF and ECC decoder, no complete key storage system is implemented for the experiments. In particular, the PUF is replaced with a model and the derived key is not used in a cryptographic application. This section outlines the design choices behind the hardware model in terms of its scope and additional features, which facilitate a reasonably fast validation of the attack while representing a real-world system's behaviour realistically.

#### 4.1 Experiment scenarios

Within our attacker model, several slightly different experiment scenarios are possible, depending on the attacker's actual capabilities, the system under attack's design and the PUF's performance. To assess the attack's prospects in a broad range of scenarios, several experiments were carried out. Table 1 summarises the experiments and highlights their differences, e.g. if helper data manipulation or on-device profiling was considered in-scope for the attacker.

The base and masked implementations mentioned in Table 1 will be introduced in Section 4.2 and Section 4.3, respectively. In addition to these experiments focusing on the attack itself, results from the preceding profiling step with and without helper data manipulation are presented in Appendix C.

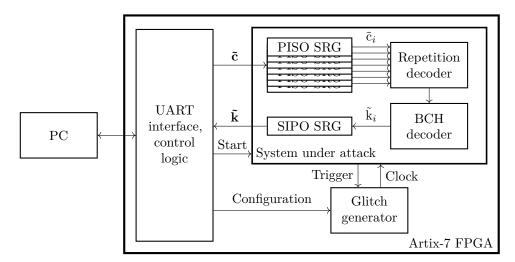

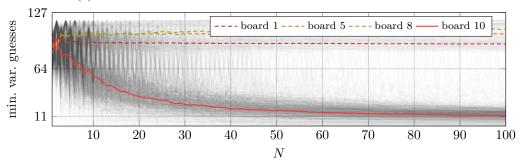

### 4.2 Basic experiment hardware

Figure 4 shows a block diagram of the experiment set-up: a Xilinx XC7A35T-1CPG236C FPGA contains both the system under attack and a clock glitch generator; all components are configured and communicated with using a UART interface. Naturally, this model carries a number of design choices and simplifications.

**PUF model.** As the proposed attack only needs the data transmission to the error correction code, the PUF itself lies beyond the scope of this work and its concrete implementation is not relevant.

For a practical setting, it can be expected that the PUF is either derived before the decoding starts, e.g. for an SRAM PUF, where the bits are available after power on of the

Figure 4: Simplified block diagram of the experiment set-up.

SRAM, or in parallel to the decoding, e.g., for an RO PUF. In the latter case, the PUF is measured for a long time and there is a low probability that a clock glitch skipping one clock cycle affects the PUF response significantly. In any case, it can be expected that data is buffered before fed into the repetition code.

Thus, the PUF is simulated by a programmable register in our design.<sup>6</sup> This simulated PUF makes our results independent of the actual PUF implementation.

For the first set of experiments, the PUF response was held constant, as PUF measurement noise can be compensated by averaging multiple attack runs. The hardware PUF model then enabled us to simulate differently reliable PUFs, as will be described in Section 4.4, to assess the impact of real-world PUF noise on the attack's feasibility.

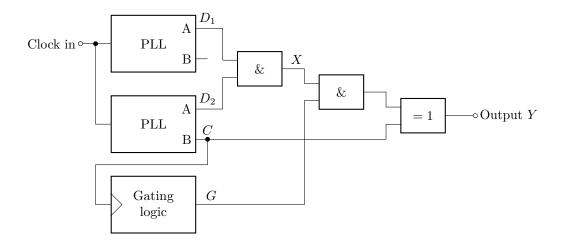

**Error correction code.** So far, the exact code used as the PUF system's error-correction measure was not important, as long as its codeword was transmitted serially. This work's implementation closely mirrors the code used in [MSS13] and [TPS17], i.e. a concatenated code consisting of a (7,1,3)-repetition code as its inner code and a (127,64,10)-BCH code as its outer code. BCH codes have been proposed and used in the context of PUF systems a number of times [Yu+12; Kan+14], sometimes in combination with a repetition code [MVV12]. They offer good performance and efficient hardware implementations and are thus suitable for the task (cf. Section 2.2).

Since the PUF value is initially assumed constant and the repetition decoder consists entirely of combinational logic, this part of the code concatenation is of little importance for the functional principle of this attack. It is still included in the hardware design because the propagation delay caused by its logic has an influence on the exact timing of the system. Therefore, the manipulation of one helper data bit in the attack described above corresponds to flipping one 7-bit block at the repetition decoder input.

The implementation of the BCH decoder has been generated using the software presented in [Jam97]. This code uses *systematic encoding*, i.e. the codeword is a concatenation of the 64-bit *symbol part*, which correspond to 64 key bits, and the 63-bit *redundancy part*, containing error correction information. To derive a 128-bit key two BCH code words would be used in practice.

<sup>&</sup>lt;sup>6</sup>Profiling and experiment results (cf. Section 5) for different configurations agree well with the fault model. Together with simulations explaining particular behaviours (cf. Section 5.1) they substantiate that indeed the targeted ECC decoder is attacked and not just the PUF model.

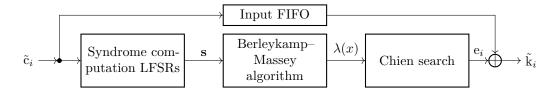

Figure 5: Block diagram of the BCH decoder hardware.

Figure 5 presents a block diagram of the BCH decoder's internal structure: LFSRs are used to compute the syndromes of the bit-serially supplied input, after which the  $error\ locator\ polynomial$  is determined. Based on that, the actual bit errors are calculated, which are than corrected in a stored copy of the input's first 64 bits. Since the input first-in first-out (FIFO) and the syndrome LFSRs use only a bit-wise serial input of  $\tilde{\mathbf{c}}$ , the described attack is directly applicable for this ECC implementation.

In this BCH implementation, the locations of the errors are determined using *Chien search*, i.e. by finding the roots of a polynomial of degree t [Jam97]. As this polynomial has at most t roots, exactly t bit errors can be corrected if all errors are within the symbol part of the codeword. Since we assume a constant PUF secret, which is the same for enrolment and reconstruction, this allows for a simplification of the attack: to bring the decoder to its error correction limit, Algorithm 1, which inserts a fixed number—t in the noise-free case—of bit flips, can be used instead of a more generic helper data modification scheme.

**Fuzzy commitment scheme implementation.** Only the reconstruction phase is implemented, as the enrolment phase is out of the attacker's control and not relevant to the attack. Thus, only the error correction based on simulated PUF secret and helper data is necessary. The usage of the reconstructed key is simulated by a comparison to a stored copy, yielding the pass/fail result.

Because the BCH has a bit-serial input, parallel-in serial-out (PISO) shift registers (SRGs) are used to convert from the parallel codeword to the serial decoder input, one for each repetition decoder input. These registers might also be present in a real-world implementation as part of a FIFO buffer to interface between the slow PUF and fast ECC decoder. Similarly, a serial-in parallel-out (SIPO) SRG is used to convert the reconstructed key to a parallel format.

**On-chip glitching.** We opted for on-chip glitching during our work as this approach allows us to perform experiments on several FPGAs simultaneously without requiring multiple physical glitch generator set-ups. The architecture of the on-chip glitch generator used in this work is based on the ChipWhisperer's design [OC15]. A more detailed look into its operating principle and performance is provided in Appendix B.

If a physical glitching set-up is used, the wiring between the device under test (DUT) and the glitch generator introduces a constant delay. In contrast to the off-chip glitching approach, this delay is very small for on-chip glitching. A physical glitching set-up's delay can be determined during the profiling phase for later compensation, as it does not change during the measurements.

In contrast to a real-world attacker, who would use an external glitch generator, on-chip glitching guarantees perfect glitch alignment with very low jitter. Contrarily, off-chip glitching is influenced by a certain amount of jitter, since optimal trigger signals for the external glitch generator might not be available. However, with an intelligent helper data modification scheme, glitch position jitter can be compensated with averaging (cf. Algorithm 1): a randomisation of a range of helper data bits ensures that measurement noise caused by imprecisely placed glitches appears as independent noise.

Lastly, if a physical glitching set-up is used, the whole DUT is affected by the glitch; in the on-chip glitching scenario only parts of the FPGA which form the model for the device under attack are influenced by the glitch. Nevertheless, we assume our model to be realistic as the whole ECC, the accompanying registers, and control logic are all wired to the on-chip glitch generator. This is essentially the same experiment setting as when the attack is conducted with a physical glitching set-up, e.g. with an ASIC design.

A comparison of both glitching techniques is shown in Table 2, where different parameters with respect to the according glitching technique are compared.

| Table 2. Comparison of on-/on-cmp gitting. |                                     |                                                                                  |  |  |  |  |  |

|--------------------------------------------|-------------------------------------|----------------------------------------------------------------------------------|--|--|--|--|--|

| Glitching technique                        |                                     |                                                                                  |  |  |  |  |  |

| Parameter                                  | On-chip glitching                   | External glitch generator                                                        |  |  |  |  |  |

| Jitter<br>Delay<br>Glitch target           | nearly none<br>none<br>device model | compensated by averaging/profiling<br>determined during profiling<br>real device |  |  |  |  |  |

Table 2: Comparison of on-/off-chip glitching.

## 4.3 Masking implementations

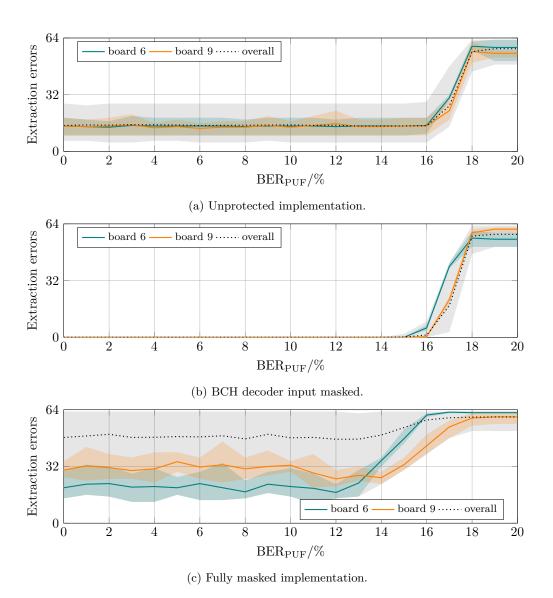

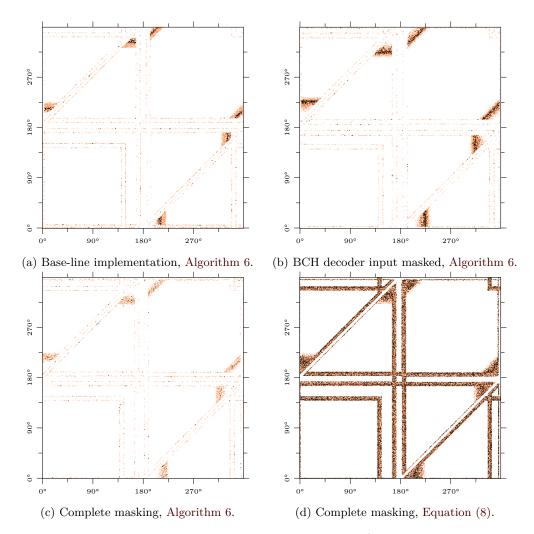

Masking is a well-known countermeasure against SCAs [Cha+99; RP10; GMK16]. By adding a random mask to a secret intermediate value, which is later removed again, masking effectively makes the intermediate value useless to the attacker without knowledge of the ephemeral mask. In the context of PUFs, masking has already been found successful against an SCA on a system similar to the one under consideration in this work [MSS13].

On a hardware implementation of a fuzzy-commitment-based PUF key storage system, masking of the decoder is nearly free in terms of required resources as the random number generator (RNG) and ECC encoder are likely already present for the enrolment phase and only an intermediate storage for the masking key and some control logic need to be added.

The principles of masking have also been used to provide protection against Statistical Ineffective Fault Analysis (SIFA) under the assumption of a SIFA-1 fault model [Sah+20], which assumes an alternation of parts of the shares.

Since SCA and FIA have a very similar attacker model, masking could be in place as an SCA countermeasure in our scenario. Although masking is known to be ineffective against FIA in the general case (i.e. apart from SIFA-1), it could be assumed to stifle this particular attack: since the attack extracts a single bit difference at a time, masking the codeword, thus randomising these bit differences, would—following our bit-level fault model—make the attack impossible.

The masking scheme in [MSS13] generates a random codeword of the ECC from a random seed and XORs it to the noisy codeword from the PUF in order to mask the decoding procedure. Removing the mask after decoding by XORing the random seed to the decoder output is possible due to linearity of the error correction code. We adapt this codeword masking scheme in order to analyse its impact on the prospects of a FIA.

Masking architecture. The ECC encoder was generated using the same software as the decoder to ensure a matching code. For the RNG, a 64 bit LFSR was instantiated using a polynomial from [Alf96]. Note that this is by no means a cryptographically secure RNG, which could be exploited in a more advanced attack. As the RNG's potential weaknesses are not the focus of this work, it is merely important that its output is (approximately) bias-free. To achieve this, the LFSR is left free-running and sampled once for each reconstruction phase. During the experiments, the codeword bits are attacked in random order to ensure any periodicity effects the LFSR might show cannot affect the results.

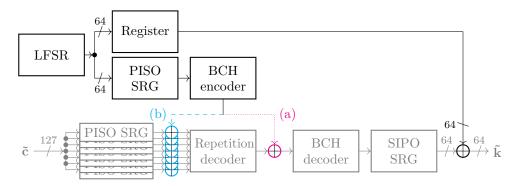

Two slightly different approaches are analysed in this work, shown in Figure 6. In the first one, (a), the random mask is applied to the BCH decoder's input. This scheme might

suffice to protect against side-channel attacks targeting the BCH decoder, as the attacks target the decoder's input FIFO, whose contents are now randomised.

A second, more complete variant, (b), applies the mask before the repetition decoder, thus masking the complete concatenated code. This implementation has the disadvantage of needing one XOR gate for each repetition decoder input and thus comes with a slightly higher hardware overhead.

Figure 6: Masking block diagram with control and clock signals omitted for brevity and the already present reconstruction phase circuit drawn in grey. Two masking implementations are tested: the codeword mask is either added (a) before the BCH decoder or (b) before the repetition decoder.

#### 4.4 PUF offset and noise simulation

As introduced in Section 2.3, we consider the deviation of the PUF response from the enrolment time response to consist of two parts, a constant offset term  $\Delta \mathbf{r}$  and a variable noise term  $\delta \mathbf{r}$ . These will be simulated in our experiments as follows:

**Offset.** Since  $\Delta \mathbf{r}$  is constant throughout the experiments and can be extracted by an attacker using Algorithm 2, it is assumed to be known by an attacker where helper data manipulation is possible. Since it can then be fully compensated by adding  $\Delta \mathbf{r}$  to the helper data, the offset term is set to zero for experiments with helper data manipulation.

If helper data manipulation is not available, the offset term can neither be extracted nor compensated by an attacker. To simulate it, a set number of bits is flipped in the codeword with the flip positions chosen uniform randomly once at the experiment's start.

**Noise.** For maximum generalisability, we model the PUF noise as i.i.d. for all bits of the PUF response. Note that this is not necessarily the case for a real-world PUF, where different bits commonly have different reliability; on the other hand, any non-uniformity in the error distribution over the codeword bits can be used to the attacker's advantage by prioritising less reliable bits during the post-attack guessing or error correction.

Since the modelled system architecture contains a concatenated code, the PUF noise has to be considered to be present at the input of the inner (7,1,3) repetition code. The bit error rate (BER) at the input of the BCH decoder, after repetition decoder with odd  $n_{\rm rep}$ , can be calculated from the PUF BER as:

$$BER_{BCH} = \sum_{i=(n_{rep}+1)/2}^{n_{rep}} {n_{rep} \choose i} (BER_{PUF})^i (1 - BER_{PUF})^{n_{rep}-i}$$

(3)

$$= \sum_{i=4}^{7} {7 \choose i} (BER_{PUF})^{i} (1 - BER_{PUF})^{7-i}$$

(4)

Throughout the experiments, PUF noise was simulated by Bernoulli-sampling all n bits of  $\delta \mathbf{r}$  with the probability BER<sub>BCH</sub> before each fault injection experiment.  $\delta \mathbf{r}$  can then, together with the constant  $\Delta \mathbf{r}$ , be XORed with the codeword.

## 4.5 Experiment procedure

For a representative evaluation, experiments were carried out on 15 FPGA boards. For all tested implementation variants, an attack procedure based on two phases was carried out independently for each board:

- Profiling. Before a codeword was extracted, the optimal glitch parameters were determined using Algorithm 3. To match a realistic scenario, where an attacker cannot choose or change the system's codeword, as closely as possible, a single random codeword per FPGA board was used for the profiling stage. To limit operator bias, the maximum was found using a peak search on FITNESS evaluations of uniformly random glitch parameters, which required a comparatively high number of 250 000 samples. An attacker can employ a guided search or pick the timings manually, requiring considerably fewer data points. Results of the profiling step, shown in Appendix C, provide additional support to our fault model.

- Attack. Using the per-FPGA optimal glitch timings, the attack was carried out using Algorithm 4. 250 trials of this algorithms were used for 100 random attacked codewords per FPGA. To monitor the attack as it progressed, the extracted codeword bit differences were computed on-line based on the average of the current trials.

- The number N of trials corresponds directly to the total number of glitches needed for the attack since each trial consists of 127 fault injection experiments. If only the key part of the codeword was attacked, the total number of glitches would be  $64 \cdot N$ .

## 4.6 Attack success metrics

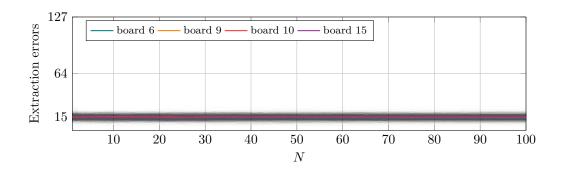

After extracting a secret codeword from a device, the number of bit extraction errors gives a first indication for the attack's success. However, since the position of any extraction errors is unknown to the attacker, they need, in general, to guess more than this number of bits to reach the correct secret. This section discusses different metrics for bit guessing after the attack, used during the experiments to assess the attack's power.

Since the attacker can only extract bit differences between subsequent bits, it is sensible to judge their success based on the number of correct bit differences. In the following, 'bit extraction errors' refer to errors in the bit *differences* of codeword and, respectively, key.

Residual guess entropy (RGE). Lacking any further information, a sensible approach for an attacker would be to guess codewords based on their error count, i.e. the attacker would try all codewords with one bit flip respective to their extracted value, then two additional bit flips, and so on. An upper bound of the number of bits the attacker needs to guess to find x bit errors in an l-bit word is the max-entropy:

$$RGE(x,l) = \log_2 \left( \sum_{i=0}^x {l \choose i} \right).$$

(5)

<sup>&</sup>lt;sup>7</sup>A cross-check repeating the experiments on a subset of the FPGAs with different codewords did not reveal any dependence on the particular codeword.

If the system under attack uses systematic encoding, i.e. the key bits are available directly as a subset of the codeword bits, the attacker can try to only extract these key bits. If x bit extraction errors were made during that process, the residual guess entropy for the key-only attack becomes

$$RGE_{\hat{\mathbf{L}}}(x) := RGE(k, x). \tag{6}$$

As previously discussed, if a cyclic code is used, its decoder can be used by an attacker to error-correct their extracted codeword. For simplicity, we assume that the attacker will always guess bit 0 due to its special role and will be able to correct t bit extraction errors among the remaining codeword bits. The RGE thus becomes

$$RGE_{\hat{\mathbf{c}}}(x_{1+}) := \begin{cases} 1 & \text{for } x_{1+} \le t \\ 1 + RGE(n-1, x_{1+} - t) & \text{otherwise} \end{cases}$$

, (7)

where  $x_{1+}$  is the number of bit extraction errors for the codeword bits 1 to n-1.

Note that either strategy can be better. For low extraction error counts, a significant part can be error-corrected if the complete codeword is extracted, whereas  $\mathrm{RGE}_{\hat{\mathbf{c}}} > \mathrm{RGE}_{\hat{\mathbf{k}}}$  for higher error counts, since the attacker has to find the errors within n > k bit positions. For example, for the (127,64,10)-code used for the experiments, extracting the whole codeword leads to a lower residual guess entropy only if there are less than 16 bit extraction errors (assuming an equal distribution of errors within the codeword).

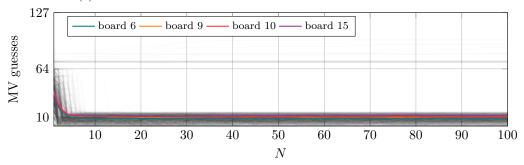

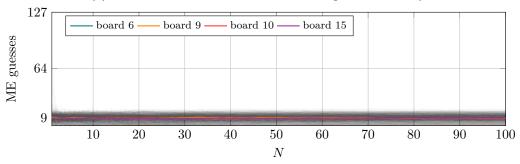

**Smart guessing strategies.** If additional information about the system is known, an attacker can guess bits more intelligently. We consider two approaches:

Maximum-variance (MV) guessing. As multiple fault injection experiments are carried out for each codeword bit to compensate for measurement noise by averaging, estimating the measurement variance per bit is possible. This variance intuitively maps to a confidence in the extracted bit and an attacker can try to guess bits in order of decreasing measurement variance.

This metric is computed as the number of bits, as ordered by their measurement variance, which need to be adapted for all extraction errors to be compensated or until the remaining errors can be corrected using the ECC. As with the residual guess entropy, bit 0 is always adapted first in the case of a codeword extraction.

Maximum error probability (ME) guessing. In some cases, an attacker might be able to profile the attack more extensively or in other ways obtain information at which positions a secret extraction is less likely succeed. They would then adapt the bit positions with the highest extraction error probability first.

In the experiments, this metric is calculated a-posteriori, using the collected data from all boards to estimate all bit positions' extraction error probabilities. The number of bits to be flipped to reach a correct key/codeword is then determined analogously to the MV guess count.

## 5 Experiment results

Using the procedure outlined in Section 4.5, 15 FPGA boards were used to carry out 100 attacks on randomly chosen secret keys each. This section presents the results of each implementation variant's 1500 attack experiment results, highlighting boards showing representative behaviour. The results of the preceding profiling step are detailed in Appendix C.

## 5.1 Base-line implementation

Before examining the proposed countermeasure, we first demonstrate the attack's feasibility on the base-line implementation. This section begins with a short analysis of the clock glitch's influence on the system before proceeding with the actual attack results.

Error correction limit under glitch influence. Following the argumentation of Section 3.2, we would expect a clock glitch to have no effect at all for fewer than t bit flips in the (fault-less) codeword because the decoder can always recover from a single additional error. However, reconstruction failures were already observed for much fewer helper data bit flips.

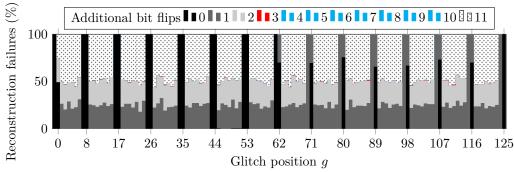

To analyse this behaviour, 250 random 64-bit keys were encoded and the effects of a glitch at each codeword bit position was recorded for different number of helper data bit flips. The previously determined optimum glitch timing was used and the 0 to 11 helper data bit flips' positions were chosen at random within the k symbol bits of the codeword, excluding the glitch position g and g-1.

(a) Share of reconstruction failures when introducing a clock glitch at a specific position.

(b) Observed data dependency of the fault injection results.

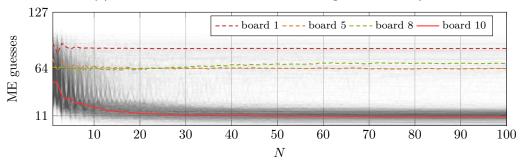

Figure 7: Fault injection behaviour depending on the number of inserted helper data bit flips, based on experiments with 250 random codewords.

Figure 7a shows the share of the recorded reconstruction failures for each glitch position; the number of additional bit flips at which the reconstructions start to fail is indicated by the bars' colours. As expected, all reconstructions fail at t+1 bit errors, since the flip positions do not permit a compensation by the clock glitch. Note that only very small red regions are visible, i.e. very few reconstruction failures occurred at 3 bit flips which did not occur at 2 or fewer bit flips. The colour cyan is completely absent: from 3 to 9 bit flips, the behaviour does not change.

Thus, reconstructions start to fail much earlier than at t bit flips. First, a number of glitch positions, visible as regularly spaced black vertical bars, lead to a reconstruction

Figure 8: Bit extraction error probability over the bit position, estimated from all experiments.

failure in every case, even without any helper data manipulation. These glitch positions thus cannot exhibit any useful data dependency.<sup>8</sup> Since they coincide with two control signals with 9-bit period, it is likely that a glitch at these positions disturbs the decoder's internal control logic, affecting the reconstructed key.

Second, even with one bit of helper data manipulation, a significant share of clock-glitched reconstructions begins to fail. Even more so, with the exception of a few cases at three bit flips (drawn in red), the experiment's outcomes do not change from two to ten bit flips and no cyan is visible in Figure 7a. This is more directly visible in Figure 7b, where the share of pass/fail results in line with the set-up time violation model is shown depending on the number of additionally inserted bit flips. In simulations, a similar behaviour occurred when some syndrome LFSRs were left unaffected by the clock glitch, which also fits the intuition: as soon as the syndrome computation units become desynchronised, the error correction capability suffers.

However, since a behaviour like this cannot be presumed from a general system under attack, the majority of the attacks in the remainder of this section are carried out as they were described earlier, with helper data manipulation bringing the error-correcting code to its error correction limit before the insertion of clock glitches. Since the observable data dependency, as Figure 7b shows, is not worse for this case, this approach does not degrade the attack's performance. The evidently exploitable data dependency for fewer artificially introduced bit flips allowed for an attack without helper data manipulation in Section 5.4.

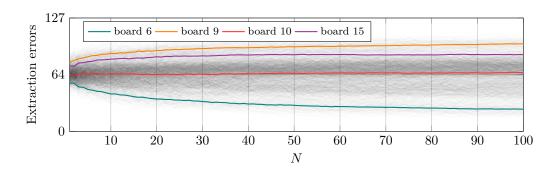

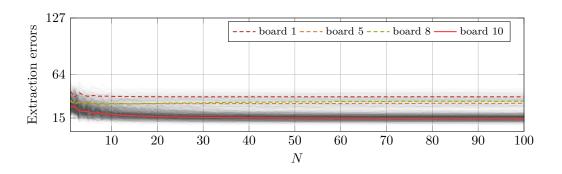

**Attack results.** As expected, the bit positions without or with limited data dependency highlighted in Figure 7a and discussed in the previous section also appear during the attack as bit positions with high extraction error probability. Figure 8 shows the indeterminable bits (i.e. with 50% error probability) with their regular 9-bit spacing.

Apart from these positions, Figure 8 only has a very small 'error floor', indicating that the attack performs well with respect to measurement noise. This is corroborated by the attack's progress on the number of extraction errors within a codeword over the number of trials in Figure 9a, which is mostly constant despite a growing number of averages.