# Time-Optimal Interactive Proofs for Circuit Evaluation

Justin Thaler \*

#### Abstract

Several research teams have recently been working toward the development of practical generalpurpose protocols for verifiable computation. These protocols enable a computationally weak *verifier* to offload computations to a powerful but untrusted *prover*, while providing the verifier with a guarantee that the prover performed the requested computations correctly. Despite substantial progress, existing implementations require further improvements before they become practical for most settings. The main bottleneck is typically the extra effort required by the prover to return an answer with a guarantee of correctness, compared to returning an answer with no guarantee.

We describe a refinement of a powerful interactive proof protocol due to Goldwasser, Kalai, and Rothblum [21]. Cormode, Mitzenmacher, and Thaler [14] show how to implement the prover in this protocol in time  $O(S \log S)$ , where S is the size of an arithmetic circuit computing the function of interest. Our refinements apply to circuits with sufficiently "regular" wiring patterns; for these circuits, we bring the runtime of the prover down to O(S). That is, our prover can evaluate the circuit with a guarantee of correctness, with only a constant-factor blowup in work compared to evaluating the circuit with no guarantee.

We argue that our refinements capture a large class of circuits, and we complement our theoretical results with experiments on problems such as matrix multiplication and determining the number of distinct elements in a data stream. Experimentally, our refinements yield a 200x speedup for the prover over the implementation of Cormode et al., and our prover is less than 10x slower than a C++ program that simply evaluates the circuit. Along the way, we describe a special-purpose protocol for matrix multiplication that is of interest in its own right.

Our final contribution is the design of an interactive proof protocol targeted at general data parallel computation. Compared to prior work, this protocol can more efficiently verify complicated computations as long as that computation is applied independently to many different pieces of data.

<sup>\*</sup>Harvard University, School of Engineering and Applied Sciences. Supported by an NSF Graduate Research Fellowship and NSF grants CNS-1011840 and CCF-0915922.

# Contents

| 1 | Intro | oduction 4                                                                                                                                               |

|---|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 1.1   | Prior Work                                                                                                                                               |

|   |       | 1.1.1 Work on Interactive Proofs                                                                                                                         |

|   |       | 1.1.2 Work on Argument Systems                                                                                                                           |

|   | 1.2   | Our Contributions                                                                                                                                        |

|   | 1.3   | Roadmap                                                                                                                                                  |

|   |       | -                                                                                                                                                        |

| 2 |       | iminaries 7                                                                                                                                              |

|   | 2.1   | Definitions                                                                                                                                              |

|   |       | 2.1.1 Cost Model                                                                                                                                         |

|   |       | 2.1.2 Problem Definitions                                                                                                                                |

|   |       | 2.1.3 Additional Notation                                                                                                                                |

| 3 | Over  | rview of the Ideas                                                                                                                                       |

| 5 | 3.1   | The GKR Protocol From 10,000 Feet                                                                                                                        |

|   | 3.2   | Achieving Optimal Prover Runtime for Regular Circuits                                                                                                    |

|   | 3.3   | Verifying General Data Parallel Computations                                                                                                             |

|   | 3.4   | A Special-Purpose Protocol for MATMULT                                                                                                                   |

|   | Э.т   |                                                                                                                                                          |

| 4 | Tech  | nical Background 12                                                                                                                                      |

|   | 4.1   | Schwartz-Zippel Lemma                                                                                                                                    |

|   | 4.2   | Sum-Check Protocol                                                                                                                                       |

|   |       | 4.2.1 Discussion of costs                                                                                                                                |

|   | 4.3   | The GKR Protocol                                                                                                                                         |

|   |       | 4.3.1 Notation                                                                                                                                           |

|   |       | 4.3.2 Protocol Outline                                                                                                                                   |

|   |       | 4.3.3 Details for Each Iteration                                                                                                                         |

|   |       | 4.3.4 Discussion of Costs                                                                                                                                |

|   |       | 4.3.5 Making $\mathcal{V}$ Fast vs. Making $\mathcal{V}$ Streaming                                                                                       |

| 5 | Tim   | e-Optimal Protocols for Circuit Evaluation 17                                                                                                            |

| 5 | 5.1   | Protocol Outline and Section Roadmap                                                                                                                     |

|   | 5.2   | A Preliminary Lemma                                                                                                                                      |

|   | 5.3   | Polynomials for Specific Circuits                                                                                                                        |

|   | 5.5   | 5.3.1 The Polynomial for a Binary Tree                                                                                                                   |

|   |       | 5.3.2 The Polynomials for DISTINCT                                                                                                                       |

|   | 5.4   | Reusing Work       20                                                                                                                                    |

|   | э.т   | 5.4.1 Computing the Necessary $\beta(z, p)$ Values                                                                                                       |

|   |       | 5.4.2 Computing the Necessary $\tilde{V}_{i+1}(p)$ Values                                                                                                |

|   | 5.5   | A General Theorem $\ldots \ldots \ldots$ |

|   | 5.5   | 5.5.1 Applications                                                                                                                                       |

|   |       | 5.5.1 Approviding                                                                                                                                        |

| 6 | Exp  | eriment   | tal Results                         | 27   |

|---|------|-----------|-------------------------------------|------|

|   | 6.1  | Summa     | ary of Results                      | . 28 |

|   | 6.2  | Details   | 8                                   | . 28 |

|   |      | 6.2.1     | Serial Implementation               | . 29 |

|   |      | 6.2.2     | Parallel Implementation             | . 30 |

| 7 | Veri | fying G   | eneral Data Parallel Computations   | 31   |

|   | 7.1  | Motiva    | ation                               | . 32 |

|   | 7.2  | Overvi    | iew of the Protocol                 | . 33 |

|   | 7.3  | Techni    | cal Details                         | . 34 |

|   |      | 7.3.1     | Notation                            | . 34 |

|   |      | 7.3.2     | Main Theorem                        | . 34 |

| 8 | Exte | ensions   |                                     | 36   |

|   | 8.1  | Binary    | <sup>7</sup> Tree of Addition Gates | . 36 |

|   | 8.2  | Optima    | al Space and Time Costs for MATMULT | . 38 |

|   |      | 8.2.1     | Comparison to Prior Work            | . 38 |

|   |      | 8.2.2     | Protocol Details                    | . 40 |

| 9 | Con  | clusion   |                                     | 41   |

| A | Proc | of of Th  | eorem 1                             | 44   |

| B | Ana  | lysis for | r Pattern Matching                  | 48   |

# **1** Introduction

Protocols for verifiable computation enable a computationally weak *verifier*  $\mathcal{V}$  to offload computations to a powerful but untrusted *prover*  $\mathcal{P}$ . These protocols aim to provide the verifier with a guarantee that the prover performed the requested computations correctly, without requiring the verifier to perform the computations herself.

Surprisingly powerful protocols for verifiable computation were discovered within the computer science theory community several decades ago, in the form of interactive proofs (IPs) and their brethren, interactive arguments (IAs) and probabilistically checkable proofs (PCPs). In these protocols, the prover  $\mathcal{P}$  solves a problem using her (possibly vast) computational resources, and tells  $\mathcal{V}$  the answer.  $\mathcal{P}$  and  $\mathcal{V}$  then have a conversation, i.e., they engage in a randomized protocol involving the exchange of one or more messages. During this conversation,  $\mathcal{P}$ 's goal is to convince  $\mathcal{V}$  that the answer is correct.

Results quantifying the power of IPs, IAs, and PCPs represent some of the most celebrated results in all of computational complexity theory, but until recently they were mainly of theoretical interest, far too inefficient for actual deployment. In fact, the main applications of these results have traditionally been in negative applications – showing that many problems are just as hard to approximate as they are to solve exactly.

However, the surging popularity of cloud computing has brought renewed interest in positive applications of protocols for verifiable computation. A typical motivating scenario is as follows. A business processes billions or trillions of transactions a day. The volume is sufficiently high that the business cannot or will not store and process the transactions on its own. Instead, it offloads the processing to a commercial cloud computing service. The offloading of any computation raises issues of trust: the business may be concerned about relatively benign events like dropped transactions, buggy algorithms, or uncorrected hardware faults, or the business may be more paranoid and fear that the cloud operator is deliberately deceptive or has been externally compromised. Either way, each time the business poses a query to the cloud, the business may demand that the cloud also provide a guarantee that the returned answer is correct.

This is precisely what protocols for verifiable computation accomplish, with the cloud acting as the prover in the protocol, and the business acting as the verifier. In this paper, we describe a refinement of an existing general-purpose protocol originally due to Goldwasser, Kalai, and Rothblum [14, 21]. When they are applicable, our techniques achieve asymptotically optimal runtime for the prover, and we demonstrate that they yield protocols that are significantly closer to practicality than that achieved by prior work.

We also make progress toward addressing another issue of existing interactive proof implementations: their applicability. The protocol of Goldwasser, Kalai, and Rothblum (henceforth the GKR protocol) applies in principle to any problem computed by a small-depth arithmetic circuit, but this is not the case when more fine-grained considerations of prover and verifier efficiency are taken into account. In brief, existing implementations of interactive proof protocols for circuit evaluation all require that the circuit have a highly regular wiring pattern [14, 40]. If this is not the case, then these implementations require the verifier to perform an expensive (though data-independent) preprocessing phase to pull out information about the wiring of the circuit, and they require a substantial factor blowup (logarithmic in the circuit size) in runtime for the prover relative to evaluating the circuit without a guarantee of correctness. Developing a protocol that avoids these pitfalls and applies to more general computations remains an important open question.

Our approach is the following. We do not have a magic bullet for dealing with irregular wiring patterns; if we want to avoid an expensive pre-processing phase for the verifier and minimize the blowup in runtime for the prover, we do need to make an assumption about the structure of the circuit we are verifying. Acknowledging this, we ask whether there is some general structure in real-world computations that we can

leverage for efficiency gains.

To this end, we design a protocol that is highly efficient for data parallel computation. By data parallel computation, we mean any setting in which one applies the same computation independently to many pieces of data. Many outsourced computations are data parallel, with Amazon Elastic MapReduce<sup>1</sup> being one prominent example of a cloud computing service targeted specifically at data parallel computations. Crucially, we do not want to make significant assumptions on the sub-computation that is being applied, and in particular we want to handle sub-computations computed by circuits with highly irregular wiring patterns.

The verifier in our protocol still has to perform an offline phase to pull out information about the wiring of the circuit, but the cost of this phase is proportional to the size of a single instance of the sub-computation, avoiding any dependence on the number of pieces of data to which the sub-computation is applied. Similarly, the blowup in runtime suffered by the prover is the same as it would be if the prover had run the basic GKR protocol on a single instance of the sub-computation.

Our final contribution is to describe a new protocol specific to matrix multiplication that is of interest in its own right. It avoids circuit evaluation entirely, and reduces the overhead of the prover (relative to running *any* unverifiable algorithm) to an additive low-order term.

### 1.1 Prior Work

### 1.1.1 Work on Interactive Proofs.

Goldwasser, Kalai, and Rothblum described a powerful general-purpose interactive proof protocol in [21]. This protocol is framed in the context of *circuit evaluation*. Given a layered arithmetic circuit *C* of depth *d*, size S(n), and fan-in 2, the GKR protocol allows a prover to evaluate *C* with a guarantee of correctness in time poly(S(n)), while the verifier runs in time  $\tilde{O}(n + d \log S(n))$ , where *n* is the length of the input and the  $\tilde{O}$  notation hides polylogarithmic factors in *n*.

Cormode, Mitzenmacher, and Thaler showed how to bring the runtime of the prover in the GKR protocol down from poly(S(n)) to O(S(n) log S(n)) [14]. They also built a full implementation of the protocol and ran it on benchmark problems. These results demonstrated that the protocol does indeed save the verifier significant time in practice (relative to evaluating the circuit locally); they also demonstrated surprising scalability for the prover, although the prover's runtime remained a major bottleneck. With the implementation of [14] as a baseline, Thaler et al. [38] described a parallel implementation of the GKR protocol that achieved 40x-100x speedups for the prover and 100x speedups for the (already fast) implementation of the verifier.

Vu, Setty, Blumberg, and Walfish [40] further refine and extend the implementation of Cormode et al. [14]. In particular, they combine the GKR protocol with a compiler from a high-level programming language so that programmers do not have to explicitly express computation in the form of arithmetic circuits as was the case in the implementation of [14]. This substantially extends the reach of the implementation, but it should be noted that their approach generates circuits with irregular wiring patterns, and hence only works in a *batching* model, where the cost of a fairly expensive offline setup phase is amortized by verifying many instances of a single computation in batch. They also build a hybrid system that statically evaluates whether it is better to use the GKR protocol or a different, cryptography-based argument system called Zaatar (see Section 1.1.2), and runs the more efficient of the two protocols in an automated fashion.

A growing line of work studies protocols for verifiable computation in the context of *data streaming*. In this context, the goal is not just to save the verifier time (compared to doing the computation without a prover), but also to save the verifier space. The protocols developed in this line of work allow the client to

<sup>&</sup>lt;sup>1</sup>http://aws.amazon.com/elasticmapreduce/

make a single streaming pass over the input (which can occur, for example, while the client is uploading data to the cloud), keeping only a very small summary of the data set. The interactive version of this model was introduced by Cormode, Thaler, and Yi [15], who observed that many protocols from the interactive proofs literature, including the GKR protocol, can be made to work in this restrictive setting. The observations of [15] imply that all of our protocols also work with streaming verifiers. Non-interactive variants of the streaming interactive proofs model have also been studied in detail [12, 13, 23, 27].

### 1.1.2 Work on Argument Systems.

There has been a lot of work on the development of efficient interactive arguments, which are essentially interactive proofs that are secure only against dishonest provers that run in polynomial time. A substantial body of work in this area has focused on the development of protocols targeted at specific problems (e.g. [2, 5, 16]). Other works have focused on the development of general-purpose argument systems. Several papers in this direction (e.g. [8, 10, 11, 18]) have used fully homomorphic encryption, which unfortunately remains impractical despite substantial recent progress. Work in this category by Chung et al. [10] focuses on streaming settings, and is therefore particularly relevant.

Several research teams have been pursuing the development of general-purpose argument systems that might be suitable for practical use. Theoretical work by Ben-Sasson et al. [4] focuses on the development of short PCPs that might be suitable for use in practice – such PCPs can be compiled into efficient interactive arguments. As short PCPs are often a bottleneck in the development of efficient argument systems, other works have focused on avoiding their use [3,6,7,19]. In particular, Gennaro et al. [19] and Bitansky et al. [9] develop argument systems with a clear focus on implementation potential. Very recent work by Parno et al. [30] describes a near-practical general-purpose implementation, called Pinocchio, of an argument system based on [19]. Pinocchio is additionally non-interactive and achieves public verifiability.

Another line of implementation work focusing on general-purpose interactive argument systems is due to Setty et al. [34–36]. This line of work begins with a base argument system due to Ishai et al. [25], and substantially refines the theory to achieve an implementation that approaches practicality. The most recent system in this line of work is called Zaatar [36], and is also based on the work of Gennaro et al. [19]. An empirical comparison of the GKR-based approach and Zaatar performed by Vu et al. [40] finds the GKR approach to be significantly more efficient for quasi-straight-line computations (e.g. programs with relatively simple control flow), while Zaatar is appropriate for programs with more complicated control flow.

### **1.2 Our Contributions**

Our primary contributions are three-fold. Our first contribution addresses one of the biggest remaining obstacles to achieving a truly practical implementation of the GKR protocol: the logarithmic factor overhead for the prover. That is, Cormode et al. show how to implement the prover in time  $O(S(n) \log S(n))$ , where S(n) is the size of the arithmetic circuit to which the GKR protocol is applied, down from the  $\Omega(S(n)^3)$  time required for a naive implementation. The hidden constant in the Big-Oh notation is at least 3, and the  $\log S(n)$  factor translates to well over an order of magnitude, even for circuits with a few million gates.

We remove this logarithmic factor, bringing  $\mathcal{P}$ 's runtime down to O(S(n)) for a large class of circuits. Informally, our results apply to any circuit whose wiring pattern is sufficiently "regular". We formalize the class of circuits to which our results apply in Theorem 1.

We experimentally demonstrate the generality and effectiveness of Theorem 1 via two case studies. Specifically, we apply an implementation of the protocol of Theorem 1 to a circuit computing matrix multiplication (MATMULT), as well as to a circuit computing the number of distinct items in a data stream

(DISTINCT). Experimentally, our refinements yield a 200x-250x speedup for the prover over the state of the art implementation of Cormode et al. [14]. A serial implementation of our prover is less than 10x slower than a C++ program that simply evaluates the circuit sequentially, a slowdown that is tolerable in realistic outsourcing scenarios where cycles are plentiful for the prover. Moreover, a parallel implementation of our prover using a graphics processing unit (GPU) is roughly 30x faster than our serial implementation, and therefore takes less time than that required to evaluate the circuit in serial.

Our second contribution is to specify a highly efficient protocol for verifiably outsourcing arbitrary data parallel computation. Compared to prior work, this protocol can more efficiently verify complicated computations, as long as that computation is applied independently to many different pieces of data. We formalize this protocol and its efficiency guarantees in Theorem 2.

Our third contribution is to describe a new protocol specific to matrix multiplication that we believe to be of interest in its own right. This protocol is formalized in Theorem 3. Given any *unverifiable* algorithm for  $n \times n$  matrix multiplication that requires time T(n) using space s(n), Theorem 3 allows the prover to run in time  $T(n) + O(n^2)$  using space  $s(n) + o(n^2)$ . Note that Theorem 3 (which is specific to matrix multiplication) is much less general than Theorem 1 (which applies to any circuit with a sufficiently regular wiring pattern). However, Theorem 3 achieves optimal runtime and space usage for the prover up to leading constants, assuming there is no  $O(n^2)$  time algorithm for matrix multiplication. While these properties are also satisfied by a classic protocol due to Freivalds [17], the protocol of Theorem 3 is significantly more amenable for use as a primitive when verifying computations that repeatedly invoke matrix multiplication. For example, using the protocol of Theorem 3 as a primitive, we give a natural protocol for computing the diameter of an unweighted directed graph G.  $\mathcal{V}$ 's runtime in this protocol is  $O(m \log n)$ , where m is the number of edges in G,  $\mathcal{P}$ 's runtime matches the best known unverifiable diameter algorithm up to a low-order additive term [33,42], and the total communication is just polylog(n). We know of no other protocol achieving this.

We complement Theorem 3 with experimental results demonstrating its efficiency.

### 1.3 Roadmap

Section 2 presents preliminaries. We give a high-level overview of the ideas underlying our main results in Section 3. Section 4 gives a detailed overview of prior work, including the standard sum-check protocol as well as the GKR protocol. Section 5 contains the details of our time-optimal protocol for circuit evaluation as formalized in Theorem 1. Section 6 describes our experimental cases studies of the protocol described in Theorem 1. Section 7 describes our protocol for arbitrary data parallel computation. Section 8 describes some additional optimizations that apply to specific important wiring patterns. In particular, this section describes our special-purpose protocol for MATMULT that achieves optimal prover efficiency up to leading constants. Section 9 concludes.

### 2 Preliminaries

### 2.1 Definitions

We begin by defining a valid interactive proof protocol for a function f.

**Definition 1** Consider a prover  $\mathcal{P}$  and verifier  $\mathcal{V}$  who both observe an input x and wish to compute a function  $f: \{0,1\}^n \to \mathcal{R}$  for some set  $\mathcal{R}$ . After the input is observed,  $\mathcal{P}$  and  $\mathcal{V}$  exchange a sequence of messages. Denote the output of  $\mathcal{V}$  on input x, given prover  $\mathcal{P}$  and  $\mathcal{V}$ 's random bits R, by  $out(\mathcal{V}, x, R, \mathcal{P})$ .  $\mathcal{V}$  can output  $\perp$  if  $\mathcal{V}$  is not convinced that  $\mathcal{P}$ 's claim is valid.

We say  $\mathcal{P}$  is a valid prover with respect to  $\mathcal{V}$  if for all inputs x,  $Pr_R[out(\mathcal{V}, x, R, \mathcal{P}) = f(x)] = 1$ . The property that there is at least one valid prover  $\mathcal{P}$  with respect to  $\mathcal{V}$  is called completeness. We say  $\mathcal{V}$  is a valid verifier for f with soundness probability  $\delta$  if there is at least one valid prover  $\mathcal{P}$  with respect to  $\mathcal{V}$ , and for all provers  $\mathcal{P}'$  and all inputs x,  $Pr[out(\mathcal{V}, A, R, \mathcal{P}') \notin \{f(x), \bot\}] \leq \delta$ . We say a prover-verifier pair  $(\mathcal{P}, \mathcal{V})$  is a valid interactive proof protocol for f if  $\mathcal{V}$  is a valid verifier for f with soundness probability 1/3, and  $\mathcal{P}$  is a valid prover with respect to  $\mathcal{V}$ . If  $\mathcal{P}$  and  $\mathcal{V}$  exchange r messages in total, we say the protocol has  $\lceil r/2 \rceil$  rounds.

Informally, the completeness property guarantees that an honest prover will convince the verifier that the claimed answer is correct, while the soundness property ensures that a dishonest prover will be caught with high probability. An *interactive argument* is an interactive proof where the soundness property holds only against polynomial-time provers  $\mathcal{P}'$ . We remark that the constant 1/3 used for the soundness probability in Definition 1 is chosen for consistency with the interactive proofs literature, where 1/3 is used by convention. In our actual implementation, the soundness probability will always be less than  $2^{-45}$ .

### 2.1.1 Cost Model

Whenever we work over a finite field  $\mathbb{F}$ , we assume that a single field operation can be computed in a single machine operation. For example, when we say that the prover  $\mathcal{P}$  in our interactive protocols requires time O(S(n)), we mean that  $\mathcal{P}$  must perform O(S(n)) additions and multiplications within the finite field over which the protocol is defined.

**Input Representation.** Following prior work [12, 14, 15], all of the protocols we consider can handle inputs specified in a general data stream form. Each element of the stream is a tuple  $(i, \delta)$ , where  $i \in [n]$  and  $\delta$  is an integer. The  $\delta$  values may be negative, thereby modeling deletions. The data stream implicitly defines a frequency vector a, where  $a_i$  is the sum of all  $\delta$  values associated with i in the stream. For simplicity, we assume throughout the paper that the number of stream updates m is related to n by a constant factor i.e.,  $m = \Theta(n)$ .

When checking the evaluation of a circuit C, we consider the inputs to C to be the entries of the frequency vector a. We emphasize that in all of our protocols, V only needs to see the raw stream and not the aggregated frequency vector a (see Lemma 2 for details). Notice that we may interpret the frequency vector a as an object other than a vector, such as a matrix or a string. For example, in MATMULT, the data stream defines two matrices to be multiplied.

When we refer to a *streaming verifier* with space usage s(n), we mean that the verifier can make a single pass over the stream of tuples defining the input, regardless of their ordering, while storing at most s(n) elements in the finite field over which the protocol is defined.

### 2.1.2 **Problem Definitions**

To focus our discussion in this paper, we give special attention to two problems also considered in prior work [14,38].

- 1. In the MATMULT problem, the input consists of two  $n \times n$  matrices  $A, B \in \mathbb{Z}^{n \times n}$ , and the goal is to compute the matrix product  $A \cdot B$ .

- 2. In the DISTINCT problem, also denoted  $F_0$ , the input is a data steam consisting of *m* tuples  $(i, \delta)$  from a universe of size *n*. The stream defines a frequency vector *a*, and the goal is to compute  $|\{i : a_i \neq 0\}|$ , the number of items with non-zero frequency.

### 2.1.3 Additional Notation

Throughout, [n] will denote the set  $\{1, \ldots, n\}$ , while [[n]] will denote the set  $\{0, \ldots, n-1\}$ .

Let  $\mathbb{F}$  be a field, and  $\mathbb{F}^* = \mathbb{F} \setminus \{0\}$  its multiplicative group. For any *d*-variate polynomial  $p(x_1, \ldots, x_d)$ :  $\mathbb{F}^d \to \mathbb{F}$ , we use deg<sub>i</sub>(p) to denote the degree of p in variable i. A *d*-variate polynomial p is said to be *multilinear* if deg<sub>i</sub>(p)  $\leq 1$  for all  $i \in [d]$ . Given a function  $V : \{0,1\}^d \to \{0,1\}$  whose domain is the *d*dimensional Boolean hypercube, the *multilinear extension* (MLE) of V over  $\mathbb{F}$ , denoted  $\tilde{V}$ , is the unique multilinear polynomial  $\mathbb{F}^d \to \mathbb{F}$  that agrees with V on all Boolean-valued inputs. That is,  $\tilde{V}$  is the unique multilinear polynomial over  $\mathbb{F}$  satisfying  $\tilde{V}(x) = V(x)$  for all  $x \in \{0,1\}^d$ .

## **3** Overview of the Ideas

We begin by describing the methodology underlying the GKR protocol before summarizing the ideas underlying our improved protocols.

### 3.1 The GKR Protocol From 10,000 Feet

In the GKR protocol,  $\mathcal{P}$  and  $\mathcal{V}$  first agree on an arithmetic circuit *C* of fan-in 2 over a finite field  $\mathbb{F}$  computing the function of interest (*C* may have multiple outputs). Each gate of *C* performs an addition or multiplication over  $\mathbb{F}$ . *C* is assumed to be in layered form, meaning that the circuit can be decomposed into layers, and wires only connect gates in adjacent layers. Suppose the circuit has depth *d*; we will number the layers from 1 to *d* with layer *d* referring to the input layer, and layer 1 referring to the output layer.

In the first message,  $\mathcal{P}$  tells  $\mathcal{V}$  the (claimed) output of the circuit. The protocol then works its way in iterations towards the input layer, with one iteration devoted to each layer. The purpose of iteration *i* is to reduce a claim about the values of the gates at layer *i* to a claim about the values of the gates at layer *i* + 1, in the sense that it is safe for  $\mathcal{V}$  to assume that the first claim is true as long as the second claim is true. This reduction is accomplished by applying the standard *sum-check protocol* [29] to a certain polynomial.

More concretely, the GKR protocol starts with a claim about the values of the output gates of the circuit, but  $\mathcal{V}$  cannot check this claim without evaluating the circuit herself, which is precisely what she wants to avoid. So the first iteration uses a sum-check protocol to reduce this claim about the outputs of the circuit to a claim about the gate values at layer 2 (more specifically, to a claim about an evaluation of the multilinear extension (MLE) of the gate values at layer 2). Once again,  $\mathcal{V}$  cannot check this claim herself, so the second iteration uses another sum-check protocol to reduce the latter claim to a claim about the gate values at layer 3, and so on. Eventually,  $\mathcal{V}$  is left with a claim about the inputs to the circuit, and  $\mathcal{V}$  can check this claim on her own.

In summary, the GKR protocol uses a sum-check protocol at each level of the circuit to enable  $\mathcal{V}$  to go from verifying a randomly chosen evaluation of the MLE of the gate values at layer *i* to verifying a (different) evaluation of the MLE of the gate values at layer *i*+1. Importantly, apart from the input layer and output layer,  $\mathcal{V}$  does not ever see all of the gate values at a layer (in particular,  $\mathcal{P}$  does not send these values in full). Instead,  $\mathcal{V}$  relies on  $\mathcal{P}$  to do the hard work of actually evaluating the circuit, and uses the power of the sum-check protocol as the main tool to force  $\mathcal{P}$  to be consistent and truthful over the course of the protocol.

### 3.2 Achieving Optimal Prover Runtime for Regular Circuits

In Theorem 1, we describe an interactive proof protocol for circuit evaluation that brings  $\mathcal{P}$ 's runtime down to O(S(n)) for a large class of circuits, while maintaining the same verifier runtime as in prior implementations of the GKR protocol. Informally, Theorem 1 applies to any circuit whose wiring pattern is sufficiently "regular".

This protocol follows the same general outline as the GKR protocol, in that we proceed in iterations from the output layer of the circuit to the input layer, using a sum-check protocol at iteration *i* to reduce a claim about the gate values at layer *i* to a claim about the gate values at layer i + 1. However, at each iteration *i* we apply the sum-check protocol to a carefully chosen polynomial that differs from the one used by GKR. In each round *j* of the sum-check protocol, our choice of polynomial allows  $\mathcal{P}$  to reuse work from prior rounds in order to compute the prescribed message for round *j*, allowing us to shave a log S(n) factor from the runtime of  $\mathcal{P}$  relative to the  $O(S(n) \log S(n))$ -time implementation due to Cormode et al. [14].

Specifically, at iteration *i*, the GKR protocol uses a polynomial  $f_z^{(i)}$  defined over  $\log S_i + 2\log S_{i+1}$  variables, where  $S_i$  is the number of gates at layer *i*. The "truth table" of  $f_z^{(i)}$  is sparse on the Boolean hypercube, in the sense that  $f_z^{(i)}(x)$  is non-zero for at most  $S_i$  of the  $S_i \cdot S_{i+1}^2$  inputs  $x \in \{0, 1\}^{\log S_i + 2\log S_{i+1}}$ . Cormode et al. leverage this sparsity to bring the runtime of  $\mathcal{P}$  in iteration *i* down to  $O(S_i \log S_i)$  from a naive bound of  $\Omega(S_i \cdot S_{i+1}^2)$ . However, this same sparsity prevents  $\mathcal{P}$  from reusing work from prior iterations as we seek to do.

In contrast, we use a polynomial  $g_z^{(i)}$  defined over only  $\log S_i$  variables rather than  $\log S_i + 2\log S_{i+1}$  variables. Moreover, the truth table of  $g_z^{(i)}$  is dense on the Boolean hypercube, in the sense that  $g_z^{(i)}(x)$  may be non-zero for all of the  $S_i$  Boolean inputs  $x \in \{0,1\}^{\log S_i}$ . This density allows  $\mathcal{P}$  to reuse work from prior iterations in order to speed up her computation in round *i* of the sum-check protocol.

In more detail, in each round *j* of the sum-check protocol, the prover's prescribed message is defined via a sum over a large number of terms, where the number of terms falls geometrically fast with the round number *j*. Moreover, it can be shown that in each round *j*, each gate at layer i + 1 contributes to exactly one term of this sum. Essentially, what we do is group the gates at layer i + 1 by the term of the sum to which they contribute. Each such group can be treated as a single unit, ensuring that in any round of the sum-check protocol, the amount of work  $\mathcal{P}$  needs to do is proportional to the number of terms in the sum rather than the number of gates  $S_i$  at layer *i*.

We remark that a similar "reuse of work" technique was implicit in an analysis by Cormode, Thaler, and Yi [15, Appendix B] of an efficient protocol for a specific streaming problem known as the second frequency moment. This frequency moment protocol was the direct inspiration for our refinements, though we require additional insights to apply the reuse of work technique in the context of evaluating general arithmetic circuits.

It is worth clarifying why our methods do not yield savings when applied to the polynomial  $f_z^{(i)}$  used in the basic GKR protocol. The reason is that, since  $f_z^{(i)}$  is defined over  $\log S_i + 2\log S_{i+1}$  variables instead of just  $\log S_i$  variables, the sum defining  $\mathcal{P}$ 's message in round *j* is over a much larger number of terms when using  $f_z^{(i)}$ . It is still the case that each gate contributes to only one term of the sum, but until the number of terms in the sum falls below  $S_i$  (which does not happen until round  $j = \log S_i + \log S_{i+1}$  of the sum-check protocol), it is possible for each gate to contribute to a different term. Before this point, grouping gates by the term of the sum to which they contribute is not useful, since each group can have size 1.

### 3.3 Verifying General Data Parallel Computations

Theorem 1 only applies to circuits with regular wiring patterns, as do other existing implementations of interactive proof protocols for circuit evaluation [14, 40]. For circuits with irregular wiring patterns, these implementations require the verifier to perform an expensive preprocessing phase (requiring time proportional to the size of the circuit) to pull out information about the wiring of the circuit, and they require a substantial factor blowup (logarithmic in the circuit size) in runtime for the prover relative to evaluating the circuit without a guarantee of correctness.

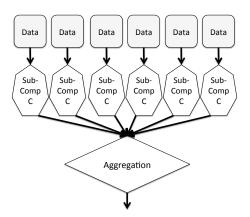

To address these bottlenecks, we do need to make an assumption about the structure of the circuit we are verifying. Ideally our assumption will be satisfied by many real-world computations. To this end, Theorem 2 will describe a protocol that is highly efficient for any data parallel computation, by which we mean any setting in which one applies the same computation independently to many pieces of data. See Figure 2 in Section 7 for a schematic of a data parallel computation.

The idea behind Theorem 2 is as follows. Let *C* be a circuit of size *S* with an arbitrary wiring pattern, and let  $C^*$  be a "super-circuit" that applies *C* independently to *B* different inputs before possibly aggregating the results in some fashion. If one naively applied the basic GKR protocol to the super-circuit  $C^*$ ,  $\mathcal{V}$  might have to perform a pre-processing phase that requires time proportional to the size of  $C^*$ , which is  $\Omega(B \cdot S)$ . Moreover, when applying the basic GKR protocol to  $C^*$ ,  $\mathcal{P}$  would require time  $\Theta(B \cdot S \cdot \log(B \cdot S))$ .

In order to improve on this, the key observation is that although each sub-computation C can have a very complicated wiring pattern, the circuit is "maximally regular" between sub-computations, as the sub-computations do not interact at all. Therefore, each time the basic GKR protocol would apply the sum-check protocol to a polynomial derived from the wiring predicate of  $C^*$ , we instead use a simpler polynomial derived only from the wiring predicate of C. This immediately brings the time required by  $\mathcal{V}$  in the pre-processing phase down to O(S), which is proportional to the cost of executing a single instance of the sub-computation. By using the reuse of work technique underlying Theorem 1, we are also able to bring  $\mathcal{P}$ 's runtime down from  $\Theta(B \cdot S \cdot \log(B \cdot S))$  to  $\Theta(B \cdot S \cdot \log S)$ , i.e.,  $\mathcal{P}$ 's requires a factor of  $O(\log S)$  more time to evaluate the circuit with a guarantee of correctness, compared to evaluating the circuit without such a guarantee. This  $O(\log S)$  factor overhead does not depend on the batch size B.

Our improvements are most significant when  $B \gg S$ , i.e., when a (relatively) small but potentially complicated sub-computation is applied to a very large number of pieces of data. For example, given any very large database, one may ask "How many people in the database satisfy Property P?" Our protocol allows one to verifiably outsource such *counting* queries with overhead that depends minimally on the size of the database, but that necessarily depends on the complexity of the property P.

### 3.4 A Special-Purpose Protocol for MATMULT

We describe a special-purpose protocol for  $n \times n$  MATMULT in Theorem 3. The idea behind this protocol is as follows. The GKR protocol, as well the protocols of Theorems 1 and 2, only make use of the multilinear extension  $\tilde{V}_i$  of the function  $V_i$  mapping gate labels at layer *i* of the circuit to their values. In some cases, there is something to be gained by using a higher-degree extension of  $V_i$ , and this is precisely what we exploit here.

In more detail, our special-purpose protocol can be viewed as an extension of our circuit-checking techniques applied to a circuit *C* performing naive matrix multiplication, but using a quadratic extension of the gate values in this circuit. This allows us to verify the computation using a single invocation of the sum-check protocol. More importantly,  $\mathcal{P}$  can evaluate this higher-degree extension at the necessary points without explicitly materializing all of the gate values of *C*, which would not be possible if we had used the

multilinear extension of the gate values of C.

In the protocol of Theorem 3,  $\mathcal{P}$  just needs to compute the correct output (possibly using an algorithm that is much more sophisticated than naive matrix multiplication), and then perform  $O(n^2)$  additional work to prove the output is correct. Since  $\mathcal{P}$  does not have to evaluate *C* in full, this protocol is perhaps best viewed outside the lens of circuit evaluation. Still, the idea underlying Theorem 3 can be thought of as a refinement of our circuit evaluation protocols, and we believe that similar ideas may yield further improvements to general-purpose protocols in the future.

### 4 Technical Background

### 4.1 Schwartz-Zippel Lemma

We will often make use of the following basic property of polynomials.

**Lemma 1** ([32]) Let  $\mathbb{F}$  be any field, and let  $f : \mathbb{F}^m \to \mathbb{F}$  be a nonzero polynomial of total degree d. Then on any finite set  $S \subseteq \mathbb{F}$ ,

$$\Pr_{x \leftarrow S^m}[f(x) = 0] \le d/|S|.$$

In words, if x is chosen uniformly at random from  $S^m$ , then the probability that f(x) = 0 is at most d/|S|. In particular, any two distinct polynomials of total degree d can agree on at most d/|S| fraction of points in  $S^m$ .

### 4.2 Sum-Check Protocol

Our main technical tool is the sum-check protocol [29], and we present a full description of this protocol for completeness. See also [1, Chapter 8] for a complete exposition and proof of soundness.

Suppose we are given a *v*-variate polynomial g defined over a finite field  $\mathbb{F}$ . The purpose of the sum-check protocol is to compute the sum:

$$H := \sum_{b_1 \in \{0,1\}} \sum_{b_2 \in \{0,1\}} \cdots \sum_{b_\nu \in \{0,1\}} g(b_1, \dots, b_\nu).$$

In order to execute the protocol, the verifier needs to be able to evaluate  $g(r_1, ..., r_v)$  for a randomly chosen vector  $(r_1, ..., r_v) \in \mathbb{F}^v$  – see the paragraph preceding Proposition 1 below.

The protocol proceeds in *v* rounds as follows. In the first round, the prover sends a polynomial  $g_1(X_1)$ , and claims that  $g_1(X_1) = \sum_{x_2,...,x_v \in \{0,1\}^{v-1}} g(X_1, x_2, ..., x_v)$ . Observe that if  $g_1$  is as claimed, then  $H = g_1(0) + g_1(1)$ . Also observe that the polynomial  $g_1(X_1)$  has degree  $\deg_1(g)$ , the degree of variable  $x_1$  in *g*. Hence  $g_1$  can be specified with  $\deg_1(g) + 1$  field elements. In our implementation,  $\mathcal{P}$  will specify *g* by sending the evaluation of *g* at each point in the set  $\{0, 1, ..., \deg_1(g)\}$ .

Then, in round j > 1,  $\mathcal{V}$  chooses a value  $r_{j-1}$  uniformly at random from  $\mathbb{F}$  and sends  $r_{j-1}$  to  $\mathcal{P}$ . We will often refer to this step by saying that variable j-1 gets *bound* to value  $r_{j-1}$ . In return, the prover sends a polynomial  $g_j(X_j)$ , and claims that

$$g_j(X_j) = \sum_{(x_{j+1},\dots,x_{\nu})\in\{0,1\}^{\nu-j}} g(r_1,\dots,r_{j-1},X_j,x_{j+1},\dots,x_{\nu}).$$

(1)

The verifier compares the two most recent polynomials by checking that  $g_{j-1}(r_{j-1}) = g_j(0) + g_j(1)$ , and rejecting otherwise. The verifier also rejects if the degree of  $g_j$  is too high: each  $g_j$  should have degree deg<sub>i</sub>(g), the degree of variable  $x_j$  in g.

In the final round, the prover has sent  $g_{\nu}(X_{\nu})$  which is claimed to be  $g(r_1, \ldots, r_{\nu-1}, X_{\nu})$ .  $\mathcal{V}$  now checks that  $g_{\nu}(r_{\nu}) = g(r_1, \ldots, r_{\nu})$  (recall that we assumed  $\mathcal{V}$  can evaluate g at this point). If this test succeeds, and so do all previous tests, then the verifier accepts, and is convinced that  $H = g_1(0) + g_1(1)$ .

**Proposition 1** Let g be a v-variate polynomial defined over a finite field  $\mathbb{F}$ , and let  $(\mathcal{P}, \mathcal{V})$  be the proververifier pair in the above description of the sum-check protocol.  $(\mathcal{P}, \mathcal{V})$  is a valid interactive proof protocol for the function  $H = \sum_{b_1 \in \{0,1\}} \sum_{b_2 \in \{0,1\}} \cdots \sum_{b_v \in \{0,1\}} g(b_1, \dots, b_v)$ .

### 4.2.1 Discussion of costs.

Observe that there is one round in the sum-check protocol for each of the *v* variables of *g*. The total communication is  $\sum_{i=1}^{v} \deg_i(g) + 1 = v + \sum_{i=1}^{v} \deg_i(g)$  field elements. In all of our applications,  $\deg_i(g) = O(1)$  for all *i*, and so the communication cost is O(v) field elements.

The running time of the verifier over the entire execution of the protocol is proportional to the total communication, plus the amount of time required to compute  $g(r_1, \ldots, r_v)$ .

Determining the running time of the prover is less straightforward. Recall that  $\mathcal{P}$  can specify  $g_j$  by sending for each  $i \in \{0, \dots, \deg_i(g)\}$  the value:

$$g_j(i) = \sum_{(x_{j+1},\dots,x_{\nu})\in\{0,1\}^{\nu-j}} g(r_1,\dots,r_{j-1},i,x_{j+1},\dots,x_{\nu}).$$

<sup>(2)</sup>

An important insight is that the number of terms defining the value  $g_j(i)$  in Equation (2) falls geometrically with *j*: in the *j*th sum, there are only  $2^{\nu-j}$  terms, each corresponding to a Boolean vector in  $\{0,1\}^{\nu-j}$ . The total number of terms that must be evaluated over the course of the protocol is therefore  $O\left(\sum_{j=1}^{\nu} 2^{\nu-j}\right) = O(2^{\nu})$ . Consequently, if  $\mathcal{P}$  is given oracle access to the truth table of the polynomial *g*, then  $\mathcal{P}$  will require just  $O(2^{\nu})$  time.

Unfortunately, in our applications  $\mathcal{P}$  will not have oracle access to the truth table of g. The key to our results is to show that in our applications  $\mathcal{P}$  can nonetheless evaluate g at all of the necessary points in  $O(2^{\nu})$  total time.

### 4.3 The GKR Protocol

We describe the details of the GKR protocol for completeness, as well as to simplify the exposition of our refinements.

### 4.3.1 Notation

Suppose we are given a layered arithmetic circuit *C* of size S(n), depth d(n), and fan-in two. Let  $S_i$  denote the number of gates at layer *i* of the circuit *C*. Assume  $S_i$  is a power of 2 and let  $S_i = 2^{s_i}$ . In order to explain how each iteration of the GKR protocol proceeds, we need to introduce several functions, each of which encodes certain information about the circuit.

To this end, number the gates at layer *i* from 0 to  $S_i - 1$ , and let  $V_i : \{0, 1\}^{s_i} \to \mathbb{F}$  denote the function that takes as input a binary gate label, and outputs the corresponding gate's value at layer *i*. The GKR protocol makes use of the multilinear extension  $\tilde{V}_i$  of the function  $V_i$  (see Section 2.1.3).

The GKR protocol also makes use of the notion of a "wiring predicate" that encodes which pairs of wires from layer i + 1 are connected to a given gate at layer i in C. We define two functions,  $add_i$  and  $mult_i$

mapping  $\{0,1\}^{s_i+2s_{i+1}}$  to  $\{0,1\}$ , which together constitute the wiring predicate of layer *i* of *C*. Specifically, these functions take as input three gate labels  $(j_1, j_2, j_3)$ , and return 1 if gate  $j_1$  at layer *i* is the addition (respectively, multiplication) of gates  $j_2$  and  $j_3$  at layer i+1, and return 0 otherwise. Let  $add_i$  and  $mult_i$  denote the multilinear extensions of  $add_i$  and  $mult_i$  respectively.

Finally, let  $\beta_{s_i}(z, p)$  denote the function

$$\beta_{s_i}(z,p) = \prod_{j=1}^{s_i} \left( (1-z_j)(1-p_j) + z_j p_j \right)$$

It is straightforward to check that  $\beta_{s_i}$  is the multilinear extension of the function  $B(x, y) : \{0, 1\}^{s_i} \times \{0, 1\}^{s_i} \rightarrow \{0, 1\}$  that evaluates to 1 if x = y, and evaluates to 0 otherwise.

#### 4.3.2 Protocol Outline

The GKR protocol consists of d(n) iterations, one for each layer of the circuit. Each iteration starts with  $\mathcal{P}$  claiming a value for  $\tilde{V}_i(z)$  for some field element  $z \in \mathbb{F}^{s_i}$ . In the first iteration and circuits with a single output gate, z = 0 and  $\tilde{V}_1(0)$  corresponds to the output value of the circuit.

For circuits with many output gates, Vu et al. [40] observe that in the first iteration,  $\mathcal{P}$  may simply send  $\mathcal{V}$  the (claimed) values of all output gates, thereby specifying a function  $V'_1 : \{0,1\}^{s_1} \to \mathbb{F}$  claimed to equal  $V_1$ .  $\mathcal{V}$  can pick a random point  $z \in \mathbb{F}^{s_1}$  and evaluate  $\tilde{V}'_1(z)$  on her own in  $O(S_1)$  time (see Remark 1 in Section 4.3.5). The Schwartz-Zippel Lemma (Lemma 1) implies that it is safe for  $\mathcal{V}$  to believe that  $V'_1$  indeed equals  $V_1$  as claimed, as long as  $\tilde{V}_1(z) = \tilde{V}'_1(z)$  (which will be checked in the remainder of the protocol).

The purpose of iteration *i* is to reduce the claim about the value of  $\tilde{V}_i(z)$  to a claim about  $\tilde{V}_{i+1}(\omega)$  for some  $\omega \in \mathbb{F}^{s_{i+1}}$ , in the sense that it is safe for  $\mathcal{V}$  to assume that the first claim is true as long as the second claim is true. To accomplish this, the iteration applies the sum-check protocol described in Section 4.2 to a specific polynomial derived from  $\tilde{V}_{i+1}$ , add<sub>i</sub>, and mult<sub>i</sub>, and  $\beta_{s_i}$ .

### 4.3.3 Details for Each Iteration

**Applying the Sum-Check Protocol.** It can be shown that for any  $z \in \mathbb{F}^{s_i}$ ,

$$\tilde{V}_i(z) = \sum_{(p, \omega_1, \omega_2) \in \{0, 1\}^{s_i + 2s_{i+1}}} f_z^{(i)}(p, \omega_1, \omega_2),$$

where

$$f_{z}^{(i)}(p,\boldsymbol{\omega}_{1},\boldsymbol{\omega}_{2}) = \boldsymbol{\beta}_{s_{i}}(z,p) \cdot \left( \tilde{\operatorname{add}}_{i}(p,\boldsymbol{\omega}_{1},\boldsymbol{\omega}_{2})(\tilde{V}_{i+1}(\boldsymbol{\omega}_{1}) + \tilde{V}_{i+1}(\boldsymbol{\omega}_{2})) + \tilde{\operatorname{mult}}_{i}(p,\boldsymbol{\omega}_{1},\boldsymbol{\omega}_{2})\tilde{V}_{i+1}(\boldsymbol{\omega}_{1}) \cdot \tilde{V}_{i+1}(\boldsymbol{\omega}_{2}) \right).$$

(3)

Iteration *i* therefore applies the sum-check protocol of Section 4.2 to the polynomial  $f_z^{(i)}$ . There remains the issue that  $\mathcal{V}$  can only execute her part of the sum-check protocol if she can evaluate the polynomial  $f_z^{(i)}$  at a random point  $f_z^{(i)}(r_1, \ldots, r_{s_i+2s_{i+1}})$ . This is handled as follows.

Let  $p^*$  denote the first  $s_i$  entries of the vector  $(r_1, \ldots, r_{s_i+2s_{i+1}})$ ,  $\omega_1^*$  the next  $s_{i+1}$  entries, and  $\omega_2^*$  the last  $s_{i+1}$  entries. Evaluating  $f_z^{(i)}(p^*, \omega_1^*, \omega_2^*)$  requires evaluating  $\beta(z, p^*)$ ,  $\tilde{\mathrm{add}}_i(p^*, \omega_1^*, \omega_2^*)$ ,  $\tilde{\mathrm{mult}}_i(p^*, \omega_1^*, \omega_2^*)$ ,  $\tilde{V}_{i+1}(\omega_1^*)$ , and  $\tilde{V}_{i+1}(\omega_2^*)$ .

$\mathcal{V}$  can easily evaluate  $\beta(z, p^*)$  in  $O(s_i)$  time. For many circuits, particularly those with "regular" wiring patterns,  $\mathcal{V}$  can evaluate  $add_i(p^*, \omega_1^*, \omega_2^*)$  and  $\tilde{mult}_i(p^*, \omega_1^*, \omega_2^*)$  on her own in  $poly(s_i, s_{i+1})$  time as well.<sup>2</sup>

$\mathcal{V}$  cannot however evaluate  $\tilde{V}_{i+1}(\omega_2^*)$ , and  $\tilde{V}_{i+1}(\omega_1^*)$  on her own without evaluating the circuit. Instead,  $\mathcal{V}$  asks  $\mathcal{P}$  to simply tell her these two values, and uses iteration i + 1 to *verify* that these values are as claimed. However, one complication remains: the precondition for iteration i + 1 is that  $\mathcal{P}$  claims a value for  $\tilde{V}_i(z)$  for a single  $z \in \mathbb{F}^{s_i}$ . So  $\mathcal{V}$  needs to reduce verifying both  $\tilde{V}_{i+1}(\omega_2^*)$  and  $\tilde{V}_{i+1}(\omega_1^*)$  to verifying  $\tilde{V}_{i+1}(\omega^*)$  at a single point  $\omega^* \in \mathbb{F}^{s_{i+1}}$ , in the sense that it is safe for  $\mathcal{V}$  to accept the claimed values of  $\tilde{V}_{i+1}(\omega_1^*)$  and  $\tilde{V}_{i+1}(\omega_2^*)$  as long as the value of  $\tilde{V}_{i+1}(\omega^*)$  is as claimed. This is done as follows.

**Reducing to Verification of a Single Point.** Let  $\ell : \mathbb{F} \to \mathbb{F}^{s_{i+1}}$  be some canonical line passing through  $\omega_1^*$  and  $\omega_2^*$ . For example, we can let  $\ell$  be the unique line such that  $\ell(0) = \omega_1^*$  and  $\ell(1) = \omega_2^*$ .  $\mathcal{P}$  sends a degree- $s_{i+1}$  polynomial h claimed to be  $\tilde{V}_{i+1} \circ \ell$ , the restriction of  $\tilde{V}_{i+1}$  to the line  $\ell$ .  $\mathcal{V}$  checks that  $h(0) = \omega_1^*$  and  $h(1) = \omega_2^*$  (rejecting if this is not the case), picks a random point  $r^* \in \mathbb{F}$ , and asks  $\mathcal{P}$  to prove that  $\tilde{V}_{i+1}(\ell(r^*)) = h(r^*)$ . By the Schwartz-Zippel Lemma (Lemma 1), as long as  $\mathcal{V}$  is convinced that  $\tilde{V}_{i+1}(\ell(r^*)) = h(r^*)$ , it is safe for  $\mathcal{V}$  to believe that the values of  $\tilde{V}_{i+1}(\omega_1^*)$  and  $\tilde{V}_{i+1}(\omega_2^*)$  are as claimed by  $\mathcal{P}$ . This completes iteration i;  $\mathcal{P}$  and  $\mathcal{V}$  then move on to the iteration for layer i + 1 of the circuit, whose purpose is to verify that  $\tilde{V}_{i+1}(\ell(r^*))$  has the claimed value.

**The Final Iteration.** Finally, at the final iteration d,  $\mathcal{V}$  must evaluate  $\tilde{V}_d(\omega^*)$  on her own. But the vector of gate values at layer d of C is simply the input x to C. It can be shown that  $\mathcal{V}$  can compute  $\tilde{V}_d(\omega^*)$  on her own in  $O(n \log n)$  time, with a single streaming pass over the input [15]. Moreover, Vu et al. show how to bring  $\mathcal{V}$ 's time cost down to O(n) [40], but this methodology does not work in a general streaming model. For completeness, we present details of both of these observations in Section 4.3.5.

### 4.3.4 Discussion of Costs.

Observe that the polynomial  $f_z^{(i)}$  defined in Equation (3) is an  $(s_i + 2s_{i+1})$ -variate polynomial of degree at most 2 in each variable, and so the invocation of the sum-check protocol at iteration *i* requires  $s_i + 2s_{i+1}$  rounds, with three field elements transmitted per round. Thus, the total communication cost is  $O(d(n)\log S(n))$  field elements, where d(n) is the depth of the circuit *C*. The time cost to  $\mathcal{V}$  is  $O(n\log n + d(n)\log S(n))$ , where the  $n\log n$  term is due to the time required to evaluate  $\tilde{V}_d(\omega^*)$  (see Lemma 2 below), and the  $d(n)\log S(n)$  term is the time required for  $\mathcal{V}$  to send messages to  $\mathcal{P}$  and process and check the messages from  $\mathcal{P}$ .

As for  $\mathcal{P}$ 's runtime, for any iteration *i* of the GKR protocol, a naive implementation of the prover in the corresponding instance of the sum-check protocol would require time  $\Omega(2^{s_i+2s_{i+1}})$ , as the sum defining each of  $\mathcal{P}$ 's messages is over as many as  $2^{s_i+2s_{i+1}}$  terms. This cost can be  $\Omega(S(n)^3)$ , which is prohibitively large in practice. However, Cormode, Mitzenmacher, and Thaler showed in [14] that each gate at layers *i* and i+1 of *C* contributes to only a *single* term of sum, and exploit this to bring the runtime of the  $\mathcal{P}$  down to  $O(S(n)\log S(n))$ .

<sup>&</sup>lt;sup>2</sup>Various suggestions have been put forth for what to do if this is not the case. For example, these computations can always be done by  $\mathcal{V}$  in  $O(\log S(n))$  space as long as the circuit is log-space uniform, which is sufficient in streaming applications where the space usage of the verifier is paramount [14]. Moreover, these computations can be done offline before the input is even observed, because they only depend on the wiring of the circuit, and not on the input [14, 21]. Finally, [40] notes that the cost of this computation can be effectively amortized in a batching model, where many identical computations on different inputs are verified simultaneously. See Section 7 for further discussion, and a protocol that mitigates this issue in the context of data parallel computation.

#### **4.3.5** Making $\mathcal{V}$ Fast vs. Making $\mathcal{V}$ Streaming

We describe how  $\mathcal{V}$  can efficiently evaluate  $\tilde{V}_d(\omega^*)$  on her own, as required in the final iteration of the GKR protocol. Prior work has identified two methods for performing this computation. The first method is due to Cormode, Thaler, and Yi [15]. It requires  $O(n \log n)$  time, and allows  $\mathcal{V}$  to make a single streaming pass over the input using  $O(\log n)$  space.

**Lemma 2** ([15]) Given an input  $x \in \mathbb{F}^n$  and a vector  $\omega^* \in \mathbb{F}^{\log n}$ ,  $\mathcal{V}$  can compute  $\tilde{V}_d(\omega^*)$  in  $O(n \log n)$  time and  $O(\log n)$  space with a single streaming pass over the input, where  $\tilde{V}_d$  is the multilinear extension of the function that maps  $i \in \{0,1\}^{\log n}$  to the value of the ith entry of x.

**Proof:** We exploit the following explicit expression for  $\tilde{V}_d$ . For a vector  $b \in \{0,1\}^{\log n}$  let  $\chi_b(x_1, \ldots, x_{\log n}) = \prod_{k=1}^{\log n} \chi_{b_k}(x_k)$ , where  $\chi_0(x_k) = 1 - x_k$  and  $\chi_1(x_k) = x_k$ . Notice that  $\chi_b$  is the unique multilinear polynomial that takes  $b \in \{0,1\}^{\log n}$  to 1 and all other values in  $\{0,1\}^{\log n}$  to 0, i.e., it is the multilinear extension of the indicator function for boolean vector *b*. With this definition in hand, we may write:

$$\tilde{V}_d(p_1, \dots, p_{\log n}) = \sum_{b \in \{0,1\}^{\log n}} V_d(b) \chi_b(p_1, \dots, p_{\log n})$$

(4)

Indeed, it is easy to check that the right hand side of Equation (4) is a multilinear polynomial, and that it agrees with  $V_d$  on all Boolean inputs. Hence, the right hand side must equal the multilinear extension of  $V_d$ .

In particular, by letting  $(p_1, \ldots, p_{\log n}) = \omega^*$  in Equation (4), we see that

$$\tilde{V}_d(\boldsymbol{\omega}^*) = \sum_{b \in \{0,1\}^{\log n}} V_d(b) \chi_b(\boldsymbol{\omega}^*).$$

(5)

Given any stream update  $(i, \delta)$ , let  $(i_1, \ldots, i_{\log n})$  denote the binary representation of *i*. Notice that update  $(i, \delta)$  has the effect of increasing  $V_d(i_1, \ldots, i_{\log n})$  by  $\delta$ , and does not affect  $V_d(x_1, \ldots, x_{\log n})$  for any  $(x_1, \ldots, x_{\log n}) \neq (i_1, \ldots, i_{\log n})$ . Thus,  $\mathcal{V}$  can compute  $\tilde{V}_d(\omega^*)$  incrementally from the raw stream by initializing  $\tilde{V}_d(\omega^*) \leftarrow 0$ , and processing each update  $(i, \delta)$  via:

$$\tilde{V}_d(\boldsymbol{\omega}^*) \leftarrow \tilde{V}_d(\boldsymbol{\omega}^*) + \boldsymbol{\delta} \cdot \boldsymbol{\chi}_i(\boldsymbol{\omega}^*).$$

$\mathcal{V}$  only needs to store  $\tilde{V}_d(\omega^*)$  and  $\omega^*$ , which requires  $O(\log n)$  words of memory. Moreover, for any *i*,  $\chi_{(i_1,...,i_{\log n})}(\omega^*)$  can be computed in  $O(\log n)$  field operations, and thus  $\mathcal{V}$  can compute  $\tilde{V}_d(\omega^*)$  with one pass over the raw stream, using  $O(\log n)$  words of space and  $O(\log n)$  field operations per update.

The second method is due to Vu et al. [40]. It enables  $\mathcal{V}$  to compute  $\tilde{V}_d(\omega^*)$  in O(n) time, but requires  $\mathcal{V}$  to use O(n) space.

### **Lemma 3 (Vu et al. [40])** $\mathcal{V}$ can compute $\tilde{V}_d(\boldsymbol{\omega}^*)$ in O(n) time and O(n) space.

**Proof:** We again exploit the expression for  $\tilde{V}_d(\omega^*)$  in Equation (5). Notice the right hand side of Equation (5) expresses  $\tilde{V}_d(\omega^*)$  as the inner product of two *n*-dimensional vectors, where the *b*th entry of the first vector is  $V_d(b)$  and the *b*th entry of the second vector is  $\chi_b(\omega^*)$ . This inner product can be computed in O(n) time given a table of size *n* whose *b*th entry contains the quantity  $\chi_b(\omega^*)$ . Vu et al. show how to build such a table in time O(n) using memoization.

The memoization procedure consists of  $\log n$  stages, where Stage *j* constructs a table  $A^{(j)}$  of size  $2^j$ , such that for any  $(b_1, \ldots, b_j) \in \{0, 1\}^j$ ,  $A^{(j)}[(b_1, \ldots, b_j)] = \prod_{i=1}^j \chi_{b_i}(\omega_i^*)$ . Notice  $A^{(j)}[(b_1, \ldots, b_j)] = A^{(j-1)}[(b_1, \ldots, b_{j-1})] \cdot \chi_{b_j}(\omega_j^*)$ , and so the *j*th stage of the memoization procedure requires time  $O(2^j)$ . The total time across all log *n* stages is therefore  $O(\sum_{j=1}^{\log n} 2^j) = O(2^{\log n}) = O(n)$ . This completes the proof.

**Remark 1** In [41], Vu et al. further observe that if the input is presented in a specific order, then  $\mathcal{V}$  can evaluate  $\tilde{V}_d(\omega^*)$  using  $O(\log n)$  space. Compare this result to Lemma 2, which requires  $O(n\log n)$  time for  $\mathcal{V}$ , but allows  $\mathcal{V}$  to use  $O(\log n)$  space regardless of the order in which the input is presented.

### **5** Time-Optimal Protocols for Circuit Evaluation

### 5.1 Protocol Outline and Section Roadmap

As with the GKR protocol, our protocol consists of d(n) iterations, one for each layer of the circuit. Each iteration starts with  $\mathcal{P}$  claiming a value for  $\tilde{V}_i(z)$  for some value  $z \in \mathbb{F}^{s_i}$ . The purpose of the iteration is to reduce this claim to a claim about  $\tilde{V}_{i+1}(\omega)$  for some  $\omega \in \mathbb{F}^{s_{i+1}}$ , in the sense that it is safe for  $\mathcal{V}$  to assume that the first claim is true as long as the second claim is true. As in the GKR protocol, this is done by invoking the sum-check protocol on a certain polynomial.

In order to improve on the costs of the GKR protocol implementation of Cormode et al. [14], we replace the polynomial  $f_z^{(i)}$  in Equation (3) with a different polynomial  $g_z^{(i)}$  defined over a much smaller domain. Specifically,  $g_z^{(i)}$  is defined over only  $s_i$  variables rather than  $s_i + 2s_{i+1}$  variables as is the case of  $f_z^{(i)}$ . Using  $g_z^{(i)}$  in place of  $f_z^{(i)}$  allows  $\mathcal{P}$  to reuse work across iterations of the sum-check protocol, thereby reducing  $\mathcal{P}$ 's runtime by a logarithmic factor relative to [14], as formalized in Theorem 1 below.

The remainder of the presentation leading up to Theorem 1 proceeds as follows. After stating a preliminary lemma, we describe the polynomial  $g_z^{(i)}$  that we use in the context of three specific circuits: a binary tree of addition or multiplication gates, and a circuit computing the number of non-zero entries of an *n*-dimensional vector *a*. The purpose of this exposition is to showcase the ideas underling Theorem 1 in concrete scenarios. Second, we explain the algorithmic insights that allow  $\mathcal{P}$  to reuse work across iterations of the sum-check protocol applied to  $g_z^{(i)}$ . Finally, we state and prove Theorem 1, which formalizes the class of circuits to which our methods apply.

### 5.2 A Preliminary Lemma

We will repeatedly invoke the following lemma, which allows us to express the value  $\tilde{V}_i(z)$  in a manner amenable to verification via the sum-check protocol. This is essentially a restatement of [31, Lemma 3.2.1].

**Lemma 4** Let W be any polynomial  $\mathbb{F}^{s_i} \to \mathbb{F}$  that extends  $V_i$ , in the sense that for all  $p \in \{0,1\}^{s_i}$ ,  $W(p) = V_i(p)$ . Then for any  $z \in \mathbb{F}^{s_i}$ ,

$$\tilde{V}_i(z) = \sum_{p \in \{0,1\}^{s_i}} \beta_{s_i}(z, p) W(p).$$

(6)

**Proof:** It is easy to check that the right hand side of Equation (6) is a multilinear polynomial in z, and that it agrees with  $V_i$  on all Boolean inputs. Thus, the right hand side of Equation (6), viewed as a polynomial in z, must be the multilinear extension  $\tilde{V}_i$  of  $V_i$ . This completes the proof.

### 5.3 Polynomials for Specific Circuits

### 5.3.1 The Polynomial for a Binary Tree

Consider a circuit *C* that computes the product of all *n* of its inputs by multiplying them together via a binary tree. Label the gates at layers *i* and *i*+1 in the natural way, so that the first input to the gate labelled  $p = (p_1, \ldots, p_{s_i}) \in \{0, 1\}^{s_i}$  at layer *i* is the gate with label (p, 0) at layer *i*-1, and the second input to gate *p* has label (p, 1). Here and throughout, (p, 0) denotes the  $s_i + 1$ -dimensional vector obtained by concatenating the entry 0 to the end of the vector *p*. Interpreting  $p = (p_1, \ldots, p_{s_i}) \in \{0, 1\}^{s_i}$  as an integer between 0 and  $2^{s_i} - 1$  with  $p_1$  as the high-order bit and  $p_{s_i}$  as the low-order bit, this says that the first inneighbor of *p* is 2*p* and the second is 2p + 1. It follows immediately that for any gate  $p \in \{0, 1\}^{s_i}$  at layer *i*,  $V_i(p) = \tilde{V}_{i+1}(p, 0) \cdot \tilde{V}_{i+1}(p, 1)$ . Invoking Lemma 4, we obtain the following proposition.

**Proposition 2** Let *C* be a circuit consisting of a binary tree of multiplication gates. Then  $\tilde{V}_i(z) = \sum_{p \in \{0,1\}^{s_i}} g_z^{(i)}(p)$ , where  $g_z^{(i)}(p) = \beta_{s_i}(z,p) \cdot \tilde{V}_{i+1}(p,0) \cdot \tilde{V}_{i+1}(p,1)$ .

**Remark 2** Notice that the polynomial  $g_z^{(i)}$  in Proposition 2 is a degree three polynomial in each variable of *p*. When applying the sum-check protocol to  $g_z^{(i)}$ , the prover therefore needs to send 4 field elements per round.

In the case of Proposition 2, the line  $\ell : \mathbb{F} \to \mathbb{F}^{2_{i+1}}$  in the "Reducing to Verification of a Single Point" step has an especially simple expression. Let  $r \in \mathbb{F}^{s_i}$  be the vector of random field elements chosen by  $\mathcal{V}$ over the execution of the sum-check protocol. Notice that  $\ell(0)$  must equal the point  $(r,0) \in \mathbb{F}^{s_i+1}$  i.e., the point whose first  $s_i$  coordinates equal r and whose last coordinate equals 0. Similarly,  $\ell(1)$  must equal (r, 1). We may therefore express the line  $\ell$  via the equation  $\ell(t) = (r, t)$ . In this case,  $\tilde{V}_{i+1} \circ \ell$  has degree 1 and is implicitly specified when  $\mathcal{P}$  sends the claimed values of  $\tilde{V}_i(r, 0)$  and  $\tilde{V}_i(r, 1)$ .

The case of a binary tree of addition gates is similar to the case of multiplication gates.

**Proposition 3** Let *C* be a circuit consisting of a binary tree of addition gates. Then  $\tilde{V}_i(z) = \sum_{p \in \{0,1\}^{s_i}} g_z^{(i)}(p)$ , where  $g_z^{(i)}(p) = \beta_{s_i}(z,p) \left( \tilde{V}_{i+1}(p,0) + \tilde{V}_{i+1}(p,1) \right)$ .

**Remark 3** The polynomial  $g_z^{(i)}$  of Proposition 3 has degree 2 in all variables, rather than degree 3 as in *Proposition 2.*

#### 5.3.2 The Polynomials for DISTINCT

We now describe a circuit *C* for computing the number of non-zero entries of a vector  $a \in \mathbb{F}^n$  (this vector should be interpreted as the *frequency vector* of a data stream). A similar circuit was used in conjunction with the GKR protocol in [14] to yield an efficient protocol with a streaming verifier for DISTINCT, and we borrow heavily from the presentation there. We remark that our refinements enable us to slightly simplify the circuit used in [14] by avoiding the awkward use of a constant-valued input wire with value set to 1. This causes some gates in our circuit to have fan-in 1 rather than fan-in 2, which is easily supported by our protocol.

The circuit *C* is tailored for use over the field of cardinality equal to a Mersenne prime  $q = 2^k - 1$  for some *k*. Fields of cardinality equal to a Mersenne prime can support extremely fast arithmetic, and as discussed later in Section 6.2, there are several Mersenne primes of appropriate magnitude for use within our protocols.

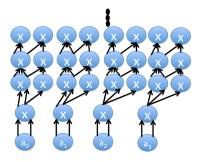

Figure 1: The first several layers of a circuit for  $F_0$  on four inputs over the field  $\mathbb{F}$  with  $q = 2^k - 1$  elements. The first layer from the bottom computes  $a_i^2$  for each input entry  $a_i$ . The second layer from the bottom computes  $a_i^4$  and  $a_i^2$  for all *i*. The third layer computes  $a_i^8$  and  $a_i^6 = a_i^4 \times a_i^2$ , while the fourth layer computes  $a_i^{16}$  and  $a_i^{14} = a_i^8 \times a_i^6$ . The remaining layers (not shown) have structure identical to the third and fourth layers until the value  $a_i^{q-1}$  is computed for all *i*, and the circuit culminates in a binary tree of addition gates.

The circuit *C* exploits Fermat's Little Theorem, computing  $a_i^{q-1}$  for each input entry  $a_i$  before summing the results. As described in [14], verifying the summation sub-circuit can be handled with a one invocation of the sum-check protocol, or less efficiently by running our protocol for a binary tree of addition gates described in Proposition 3.

We now turn to describing the part of the circuit computing  $a_i^{q-1}$  for each input entry  $a_i$ . We may write  $q-1=2^k-2$ , whose binary representation is k-1 1s followed by a 0. Thus,  $a_i^{q-1} = \prod_{j=1}^{k-1} a_i^{2^j}$ . To compute  $a_i^{q-1}$ , the circuit repeatedly squares a, and multiplies together the results "as it goes". In more detail, for j > 2 there are two multiplication gates at each layer d(n) - j of the circuit for computing  $a_i^{q-1}$ ; the first computes  $a^{2^j}$  by squaring the corresponding gate at layer j-1, and the second computes  $\prod_{\ell=1}^{j-1} a_\ell^{2^{\ell-1}}$ . See Figure 1 for a depiction.

For our purposes there are k + 1 relevant circuit layers, all of which consist entirely of multiplication gates. Layers 1 through k - 1 all contain 2n gates. Number the gates from 0 to 2n - 1 in the natural way. In what follows, we will abuse notation and use p to refer to both a gate number as well as its binary representation.

An even-numbered gate p at layer i has both in-wires connected to gate p at layer i + 1, while an odd-numbered gate p has one in-wire connected to gate p and another connected to gate p - 1. Thus, the connectivity information of the circuit is a simple function of the binary representation p of each gate at layer i. If the low-order bit  $p_{s_i}$  of p is 0 (i.e., it is an even-numbered gate), then both in-neighbors at layer i + 1 of gate p have binary representation p. If the low-order bit  $p_{s_i}$  is 1 (i.e., it is an odd-numbered gate), then the first in-neighbor of gate p has binary representation p, and the second has binary representation  $(p_{-s_i}, 0)$ , where  $p_{-s_i}$  denotes p with the coordinate  $p_{s_i}$  removed.

Invoking Lemma 4, the following proposition is easily verified.

**Proposition 4** Let C be the circuit described above. For layers  $i \in \{1, ..., k-1\}$ ,  $\tilde{V}_i(z) = \sum_{p \in \{0,1\}^{s_i}} g_z^{(i)}(p)$  where

$$g_{z}^{(i)}(p) = \beta_{s_{i}}(z,p) \left( (1-p_{s_{i}}) \tilde{V}_{i+1}(p_{-s_{i}},0) \cdot \tilde{V}_{i+1}(p_{-s_{i}},0) + p_{s_{i}} \tilde{V}_{i+1}(p_{-s_{i}},1) \cdot \tilde{V}_{i+1}(p_{-s_{i}},0) \right),$$

where  $p_{-s_i}$  denotes p with the coordinate  $p_{s_i}$  removed.

**Remark 4** To check  $\mathcal{P}$ 's claim in the final round of the sum-check protocol applied to  $g_z^{(i)}$ ,  $\mathcal{V}$  needs to know  $\tilde{V}_{i+1}(r,0)$  and  $\tilde{V}_{i+1}(r,1)$  for some random vector  $r \in \mathbb{F}^{s_i-1}$ . This is identical to the situation in the case of a binary tree of addition or multiplication gates, where the "Reducing to Verification of a Single Point" step had an especially simple implementation.

At layer k, an even-numbered gate p has both in-wires connected to gate p/2 at layer k+1, while an odd-numbered gate p has its unique in-wire connected to gate (p-1)/2 at layer k+1. Thus, for a gate at layer i = k, if the the low-order bit  $p_{s_i}$  of the gate's binary representation p is 1 (i.e., it is an odd-numbered gate), then both in-neighbors at layer i+1 of have binary representation  $p_{-s_i}$ . If the low-order bit  $p_{s_i}$  is 0 (i.e., it is an even numbered gate), then the unique in-neighbor of p at layer i+1 has binary representation  $p_{-s_i}$ .

Invoking Lemma 4, the following is easily verified.

**Proposition 5** Let C be the circuit described above. For layer i = k,  $\tilde{V}_i(z) = \sum_{p \in \{0,1\}^{s_i}} g_z^{(i)}(p)$  where

$$g_{z}^{(i)}(p) = \beta_{s_{i}}(z,p) \left( (1-p_{s_{i}}) \tilde{V}_{i+1}(p_{-s_{i}}) \cdot \tilde{V}_{i+1}(p_{-s_{i}}) + p_{s_{i}} \tilde{V}_{i+1}(p_{-s_{i}}) \right),$$

where  $p_{-s_i}$  denotes p with coordinate  $p_{s_i}$  removed.

Finally, at layer k + 1, each gate p has both in-wires connected to gate p at layer k + 2 (which is the input layer). Thus:

**Proposition 6** Let C be the circuit described above. For layer i = k + 1,  $\tilde{V}_i(z) = \sum_{p \in \{0,1\}^{s_i}} g_z^{(i)}(p)$  where

$$g_z^{(i)}(p) = \beta_{s_i}(z,p)\tilde{V}_{i+1}(p)\cdot\tilde{V}_{i+1}(p).$$

### 5.4 Reusing Work

Recall that our analysis of the costs of the sum-check protocol in Section 4.2.1 revealed that, when applying a sum-check protocol to an  $s_i$ -variate polynomial  $g_z^{(i)}$ ,  $\mathcal{P}$  only needs to evaluate  $g_z^{(i)}$  at  $O(2^{s_i})$  points across all rounds of the protocol. Our goal in this section is to show how  $\mathcal{P}$  can do this in time  $O(2^{s_i} + 2^{s_{i+1}}) = O(S_i + S_{i+1})$  for all of the polynomials  $g_z^{(i)}$  described in Section 5.3. This is sufficient to ensure that  $\mathcal{P}$  takes  $O(\sum_{i=1}^{d(n)} S_i) = O(S(n))$  time across all iterations of our circuit-checking protocol.

To this end, notice that all of the polynomials  $g_z$  described in Propositions 2-6 have the following property: for any  $r \in \mathbb{F}^{s_i}$ , evaluating  $g_z^{(i)}(r)$  can be done in constant time given  $\beta(z, r)$  and the evaluations of  $\tilde{V}_{i+1}$  at a constant number of points. For example, consider the polynomial  $g_z^{(i)}$  described in Proposition 4:  $g_z^{(i)}(r)$  can be computed in constant time given  $\beta_{s_i}(z, r)$ ,  $\tilde{V}_{i+1}(r_{-s_i}, 0)$ , and  $\tilde{V}_{i+1}(r_{-s_i}, 1)$ .