# Formal Definition and Verification for Combined Random Fault and Random Probing Security

Sonia Belaïd<sup>1</sup>, Jakob Feldtkeller<sup>2</sup>, Tim Güneysu<sup>2,3</sup>, Anna Guinet<sup>2</sup>, Jan Richter-Brockmann<sup>2</sup>, Matthieu Rivain<sup>1</sup>, Pascal Sasdrich<sup>2</sup>, and Abdul Rahman Taleb<sup>1</sup>

1 CryptoExperts, Paris, France

{sonia.belaid, matthieu.rivain}@cryptoexperts.com

taleb.abdulrahman1@gmail.com

Ruhr University Bochum, Horst Görtz Institute for IT Security, Bochum, Germany {jakob.feldtkeller, tim.gueneysu, anna.guinet, jan.richter-brockmann, pascal.sasdrich}@rub.de

3 DFKI, Bremen, Germany

Abstract. In our highly digitalized world, an adversary is not constrained to purely digital attacks but can monitor or influence the physical execution environment of a target computing device. Such side-channel or fault-injection analysis poses a significant threat to otherwise secure cryptographic implementations. Hence, it is important to consider additional adversarial capabilities when analyzing the security of cryptographic implementations besides the default black-box model. For side-channel analysis, this is done by providing the adversary with knowledge of some internal values, while for fault-injection analysis the capabilities of the adversaries include manipulation of some internal values.

In this work, we extend probabilistic security models for physical attacks, by introducing a general random probing model and a general random fault model to capture arbitrary leakage and fault distributions, as well as the combination of these models. Our aim is to enable a more accurate modeling of low-level physical effects. We then analyze important properties, such as the impact of adversarial knowledge on faults and compositions, and provide tool-based formal verification methods that allow the security assessment of design components. These methods are introduced as extension of previous tools VERICA and IronMask which are implemented, evaluated and compared.

**Keywords:** Physical Security  $\cdot$  Random Probing Model  $\cdot$  Random Fault Model  $\cdot$  Combined Analysis.

## 1 Introduction

State-of-the-art cryptographic schemes are usually analyzed in the common black-box model, which operates under the assumption that the internal values of the scheme are hidden and protected from the adversary. However, over

the last 25 years, physical attacks, which exploit the physical realization and implementation of cryptographic algorithms, have questioned those assumptions. In particular, Side-Channel Analysis (SCA) exploits dependencies between processed values and physical execution characteristics such as timing behavior [32], instantaneous power consumption [33], or electromagnetic emanations [28], to conclude information about a secret. Similarly, Fault Injection Analysis (FIA) manipulates the physical execution environment to create a faulty intermediate state such that the resulting output gives a hint about the processed secret. Common fault injection methods include clock and voltage glitching [47,21], targeted electromagnetic (EM) pules [18,23], or focused laser beams [46]. Both attack vectors question a different assumption of the cryptographic black-box model: SCA that internal values are confidential and hidden from the adversary and FIA that the internal values have integrity and cannot be manipulated by the adversary. However, in a real attack scenario, the adversary is not restricted to performing only one of the two attack types. Indeed, first practical attack for Combined Analysis (CA), i.e., the combination of FIA and SCA, are emerging [3,15,40,41,42,43].

Constructing effective countermeasures against such physical attacks requires a deep understanding of attack properties and leakage behavior. To this end, the research community endeavors to theoretically model the leakage emanating from the victim device which is susceptible to exploitation by the adversary. In particular for SCA, in the famous d-probing model introduced by Ishai, Sahai, and Wagner [31], the leakage is modeled by the exact values of d internal variables of the adversary's choice. A victim device is then deemed d-probing secure if any such set of d intermediate variables is statistically independent on the processed secret. While this probing model facilitates security proofs, it sometimes fails to closely reflect the reality of embedded devices. For instance, it does not capture horizontal attacks [8], which exploit in particular repeated manipulation of variables within an execution. Consequently, the community is starting to focus on more realistic leakage models, like the  $\epsilon$ -random probing model [31,2,10]. In the latter, the leakage is assumed to gather the exact value carried by each wire of the circuit with probability p. The security is then determined by the probability  $\epsilon$  of the adversary to obtain a secret-dependent probe combination. This model tightly reduces to the security in the practical noisy leakage model [35,22], where each variable leaks a noisy function of its value. Nevertheless, the random probing model is still insufficient in modeling low-level physical effects because it assigns the same independent probability to each intermediate variable whereas the underlying noise is likely to be different and the independence assumption is not verified in practice.

For modeling of FIA the adversary is given the ability to manipulate a set of intermediate variables in a predefined way and then their impact on the system output is analyzed. Models from the literature often take inspiration from probing models for SCA. Specifically, the k-fault model [30] allows the adversary to manipulate up to k intermediate values, while the random fault model [19] defines a fault probability q and manipulates each internal values with proba-

bility q. In both models, the adversary wins when they get a faulty output that cannot be detected or corrected, whereas the random fault model determines the probability  $\mu$  with which this happens. There again, while beneficial for a first approximation of physical security, the current models come with significant abstractions. In particular, the deterministic k-fault model cannot capture the imprecise nature of physical attacks due to the probabilistic fault behavior, while the random fault model fails to precisely model low-level physical characteristics of fault injection due to the same independent probability for each fault. Naturally, models for CA combine the capabilities of the individual models. All those models allow the analysis of certain types of secret-dependent leakages and enable pre-silicon evaluation.

Contribution. In this work, we provide a generalization of the probabilistic models for physical attacks by considering arbitrary leakage and fault distributions. In particular, we introduce a general random probing model, a general random fault model, and a general random combined model in Section 3, all of which, but especially our random combined model, are analyzed for interesting properties. Specifically, we analyze the impact of the adversarial knowledge on the injected faults on combined security. Since the resulting analysis complexity is very high, we introduce notions for compositions for all three models in Section 4. For our general random probing model, this is a straightforward extension of an existing notion for the  $\epsilon$ -random probing model. To the best of our knowledge, for the other two models, this is the first attempt at composition in a probabilistic model. Within these security models, we investigate the formal verification of the proposed combined composition notions for gadgets. Specifically, we introduce two methods of tool-based analysis using VERICA [37] and IronMask [11]. We explain how to extend these tools to verify the proposed notions and present the implementation details in Section 5. In particular, our extension of VERICA can analyze arbitrary circuits with exact precision (up to some threshold) but is comparably slow. In contrast, our extension of IronMask is much faster but has restrictions in the type of designs it can handle and makes some approximations. We finally provide an extensive evaluation and comparison of the tools in Section 6.

## 2 Preliminaries

In the following, we give a short overview of the used notation and circuit model. Afterwards, we provide the basic concepts required to understand the contribution of this paper. Specifically, we introduce countermeasures for SCA and FIA, and discuss security proofs via simulation.

#### 2.1 Notation

Throughout the paper, we use a sans-serif font for functions (e.g., f) and an upper-case calligraphic font for sets (e.g., S). We designate  $\overline{S}$  the complement

#### 4 Belaïd et al.

of a set S, |S| its cardinality, and  $\mathbb{D}S$  a discrete probability distribution defined over the event set S. Further, we name  $\prod_i \mathbb{D}S_i$  the joint probability distribution of independent distributions  $\mathbb{D}S_i$  where the joint probability is computed as the multiplication of the individual probabilities, i.e.,  $\Pr[a \cap b] = \Pr[a] \cdot \Pr[b]$ , and with  $\equiv$  the equality of distributions. To simplify the notation for n-times replication we denote with  $\mathbb{V}_n = \{(0)^n, (1)^n\}$  the set that contains the zero vector  $(0)^n$  and the one vector  $(1)^n$  of size n. Other notations will be introduced throughout the paper where necessary.

#### 2.2 Circuit Model

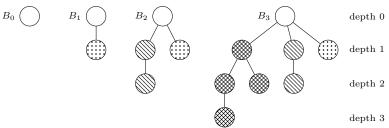

In this work, we model a circuit C as a Direct Acyclic Graph (DAG)  $\mathcal{C} = \{\mathcal{G}, \mathcal{W}\}\$ , where vertices  $g \in \mathcal{G}$  represent logical gates and edges  $w \in \mathcal{W}$  represent wires carrying a Boolean value and connecting individual gates. We restrict the set of combinational gates to  $\mathcal{G}_c = \{inv, and, xor, or\}$  and the set of memory gates to  $\mathcal{G}_{\mathsf{m}} = \{\mathsf{reg}\}.$  Further, we define a set of input and output gates  $\mathcal{G}_{\mathsf{io}} = \{\mathsf{in}, \mathsf{out}\},$ where in produces and out absorbs a Boolean value, and a set of probabilistic gates  $\mathcal{G}_{rand} = \{rand\}$ , where rand produces a uniform-random Boolean value. Finally, we define the set of constant gates  $\mathcal{G}_{const} = \{zero, one\}$ , where each gate produces the respective Boolean value. Hence, each gate is from the set  $\mathcal{G}_{\mathsf{all}} = \mathcal{G}_{\mathsf{c}} \cup \mathcal{G}_{\mathsf{m}} \cup \mathcal{G}_{\mathsf{io}} \cup \mathcal{G}_{\mathsf{rand}} \cup \mathcal{G}_{\mathsf{const}}$ . Given this, each gate implements a deterministic or probabilistic Boolean function  $f_g: \mathbb{F}_2^h \to \mathbb{F}_2$ , with  $0 \leq h \leq 2$ , of the respective functionality. Further, let  $\mathcal{G}_f = \{\mathbb{F}_2^h \to \mathbb{F}_2 \mid h \leq 2\}$  be the set of all possible Boolean functions for this purpose. With respect to the fan-out of wires, we consider two different scenarios depending on the analysis of hardware or software. For hardware (cf. Section 5.2), we create a copy of the wire for each gate that is connected, i.e., for a wire with fan-out n we create n copies. Here a gate output can be connected to any number of copies of the same wire. For software (cf. Section 5.3), we say that each gate can have at most one output and introduce a special copy operation, that outputs two times the input. Hence, to represent a wire with fan-out n we require 2n-1 wires to construct a tree of copys.

#### 2.3 Countermeasures

**Masking.** A popular countermeasure against SCA is *Boolean masking* [14,29], due to its sound formal foundation. The core idea is to split a secret  $x \in \mathbb{F}_2$  into a vector  $\langle x_0, \dots, x_{s-1} \rangle \in \mathbb{F}_2^s$ , with  $x_i \in \mathbb{F}_2$ , such that  $x = \bigoplus_{i=0}^{s-1} x_i$  and each subset  $\{x_i \mid i \in [0, s-1]\}$  with cardinality smaller than s is statistically independent of x. We refer to a component  $x_i$  as a *share* of x with *share index* i. Similarly, a circuit is transformed to a *masked circuit*, which operates over shares of the inputs. In this paper, we assume the initial encoding enc of inputs and the final decoding dec of outputs (generating shares or recreating the secret, respectively) not as part of the masked circuit.

**Replication.** A popular countermeasure against FIA is the replication of the circuit in combination with a majority function for error correction purposes. In particular, a value  $x \in \mathbb{F}_2$  is replicated to a vector  $\langle x_0, \ldots, x_{n-1} \rangle \in \mathbb{F}_2^n$  with n = 2k + 1, such that  $\forall i, j \in [0, n - 1] : x_i = x_j$ . Then, up to k faults can be corrected with a majority function maj. Likewise, a circuit is replicated n times, where every replication operates on a unique set of value replications.

## 2.4 Security Proofs via Simulation

Security proofs in the context of SCA are often conducted based on *simulation*. For this, two worlds are introduced. The first world represents a real implementation, while the second world is made trivially secure by removing the secret that an adversary tries to learn. If an adversary is not able to distinguish between the two worlds then the view of the adversary is proven to be independent of the secret. The proof works by construction of a simulator that recreates the distribution of the observed values without access to any secret.

However, in this work, we do not require perfect simulation but allow the simulator to be wrong with a small probability. In particular, we require a simulator to create a distribution that is  $\epsilon$  close to the observed distribution. We say that any two probability distributions  $\mathbb{D}_1$  and  $\mathbb{D}_2$  are  $\epsilon$ -close ( $\mathbb{D}_1 \approx_{\epsilon} \mathbb{D}_2$ ) if their statistical distance is upper-bounded by  $\epsilon$ , i.e.,

$$\frac{1}{2}\sum_{x}|\mathsf{Pr}_{\mathbb{D}_{1}}[x]-\mathsf{Pr}_{\mathbb{D}_{2}}[x]|\leq\epsilon.$$

# 3 Security Model

We start our contribution by defining probabilistic security models for SCA, FIA, and CA. For this, we build on existing models but capture a more general attack scenario.

## 3.1 General Random Probing Security

Adversary Model. We introduce a new generalization of the random probing model [31,2,10] called general random probing model. Here, a probing adversary  $\mathcal{A}_p$  can invoke a circuit C multiple times and on each invocation, the exact values of a random subset of wires in C are leaked to  $\mathcal{A}_p$ . We denote the leaking combination of wires, i.e., the subset of the wires of the circuit that is given to  $\mathcal{A}_p$ , with  $\tilde{\mathcal{W}} \subseteq \mathcal{W}$ . Let  $\mathcal{W}^{\infty} = \{\tilde{\mathcal{W}} \subseteq \mathcal{W}\}$  be the set of all wire combinations in C and  $\mathbb{D}\mathcal{W}^{\infty}$  an arbitrary discrete probability distribution defined over  $\mathcal{W}^{\infty}$ . Further, we define the following two functions to first select a random element from  $\mathcal{W}^{\infty}$  and then determine the values carried by the selected wires for a given input:

LeakingWires $(C, \mathbb{D}W^{\infty})$ : The leaking-wire sampler selects for a given circuit C a wire combination  $\tilde{W}$  with probability  $\mathsf{Pr}_{\mathbb{D}W^{\infty}}[\tilde{W}]$ .

AssignWires $(C, \tilde{W}, x)$ : The assign-wire sampler takes a fixed input x for C and outputs the values assigned to the wires  $w \in \tilde{W}$  as a tuple in  $\mathbb{F}_2^{|\tilde{W}|}$ . If C is probabilistic so is AssignWires().

Then, the view of  $\mathcal{A}_p$  is formally defined as the random probing leakage  $\mathcal{L}_{\tilde{\mathcal{W}}}(C, x)$ , which is given by the random experiment

$$\tilde{\mathcal{W}} \leftarrow \mathtt{LeakingWires}(C, \mathbb{D}\mathcal{W}^{\infty}),$$

$$\mathcal{L}_{\tilde{\mathcal{W}}}(C, x) \leftarrow \mathtt{AssignWires}(C, \tilde{\mathcal{W}}, x).$$

Security Definition. Intuitively, a circuit C is secure in our model if the view of  $\mathcal{A}_p$  can be simulated with high probability without access to the secret, i.e., there exists a simulator Sim that recreates the distribution of the leaking wires  $\tilde{\mathcal{W}}$  without knowledge of the secret, such that the failure probability of Sim is bounded by some (small)  $\epsilon$ . A more formal definition is given in Definition 1. Throughout this work, we consider enc to be some encoding function, e.g., defined by Boolean masking (cf. Section 2.3).

**Definition 1 (General Random Probing Security).** A circuit C is said to be  $(\mathbb{D}W^{\infty}, \epsilon)$ -random probing secure with respect to an encoding enc if there exists a simulator Sim such that for all inputs x:

$$\operatorname{Sim}(C, \tilde{\mathcal{W}}) \approx_{\epsilon} \mathcal{L}_{\tilde{\mathcal{W}}}(C, \operatorname{enc}(x))$$

.

The required simulator Sim can be constructed by returning a *simulation* failure  $\bot$  whenever the exact distribution  $\mathcal{L}_{\tilde{\mathcal{W}}}(C, \mathsf{enc}(x))$  cannot be recreated without access to x and ensuring that

$$\Pr[\operatorname{Sim}(C, \tilde{\mathcal{W}}) = \perp] = \epsilon$$

and, conditionned to the event  $Sim(C, \tilde{W}) \neq \perp$ ,

$$\operatorname{Sim}(C, \tilde{\mathcal{W}}) \equiv \mathcal{L}_{\tilde{\mathcal{W}}}(C, \operatorname{enc}(x))$$

.

Relation to Random Probing Model. The random probing model [31,2,10] is a specific instance of the above-defined general random probing model. Specifically, the probability distribution  $\mathbb{D}\mathcal{W}^{\infty}$  is selected such that each wire  $w \in \mathcal{W}$  leaks with the same probability p independent of all other wires.

As shown by Duc et al. [22], the random probing model can be seen as an intermediate model between the noisy leakage model [35] and the d-threshold probing model [31]. Here, the assumption of the mutually independent leakage probability p for all wires can be traced to the assumption of equal and mutually independent noise in the noisy leakage model. However, the latter does not necessarily hold in practice, neither in hardware nor in software [9]. By defining the leakage over an arbitrary discrete probability distribution  $\mathbb{D}W^{\infty}$ , we can model scenarios where the noise of two wires is not independent (e.g.,

because they operate in parallel with the same background computation) and, hence, the leakage probability of the two wires is dependent. Similarly, dependencies in the leakage probability can also be caused by physical defaults such as glitches [34,36] and couplings [16,36] or by shared structures like the Power Distribution Network (PDN) [44].

The introduction of the arbitrary discrete probability distribution  $\mathbb{D}\mathcal{W}^{\infty}$  also allows two different wires combinations of one wire  $\{w_i\}$  and  $\{w_j\}$  to have different leakage probabilities  $p_i$  and  $p_j$ , respectively. With that, it enables more fine-grained modeling for the contribution of individual wires to the occurring leakage of wire combinations (by a different weight for the wires  $w_i$  and  $w_j$  to occur). For example, an EM probe usually does not capture the entire circuit but only a subset of neighboring circuit elements. Hence, a subset of wires does not contribute to the leakage at all and can be modeled by wire combinations with zero probability. Modeling this correctly can lead to place-and-route algorithms that take EM probing into account and minimize the observable leakage. Other differences in the leakage probability may be caused by the difference in the driver strengths of individual gates, or even by the type of operation a wire is used for.

By introducing this general model, we hope to fuel research into the nature of physical leakage by looking specifically into the leakage dependencies and contributions of different circuit structures. However, due to the computational blow-up, we will stick to mutually independent leakage probabilities in the practical implementation of our evaluation tools (cf. Section 5).

## 3.2 General Random Fault Security

Adversary Model. We use the adversary model proposed by Feldtkeller et al. [26] that is based on a fault model from Richter-Brockmann et al. [39]. Here, a faulting adversary can invoke a circuit C multiple times, where on each invocation, a random subset of gates are manipulated according to a specified fault transformation. More specifically, a fault consists of a fault location  $g \in \mathcal{G}$ , i.e., a gate of the circuit, and a fault transformation  $\tau: \mathcal{G}_f \to \mathcal{G}_f$ , i.e., a transformation of the Boolean function a gate implements, where the fault model restricts the allowed transformations. Popular fault transformations are, e.g.,  $\tau_{\text{set}}(g) = \text{one}$ ,  $\tau_{\text{reset}}(g) = \text{zero}$ , or  $\tau_{\text{flip}}(g) = \text{inv}(g)$ . Hence, a fault is a pair  $f = (g, \tau)$  and we denote by  $\mathcal{F}$  the set of all possible faults, by  $\mathcal{F}^{\infty} = \{\tilde{\mathcal{F}} \subseteq \mathcal{F}\}$  the set of all possible fault combinations  $\tilde{\mathcal{F}}$  with distinct locations (i.e., each  $g \in \mathcal{G}$  occurs at most once in  $\tilde{\mathcal{F}}$ ), and by  $\mathbb{D}\mathcal{F}^{\infty}$  an arbitrary distribution defined over  $\mathcal{F}^{\infty}$ . We define the following function to select a fault combination for a single circuit invocation:

AssignFaultGates $(C, \mathbb{D}\mathcal{F}^{\infty})$ : For a given circuit C, the faulty-gate sampler selects a fault combination  $\tilde{\mathcal{F}}$  with probability  $\mathsf{Pr}_{\mathbb{D}\mathcal{F}^{\infty}}[\tilde{\mathcal{F}}]$  and outputs the modified circuit  $C^{\tilde{\mathcal{F}}}$  that we refer to as a faulty circuit.

Note that  $\tilde{\mathcal{F}}$  can be empty and, if  $\mathsf{Pr}_{\mathbb{D}\mathcal{F}^{\infty}}[\emptyset] > 0$ , then the sampler can output the original circuit  $C = C^{\emptyset}$ . For the sake of simplicity, it still falls within the definition of a faulty circuit.

The original adversary model introduced by Feldtkeller et al. provides the adversary with a correct and a faulty output of the circuit C. For our purposes, we define the leakage of faults by the correctness of the output, which is a conservative but popular choice for fault security [5,20,37,38]. For that, we define a decoding or correction gadget for the context of faulty circuits:

$G^D$ : The decoding gadget realizes a function such that, given an input with at most k bit faults, outputs a corrected result.

Then, we define the leakage by the correctness of the output of the faulty circuit. More formally, we define the random fault leakage  $\mathcal{L}_{\tilde{\mathcal{F}}}(C,x)$  as the output of the random experiment, with

$$\begin{split} C^{\tilde{\mathcal{F}}} &\leftarrow \mathtt{AssignFaultGates}(C, \mathbb{D}\mathcal{F}^{\infty})\,, \\ \mathcal{L}_{\tilde{\mathcal{F}}}(C) &\leftarrow \begin{cases} 0 & \text{if } \forall x : C(x) = G^D(C^{\tilde{\mathcal{F}}}(x))\,, \\ 1 & \text{else}. \end{cases} \end{split}$$

In contrast to  $\mathcal{L}_{\bar{\mathcal{W}}}(C, \mathsf{enc}(x))$ , the random fault leakage is not a distribution but, for each fault combination  $\tilde{\mathcal{F}}$ , a constant Boolean value. With this, we define the view of the adversary  $\mathcal{A}_f$ , after injecting a random fault into a circuit C, as  $\mathcal{L}_{\tilde{\mathcal{F}}}(C)$ . Note, that we focus on correction-based countermeasures here. However, detection-based countermeasures can be treated analogously by considering the result secure if a fault was detected correctly.

As with the general random probing model, this adversary model allows the modeling of a wide range of different adversarial capabilities [26]. For example, the set of fault combinations  $\mathcal{F}^{\infty}$  can be set to register combinations with long computation paths to model clock glitches. Or it can be set to a set of adjacent gates to model a laser attack. Similarly, a distribution of faults  $\mathbb{D}\mathcal{F}^{\infty}$  with a small variance can be used to model an adversary with precise faulting capabilities, while a broader distribution can be used for a more dispersed fault behavior.

Security Definition. We extend the above adversary models by providing an appropriate definition for security. Intuitively, we say a fault combination leads to an insecure circuit behavior if there exists some input assignment that cannot be corrected at the output. This is a very conservative assumption, in that it assumes an adversary who can exploit every effective fault at the output to gain full knowledge of the secret, and is popular in the literature [5,20,37,38]. To account for the random behavior of our adversary model, we say a circuit is random fault secure if the probability that the adversary will get exploitable information is bounded by some (small)  $\mu$ .

**Definition 2 (General Random Fault Security).** A circuit C is  $(\mathbb{D}\mathcal{F}^{\infty}, \mu)$ -random fault secure with respect to a decoding  $G^D$  if:

$$\Pr[\mathcal{L}_{\tilde{\mathcal{F}}}(C) = 1] \leq \mu$$

,

where  $\mathcal{L}_{\tilde{\mathcal{F}}}()$  is computed from the random experiment

$$C^{\tilde{\mathcal{F}}} \leftarrow \mathtt{AssignFaultGates}(C, \mathbb{D}\mathcal{F}^{\infty}).$$

In this definition, the decoding gadget required for the computation of the fault leakage  $\mathcal{L}_{\tilde{\mathcal{F}}}(C)$  cannot be faulted by  $\mathcal{A}_f$ . This is symmetric to the encoding enc in random probing security, which is not probed, and can be justified by the fact that a fault in a final correction can only leak the output of the circuit. Note, however, that any correction implemented within the circuit is subject to faults in our model.

Relation to Random Fault Model. Dhooghe and Nikova already proposed a random fault model [19], which is inspired by the random probing model. However, their model differs from our proposal in two key features: (i) They consider faults in wires allowing only the fault transformations set, reset, and flip. In contrast, we model faults by a transformation of gate functions which allows a wide range of possible fault scenarios, including set, reset, and flip [39]. (ii) They consider an adversary that has precise control over the location of the fault where the occurrence of the fault is randomly determined by an independent probability  $\kappa$ . In contrast, we allow an arbitrary distribution over fault combinations. Hence, different fault locations can be dependent and the fault type can be uncertain as well. This allows a wide range of possible adversarial scenarios [26]. Therefore, our new model is a generalization of the previously proposed random fault model.

#### 3.3 General Random Combined Security

Adversary Model. We now introduce a model for an adversary that can both inject faults and place probes simultaneously. As such, the resulting *combined* adversary will have the capability to manipulate a random set of gates of a circuit. Then, both the exact values of a random subset of wires and the correctness of the circuit are leaked to the adversary. To formally capture the view of the adversary, we define the random combined leakage  $\mathcal{L}_{\tilde{W},\tilde{\mathcal{F}}}(C,x)$  as the output of the random experiment

$$\begin{split} C^{\tilde{\mathcal{F}}} \leftarrow \mathtt{AssignFaultGates}(C, \mathbb{D}\mathcal{F}^{\infty})\,, \\ \tilde{\mathcal{W}} \leftarrow \mathtt{LeakingWires}(C^{\tilde{\mathcal{F}}}, \mathbb{D}\mathcal{W}^{\infty})\,, \\ \mathcal{L}_{\tilde{\mathcal{W}}, \tilde{\mathcal{F}}}(C, x) \leftarrow \mathtt{AssignWires}(C^{\tilde{\mathcal{F}}}, \tilde{\mathcal{W}}, x) \parallel \mathcal{L}_{\tilde{\mathcal{F}}}(C)\,. \end{split}$$

Again, we assume a correction-based countermeasure for simplicity. When detection is used, it is important to include the detection flag in the random combined leakage (which then need to be simulated alongside the leaking wires).

Considering the SCA aspect of CA, we require for security that the leaking wires  $\tilde{\mathcal{W}}$  can be simulated without knowledge of the secret. However, for simulation, the adversarial knowledge of the faulty circuit makes a difference. Imagine

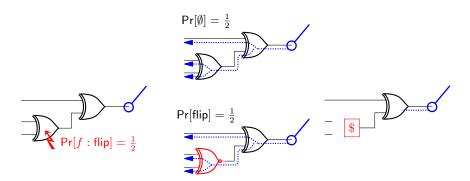

(a) Fault scenario with a probabilistic flip fault. (b) View of the simulator with abilistic flip fault. (c) View of the simulator with abilistic flip fault. (c) View of the simulator with a known fault distribution  $\mathbb{D}\mathcal{F}^{\infty}$ .

Fig. 1. Difference when knowing the injected fault versus knowing only the fault distribution. When knowing the fault the circuit is deterministic (for deterministic inputs) and a probe on the output propagates to all inputs. When only the fault distribution is known, the circuit can get probabilistic (even with deterministic inputs) potentially stopping the propagation of probes.

the scenario in Figure 1, where a flip fault is injected into a xor chain with probability  $\frac{1}{2}$ . If the adversary knows the faulty circuit  $C^{\tilde{\mathcal{F}}}$  (and, hence,  $C^{\tilde{\mathcal{F}}}$  is given to the simulator) then all deterministic inputs to the xor chain are required to simulate the probe at the end in both cases (non-faulty/faulty). In contrast, if the adversary does not know  $C^{\tilde{\mathcal{F}}}$  (and only the fault distribution  $\mathbb{D}\tilde{\mathcal{F}}^{\infty}$  is given to the simulator) then the fault randomizes the intermediate value and the output of the final xor can be simulated by a uniform random value. Hence, the fault effectively works as a mask refreshing. For this, we introduce two different combined adversaries: one without and one with knowledge of the faulty circuit.

- i) Unknown-Fault Random Combined Adversary. Our first adversary  $\mathcal{A}_{uc}$  is the combination of  $\mathcal{A}_p$  and  $\mathcal{A}_f$  without knowledge of the randomly chosen fault combination  $\tilde{\mathcal{F}}$ . Specifically, the adversary gets no access to the faulty circuit  $C^{\tilde{\mathcal{F}}}$  and the corresponding simulator gets only the circuit C and the fault distribution  $\mathbb{D}\mathcal{F}^{\infty}$  as input. Hence, the view of  $\mathcal{A}_{uc}$  is defined by  $\mathcal{L}_{\tilde{\mathcal{W}},\tilde{\mathcal{F}}}(C,x)$  and the effects of fault injection and probing is interleaved, i.e., we analyze the circuit in Figure 1c.

- ii) Known-Fault Random Combined Adversary. The second adversary  $\mathcal{A}_{kc}$  is the combination of  $\mathcal{A}_p$  and  $\mathcal{A}_f$  with additional knowledge of the faulty circuit  $C^{\tilde{\mathcal{F}}}$  (or equivalently, the selected fault combination  $\tilde{\mathcal{F}}$ ). For this, the corresponding simulator has access to  $C^{\tilde{\mathcal{F}}}$  for the simulation of the leaking wires. With this, the view of  $\mathcal{A}_{kc}$  is defined by  $\mathcal{L}_{\tilde{\mathcal{W}},\tilde{\mathcal{F}}}(C,x) \parallel \tilde{\mathcal{F}}$ . Since the faulty circuit is known, we can analyze  $\mathcal{L}_{\tilde{\mathcal{W}}}(C^{\tilde{\mathcal{F}}},x)$  and  $\mathcal{L}_{\tilde{\mathcal{F}}}(C)$  independently, i.e., after the fault injection, we only consider one of the two circuits in Figure 1b.

When comparing the two adversaries, it becomes apparent that  $\mathcal{A}_{uc}$  is the more realistic adversary model for CA because, in a real-world circuit, the adversary usually does not know the exact effect of an injected fault. However, the uncertainty about the faults makes the analysis of combined security much more complex, due to the reciprocal effects of faults and probes. Fortunately, we can show that any circuit secure against  $\mathcal{A}_{kc}$  is also secure against  $\mathcal{A}_{uc}$ . For this, we see  $\mathcal{A}_{kc}$  mostly as a useful abstraction for analysis, allowing a clear path to security verification.

In this sense, we can make a further distinction in the knowledge an adversary has about the effect of fault injection. Specifically, we can separate the knowledge about the fault location and its effect. For this, we use the known-fault adversary  $\mathcal{A}_{kc}$  in combination with a fault transformation to a probabilistic gate function  $f_g$ , i.e.,  $f_g$  has an internal random tape that impacts the output of the gate. While this pushes the analysis closer to  $\mathcal{A}_{uc}$ , it is important to evaluate the correctness of the circuit for all values of the random tape, i.e.,  $\mathcal{L}_{\tilde{\mathcal{F}}}(C) = 0$  if the output can be corrected for all inputs and random values of probabilistic gate functions.

Our model also allows to go in the opposite direction by empowering  $\mathcal{A}_{kc}$  with direct control over the injected fault. Hence, we can model a *chosen-fault* combined adversary as the adversary  $\mathcal{A}_{kc}$  that can freely choose the fault distribution  $\mathbb{D}\mathcal{F}^{\infty}$  of a (restrict) set of fault combinations  $\mathcal{F}^{\infty}$ . In most cases, this will lead to an adversary that directly chooses the location and transformation of the injected fault, since any uncertainty will reduce the advantage of the adversary, which removes the random nature of the model. Note, if the set  $\mathcal{F}^{\infty}$  is restricted to the set of all gate combinations with up to k faults, this model is equivalent to the popular threshold fault model [1,5,30,38,45]. However, since the semantics of the security definition do not change (we do not care how the fault distribution is generated), we do not introduce a specific adversary model for this case.

Security Definition. We provide security definitions for the setting of combined adversaries. Intuitively, we say that a circuit is combined-secure if the view of the corresponding adversary can be simulated and the output can be corrected with high probability. For this, we introduce a new security parameter  $\gamma$  that represents the advantage of the adversary, i.e., the probability that the adversary gains some knowledge about the secret. In the combined setting, the adversary wins if either there exists some fault leakage ( $\mathcal{L}_{\tilde{\mathcal{T}}}(C) = 1$ ) or the leaking wires in the faulty circuit cannot be simulated without knowledge of the secret. To overcome the dependencies between those two events, we only conduct the simulation of the leaking wires if there is no fault leakage. Hence, we get the following two parameters (where we usually choose the lowest possible value):

$$\begin{split} \mu & \geq \Pr[\mathcal{L}_{\tilde{\mathcal{F}}}(C) = 1] \,, \\ \epsilon & \geq \Pr[\operatorname{Sim}(C, \tilde{\mathcal{W}}) \equiv \perp \mid \mathcal{L}_{\tilde{\mathcal{F}}}(C) = 0] \,. \end{split}$$

Here,  $\mu$  is defined exactly as in Definition 2, while  $\epsilon$  is the probability that the simulation fails knowing that  $\mathcal{L}_{\tilde{\mathcal{F}}}(C) = 0$ . We then express the advantage of the

combined adversary by

$$\gamma \ge \mu + (1 - \mu)\epsilon$$

.

To compute  $\epsilon$ , we introduce a new subset of the fault combination  $\mathcal{B} \subseteq \mathcal{F}^{\infty}$ , such that  $\mathcal{B}$  captures all fault combinations that always yield a result that can be corrected, i.e.,  $\mathcal{B} = \{\tilde{\mathcal{F}} \in \mathcal{F}^{\infty} \mid \mathcal{L}_{\tilde{\mathcal{F}}}(C) = 0\}$ . Then, we define the distribution  $\mathbb{D}\mathcal{B}$  as the scaled distribution  $\mathbb{D}\mathcal{F}^{\infty}$  conditioned to the event  $\mathcal{L}_{\tilde{\mathcal{F}}}(C) = 0$ .

We start with the security definition for the adversary  $\mathcal{A}_{uc}$ , where the random combined leakage needs to be simulated. In a sense, this is the most natural definition as the adversary has no knowledge about the circuit transformation caused by the injected fault.

**Definition 3 (Unknown-Fault Random Combined Security).** A circuit C is  $(\mathbb{D}W^{\infty}, \mathbb{D}\mathcal{F}^{\infty}, \gamma)$ -Unknown-Fault Random Combined Secure (RCS<sub>UF</sub>) with respect to an value encoding enc and a error decoding  $G^D$  if there exists some  $\mu, \epsilon \leq 1$  such that C is  $(\mathbb{D}\mathcal{F}^{\infty}, \mu)$ -random fault secure with respect to  $G^D$ , there exists a simulator Sim such that for all inputs x:

$$\mathsf{Sim}(C, \mathbb{D}\mathcal{F}^{\infty}) \approx_{\epsilon} \mathcal{L}_{\mathbb{D}\mathcal{W}^{\infty}, \mathbb{D}\mathcal{B}}(C, \mathsf{enc}(x)),$$

and

$$\mu + (1 - \mu)\epsilon \leq \gamma$$

,

where  $\mathcal{L}_{\mathbb{D}W^{\infty},\mathbb{D}\mathcal{B}}()$  is computed from the random experiment

$$\begin{split} \tilde{\mathcal{W}} \leftarrow \texttt{LeakingWires}(C, \mathbb{D}\mathcal{W}^{\infty})\,, \\ C^{\tilde{\mathcal{F}}} \leftarrow \texttt{AssignFaultGates}(C, \mathbb{D}\mathcal{B})\,. \end{split}$$

While simple, this definition is difficult to analyze due to the interleaving of probes and faults within the simulator. Therefore, we provide a second security definition tailored to  $\mathcal{A}_{kc}$ . Because this adversary knows the faulty circuit  $C^{\tilde{\mathcal{F}}}$ , the interleaving of probes and faults is eliminated. Hence, the analysis gets simpler and we will later show that security in this model implies security with unknown faults.

**Definition 4 (Known-Fault Random Combined Security).** A circuit C is  $(\mathbb{D}\mathcal{W}^{\infty}, \mathbb{D}\mathcal{F}^{\infty}, \gamma)$ -Known-Fault Random Combined Secure (RCS<sub>KF</sub>) with respect to an value encoding enc and an error decoding  $G^D$  if there exists some  $\mu, \epsilon \leq 1$  such that C is  $(\mathbb{D}\mathcal{F}^{\infty}, \mu)$ -random fault secure with respect to  $G^D$ , there exists a simulator Sim such that for all inputs x it holds that

$$\begin{split} C^{\tilde{\mathcal{F}}} \leftarrow \mathtt{AssignFaultGates}(C, \mathbb{D}\mathcal{B})\,, \\ \mathsf{Sim}(C^{\tilde{\mathcal{F}}}) \lessapprox_{\epsilon} \mathcal{L}_{\tilde{\mathcal{W}}}(C^{\tilde{\mathcal{F}}}, x), \end{split}$$

and

$$\mu + (1 - \mu)\epsilon \leq \gamma$$

,

where  $\mathcal{L}_{\tilde{\mathcal{W}}}()$  is computed from the random experiment

$$ilde{\mathcal{W}} \leftarrow \mathtt{LeakingWires}(\mathit{C}^{ ilde{\mathcal{F}}}, \mathbb{D}\mathcal{W}^{\infty})$$

.

Reduction between Security Definitions. It is evident that the adversary  $\mathcal{A}_{kc}$  has more knowledge about the probed circuit structure than  $\mathcal{A}_{uc}$ . Hence, it seems reasonable that RCS<sub>UF</sub> is the more general security notion and we can reduce its security to  $RCS_{KF}$ . In other words, if a circuit is  $RCS_{KF}$ , then it is always RCS<sub>IIF</sub>.

In particular, we can show that if there exists a simulator  $Sim_{KF}$  for the adversary  $A_{kc}$  then we can always construct a simulator  $Sim_{UF}$  for the adversary  $\mathcal{A}_{uc}$  with at most the failure probability of  $\mathsf{Sim}_{KF}$ . For that, consider that RCS<sub>KF</sub> requires the simulation for a given but randomly chosen faulty circuit  $C^{\tilde{\mathcal{F}}}$ . Hence, we can compute the failure probability of  $\mathsf{Sim}_{KF}$  as the sum of the failure probability for each faulty circuit weighted by the probability of that circuit to occur, i.e.,

$$\epsilon_{kf} = \sum_{\tilde{\mathcal{F}}} \Pr[\tilde{\mathcal{F}}] \epsilon_{kc}^{\tilde{\mathcal{F}}}, \tag{1}$$

where  $\epsilon_{kc}^{\tilde{\mathcal{F}}}$  is the failure probability of  $\mathsf{Sim}_{KF}$  given the faulty circuit  $C^{\tilde{\mathcal{F}}}$ . We can then construct a simulator that randomly selects a faulty circuit and calls  $Sim_{KF}$ for the wire simulation. Note, that standalone fault security is not affected by the choice of the adversary. We show a more formal argumentation below.

**Theorem 1.** Let C be a circuit that is  $(\mathbb{D}W^{\infty}, \mathbb{D}\mathcal{F}^{\infty}, \gamma_{kc})$ -RCS<sub>KF</sub>. Then C is  $(\mathbb{D}\mathcal{W}^{\infty}, \mathbb{D}\mathcal{F}^{\infty}, \gamma_{uc})$ - $RCS_{UF}$  with  $\gamma_{uc} \leq \gamma_{kc}$ .

*Proof.* Let C be a  $(\mathbb{D}\mathcal{W}^{\infty}, \mathbb{D}\mathcal{F}^{\infty}, \gamma_{kc})$ -RCS<sub>KF</sub> circuit. Then, by definition of  $RCS_{KF}$ , C is  $(\mathbb{D}\mathcal{F}^{\infty}, \mu)$ -random fault secure and there exists a simulator  $Sim_{KF}$ with failure probability  $\epsilon_{kc}$  for the probing leakage  $\mathcal{L}_{\tilde{\mathcal{W}}}(C^{\tilde{\mathcal{F}}},x)$  such that

$$\gamma_{kc} \geq \mu + (1-\mu)\epsilon_{kc}$$

.

Now we construct a simulator  $Sim_{UF}$  for  $RCS_{UF}$  out of  $Sim_{KF}$ . This is possible because  $\mathsf{Sim}_{UF}$  has to simulate the same events as  $\mathsf{Sim}_{KF}$  since the set of fault combinations with  $\mathcal{L}_{\tilde{\mathcal{F}}}(C) = 1$  remains untouched by the knowledge of the adversary. The simulator  $\dot{S}im_{UF}$  is constructed by the following two steps:

- 1. Call  $C^{\tilde{\mathcal{F}}} \leftarrow \texttt{AssignFaultGates}(C, \mathbb{D}\mathcal{B}),$

- 2. Return  $Sim_{KF}(C^{\tilde{\mathcal{F}}}, \tilde{\mathcal{W}})$ .

When this simulator does not fail it is a perfect simulation of the leaking wires because it draws  $\tilde{\mathcal{F}}$  from the correct distribution and  $\mathsf{Sim}_{KF}$  produces a perfect simulation for any faulty circuit  $C^{\tilde{\mathcal{F}}}$  (if it does not fail). Given this, the failure probability of  $Sim_{UF}$  is given by

$$\epsilon_{uf} = \sum_{\tilde{\mathcal{F}}} \Pr[\tilde{\mathcal{F}}] \epsilon_{kc}^{\tilde{\mathcal{F}}} \,,$$

where  $\epsilon_{kc}^{\tilde{\mathcal{F}}}$  is the failure probability of  $\mathsf{Sim}_{KF}$  given the faulty circuit  $C^{\tilde{\mathcal{F}}}$ . Hence, we have  $\epsilon_{uc} = \epsilon_{kc}$  (see Equation 1) for this simulator (however, there could be a simulator with a smaller failure probability). Together with  $(\mathcal{F}^{\infty}, \mu)$ -random fault security of C, it follows that C is  $(\mathbb{D}\mathcal{W}^{\infty}, \mathbb{D}\mathcal{F}^{\infty}, \gamma_{uc})$ -RCS<sub>UF</sub> with  $\gamma_{uc} \leq \gamma_{kc}$ .

In the remainder of this paper, we will mostly focus on  $\mathrm{RCS}_{\mathrm{KF}}$  for the sake of simplicity.

Relation Random Combined Model. In addition to the random fault model, Dhooghe and Nikova also propose a combined version of the random probing and random fault model [19]. Their model does not leak the exact occurring fault to the adversary (similar to  $RCS_{UF}$ ). Since they use their version of the random fault model and the traditional random probing model, the combination has the same limitations as the individual models. In addition, our model introduces a new security parameter  $\gamma$  that captures the overall advantage of the combined adversary. As with the individual models, the parameters of our combined model can be chosen such that it is equal to the definition from Dhooghe and Nikova. While Dhooghe and Nikova propose this model in an appendix of their work, they do not conduct any analysis or further investigations of it.

## 4 Compositional Notions

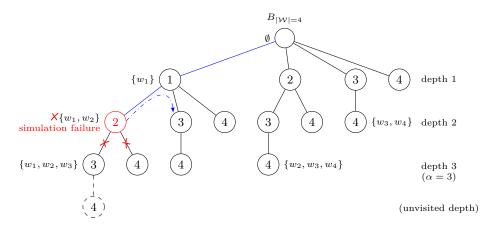

Analyzing entire circuits for their security is often prohibitively complex. As a result, the research community focuses on the construction of so-called *gadgets*, i.e., small circuits implementing a small function (often single binary operations) in a secure manner such that security is guaranteed even under composition [7,10,13,20,27,37]. To abstractly argue about the security via composition, we first define a *composability notion*, which defines the properties a gadget must fulfill, usually, by restricting the propagation of leakage or faults. Second, we outline and prove the conditions of composition, i.e., how the gadgets can be securely combined, in a *composition theorem*.

# 4.1 Composition in the Random Probing Model

For the general random probing model, we can build upon the notion of Random Probing Composability (RPC) proposed by Belaïd et al. [10] and extend it for general distributions. At a high level, RPC provides  $\mathcal{A}_p$  with the usual random probing leakage for the gadget and additionally with a tuple  $\mathcal{O}$  of arbitrary but bounded sets of probes on shares of each output. More specifically, for each unshared output with index i, there is a bounded set  $\mathcal{O}_i$  that contains the share indices of the probed output shares. Then, a gadget is composable if the view of  $\mathcal{A}_p$  can be simulated with high probability using only bounded sets of input shares, i.e., for each unshared input i the simulator requires only a bounded set of share indices  $\mathcal{I}_i$ . Here, the set of input and output shares are bounded by the same parameter d, i.e.,  $|\mathcal{O}_i| \leq d$  and  $|\mathcal{I}_i| \leq d$ . The extension to arbitrary probability distributions is straightforward: the internal wire selection uses  $\mathbb{D}\mathcal{W}^{\infty}$  instead of a wire-independent leakage probability.

Definition 5 (General Random Probing Composability (GRPC)). A gadget  $G: (\mathbb{F}_2^s)^h \to (\mathbb{F}_2^s)^m$  is  $(d, \mathbb{D}W^{\infty}, \epsilon)$ -GRPC if there exists a deterministic

algorithm ShareSelect and a probabilistic simulator Sim such that for every input x and for every tuple of sets  $\mathcal{O} = (\mathcal{O}_i)_{i \in [m]}$ , with  $\forall i : \mathcal{O}_i \subseteq [s]$  and  $|\mathcal{O}_i| \leq d$ , there exists a  $\epsilon \leq 1$  such that the random experiment

$$\begin{split} \tilde{\mathcal{W}} \leftarrow \texttt{LeakingWires}(G, \mathbb{D}\mathcal{W}^{\infty}) \\ \mathcal{I} := (\mathcal{I}_1 \dots \mathcal{I}_h) \leftarrow \texttt{ShareSelect}(\tilde{\mathcal{W}}, \mathcal{O}) \\ out \leftarrow \mathsf{Sim}(x|_{\mathcal{I}}, \mathcal{I}, \mathcal{O}, \tilde{\mathcal{W}}) \end{split}$$

yields

$$\Pr[(|\mathcal{I}_1| > d) \lor \ldots \lor (|\mathcal{I}_h| > d)] \le \epsilon$$

$$out \equiv (\texttt{AssignWires}(G, \tilde{\mathcal{W}}, x), y|_{\mathcal{O}}),$$

with  $y \leftarrow G(x)$ .

Arguing about the composition of gadgets requires knowledge of the joint probability distribution for the leakage in multiple gadgets. Using a complex (and for some scenarios more realistic) joint probability distribution, where the leakage of different gadgets is mutually dependent, contradicts the core idea of composition, i.e., the independent analysis of individual gadgets. Hence, in the following, we assume mutually independent leakage distributions for each gadget. While this is certainly a restriction in the generality of our notion, we think it is justified by the significant gains of the gadget-based approach.

Gadgets supporting GRPC can be composed in an arbitrary way as long as each output of a gadget is used only once as input to another gadget. However, the failure probability increases linearly with the number of used gadgets. Our theorem is actually a generalization of Theorem 1 from Belaïd et al. [10], and the proof is similar except for the computation of the global failure probability. Instead of being  $1 - (1 - \epsilon)^{|C|}$ , bounded by  $|C| \cdot \epsilon$ , the latter naturally becomes  $1 - \prod_{i=1}^{|C|} (1 - \epsilon_i)$  to reflect more tightly the individual gadget-simulation failures.

**Theorem 2.** Let C be a circuit constructed by composition of  $(d, \mathbb{D}W_i^{\infty}, \epsilon_i)$ -GRPC gadgets  $G_i$ , for  $i \in \{1, \ldots, |C|\}$ , such that each output of  $G_i$  is used as input of at most one other gadget  $G_j$  or as output of C. Given this, C is  $(\prod_{i=1}^{|C|} \mathbb{D}W_i^{\infty}, 1 - \prod_{i=1}^{|C|} (1 - \epsilon_i))$ -random probing secure.

Relation to (Random) Probing-Secure Composition. As mentioned, our notion is a direct extension of RPC [10] to arbitrary probe distributions. Another concept for the construction of random probing secure circuits is expansion [4,10]. For this, a circuit compiler, which replaces each gate with a respective secure gadget, is applied e-times to a circuit. Hence, for e=1, we get the normal gadget-based approach. However, for e=2, each share in the previous masked circuit is shared again and each gate of a gadget is replaced with the respective gadget of the gate again. In essence, this reduces the leakage probability of wires as now the simulation of entire gadgets needs to fail in order to leak a single share (of the originally masked circuit). Hence, the leakage probability

p is replaced by the simulation-failure probability  $\epsilon$ . Using the right gadgets can result in an exponential (in e) security increase, but also an exponential increase in implementation costs. We leave the generalization to arbitrary probe distributions for future work.

In the standard Ishai-Sahai-Wagner (ISW) probing model [31], where an adversary can choose up to d wires to be probed, the requirements for compositions are now well understood. In particular, it requires to restrict and guide the flow of probe propagation through the circuit. While (Strong) Non-Interference ((S)NI) [6,7] restricts the number of input shares that can be used for the simulation of probes, Probe-Isolating Non-Interference (PINI) [13] restricts the location (in terms of share domains) of input shares the simulator can use. Hence, (G)RPC has some similarity with (S)NI, in that it restricts the number of input shares a simulator can access. However, in contrast to (S)NI, the number of shares the simulator can access is a fixed parameter that is independent of the amount of leakage within the gadget.

## 4.2 Composition in the Random Fault Model

We continue with compositional statements for the random fault model. In contrast to the random probing model, to the best of our knowledge, there exists no prior work that looks into the composition of the random fault model. However, because of the duality of probes and faults, we can adapt the above notation from the random probing to the random fault case. However, instead of adding probes on outputs we now consider additional faults on inputs and check for correction instead of simulation.

To properly argue about the composition we need to specify the used countermeasure (similar to masking for probing). Hence, in the following, we will only consider circuits secured by simple repetition against a fault adversary. In particular, we will use 2k+1 repetitions such that a majority vote can be used for the correction of up to k faults. Then, for composition, we consider an adversary that can inject a random fault combination into the gadget where additionally a tuple  $\mathcal{I}'$  of arbitrarily but bounded sets of inputs are potentially manipulated by faults. More specifically, for each input with index i, there is a bounded set  $\mathcal{I}'_i$  that contains the replication indices of inputs that may be affected by a fault. Here, we consider each replication in  $\mathcal{I}'_i$  to be a unique and independent input, to account for all possible distribution changes due to a fault in previous parts of the composed circuit. Hence, a fault on an input wire can be seen as an arbitrary change in the value distribution over  $\mathbb{F}_2$ . Then, a gadget is composable, if the output can be corrected with high probability.

To formally define our notion of composition in the presence of a random fault adversary, we start by defining Restricted Random Fault Composability (RRFC), which states the required property for a fixed tuple of input faults  $\mathcal{I}'$ .

**Definition 6 (Restricted Random Fault Composability).** Let n = 2k+1 and  $\mathcal{I}' = (\mathcal{I}'_i)_{i \in [h]}$  be a tuple of sets such that  $\mathcal{I}'_i \subseteq [n]$ , for all  $i : |\mathcal{I}'_i| \le k$ . A gadget

$G: (\mathbb{F}_2^n)^h \to (\mathbb{F}_2^n)^m$  with is  $(\mathcal{I}', k, \mathbb{D}\mathcal{F}^\infty, \mu)$ -RRFC if there exists a deterministic algorithm ReplicationSelect such that the random experiment

$$\begin{split} G^{\tilde{\mathcal{F}}} &\leftarrow \mathtt{AssignFaultGates}(G, \mathbb{D}\mathcal{F}^{\infty})\,, \\ \mathcal{O}' := (\mathcal{O}'_1, \dots, \mathcal{O}'_m) \leftarrow \mathtt{ReplicationSelect}(G^{\tilde{\mathcal{F}}}, \mathcal{I}') \\ \mathcal{L}_{\mathcal{I}', \tilde{\mathcal{F}}}(G) \leftarrow \begin{cases} 0 & \textit{if } \forall i \leq m : |\mathcal{O}'_i| \leq k\,, \\ 1 & \textit{else}. \end{cases} \end{split}$$

yields

$$\Pr[\mathcal{L}_{\mathcal{I}',\tilde{\mathcal{F}}}(G) = 1] \le \mu$$

$$G^{\tilde{\mathcal{F}}}(x')|_{\overline{\mathcal{Q}'}} \equiv G(x)|_{\overline{\mathcal{Q}'}}$$

for all inputs  $x \in \mathbb{V}_n^h$  and faulty inputs  $x' \in (\mathbb{F}_2^n)^h$  with  $x|_{\overline{T'}} = x'|_{\overline{T'}}$ .

Then, a gadget supports Random Fault Composability (RFC) with some bound  $\mu$  if for all possible tuples  $\mathcal{I}'$  the RRFC failure probability is bounded by  $\mu$ .

**Definition 7 (Random Fault Composability).** A gadget  $G: (\mathbb{F}_2^n)^h \to (\mathbb{F}_2^n)^m$  with n=2k+1 is  $(k,\mathbb{D}\mathcal{F}^\infty,\mu)$ -RFC if for all tuples of sets  $\mathcal{I}'=(\mathcal{I}_i')_{i\in[h]}$  with  $\forall i:\mathcal{I}_i'\subseteq[n]$  and  $|\mathcal{I}_i'|\leq k$  the gadget G is  $(\mathcal{I}',k,\mathbb{D}\mathcal{F}^\infty,\mu_{\mathcal{I}'})$ -RFC and  $\max_{\mathcal{I}'}\{\mu_{\mathcal{I}'}\}\leq\mu$ .

While we split the definition of RFC into two parts (for reasons that become apparent when we look at composition under a combined adversary) it is easy to see that there is a close symmetry with the definition of GRPC. Where GRPC goes through all possible tuples of output probes  $\mathcal{O}$ , RFC goes through all possible tuples of input faults. Where GRPC restricts the number of shares per input the simulator can use for a successful simulation, RFC restricts the number of replications per output that can be affected by a fault.

We now show that gadgets supporting RFC can be composed arbitrarily. Under the assumption of mutually independent fault distributions for each gadget, the failure probability increases linearly with the number of gadgets in the circuit.

**Theorem 3.** Let C be a circuit constructed by composition of  $(k, \mathbb{D}\mathcal{F}_i^{\infty}, \mu_i)$ -RFC gadgets  $G_i$ , for  $i \in \{1, \ldots, |C|\}$ . Then, C is  $(\prod_{i=1}^{|C|} \mathbb{D}\mathcal{F}_i^{\infty}, 1 - \prod_{i=1}^{|C|} (1 - \mu_i))$ random fault secure.

Proof. Let the faulty circuit be  $C^{\tilde{\mathcal{F}}} \leftarrow \mathtt{AssignFaultGates}(C, \prod_{i=1}^{|C|} \mathbb{D}\mathcal{F}_i^{\infty})$ , with  $\tilde{\mathcal{F}}$  the set of faults selected with  $\mathsf{Pr}_{\prod_{i=1}^{|C|} \mathbb{D}\mathcal{F}_i^{\infty}}[\tilde{\mathcal{F}}]$ . We can divide  $\tilde{\mathcal{F}}$  into |C| disjoint fault sets  $\tilde{\mathcal{F}}_i \subseteq \tilde{\mathcal{F}}$  such that  $\tilde{\mathcal{F}}_i$  belongs to  $G_i$  and is selected with  $\mathsf{Pr}_{\mathbb{D}\mathcal{F},\infty}[\tilde{\mathcal{F}}_i]$ .

We go iteratively through the gadgets, starting with the gadgets only connected to the inputs of C. Let  $G_i$  be such a gadget. Then, by definition of  $(k, \mathbb{D}\mathcal{F}_i^{\infty}, \mu_i)$ -RFC, the gadget  $G_i$  is  $(\mathcal{I}'_{G_i}, k, \mathbb{D}\mathcal{F}_i^{\infty}, \mu_i)$ -RRFC for the tuple of

empty sets  $\mathcal{I}'_{G_i} = (\mathcal{I}'_{G_i,j} = \emptyset)_{j \in [h]}$ . Hence, there exists a tuple of sets  $\mathcal{O}'_{G_i}$  such that  $\Pr[\mathcal{L}_{\mathcal{I}'_{G_i},\tilde{\mathcal{F}}}(G) = 1] \leq \mu$  and  $G_i^{\tilde{\mathcal{F}}_i}(x)|_{\overline{\mathcal{O}'_{G_i}}} \equiv G_i(x)|_{\overline{\mathcal{O}'_{G_i}}}$ . We continue with the child gadgets, i.e., gadgets that have inputs connected

We continue with the child gadgets, i.e., gadgets that have inputs connected to outputs of the just handled gadgets and (potentially) inputs of the circuit. Let  $G_j$  be such a gadget. Again, we can create a tuple of sets  $\mathcal{I}'_{G_j}$  out of the respective tuples  $\mathcal{O}'_{G_i}$  of the parent gadgets  $G_i$ . Because of  $(k, \mathbb{D}\mathcal{F}_j^{\infty}, \mu_j)$ -RFC there exists tuple of sets  $\mathcal{O}'_{G_j}$  such that  $\Pr[\mathcal{L}_{\mathcal{I}'_{G_j},\tilde{\mathcal{F}}}(G)=1] \leq \mu$  and  $G_j^{\tilde{\mathcal{F}}_j}(x)|_{\overline{\mathcal{O}'_{G_j}}} \equiv G_j(x)|_{\overline{\mathcal{O}'_{G_j}}}$ . We repeat this process until we reach the outputs of C.

Since we have n=2k+1 replications, we can construct a decoding gadget  $G^D$  for C by computing the majority of the output wires  $w_i^1,\ldots,w_i^n$  for all  $i\in[m]$ . This decoding gadget will correct an output value as long as the number of faulty replications is smaller or equal to k, which is always true if none of the gadgets  $G_i$ , for  $i=1,\ldots |C|$ , fail with respect to RFC. The probability that at least one of |C| gadgets fail is  $1-\prod_{i=1}^{|C|}(1-\mu_i)$ . Hence,  $\Pr[C(x)\equiv G^D(C^{\tilde{\mathcal{F}}}(x))]\leq 1-\prod_{i=1}^{|C|}(1-\mu_i)$ , which shows random fault security of C.

Note, that the above composition loses some tightness in  $\mu$  because a failure of RFC in one gadget does not necessarily mean that the entire circuit is insecure, e.g., if some faults cancel each other out in a later gadget.

Relation to Fault-Secure Composition. To the best of our knowledge, this is the first work establishing a compositional property in the random fault model. However, in the threshold fault model [30], where an adversary can place up to k faults, composition is already discussed and notions usually have a strong symmetry to notions in the ISW probing model. In particular, (Strong) Non-Accumulation ((S)NA) [20] (later refined to Fault (Strong) Non-Interference (F-(S)NI) [37]) restricts the number of faults that can propagate to the output of a gadget, while Fault-Isolating Non-Interference (FINI) [27] limits fault propagation within so-called redundancy domains. Both variants ensure that the number of faults in the replication of a single value does not exceed the threshold that allows correction (detection) of faults. In this sense, our proposed notion has some similarity with (S)NA/F-(S)NI, in that it restricts the number of output replications that are allowed to be affected by a fault. However, similar to the contrast between (G)RPC and (S)NI, the number of allowed faulty outputs is not dependent on the amount of injected faults. Also, we use the same symmetry between faults and probes for the definition of our notion of composition.

#### 4.3 Composition in the Random Combined Model

Finally, we provide a compositional statement for the random combined model, i.e., under an adversary with both faulting and probing capabilities. Here, we consider composition under an adversary that knows the injected fault and use the reduction from Section 3.3 for the adversary with unknown faults. We leave the tighter compositional statement in the setting with unknown faults for future

work. In principle, the following notion is a combination of the two previous notions for the individual cases, however, with subtle differences.

First, we count faults in inputs and outputs per input and output share. More specifically, the tuple of indices for potentially faulty inputs has now a set for each share of each input, i.e.,  $\mathcal{I}' = ((\mathcal{I}'_{i,j})_{i \in [s]})_{j \in [h]}$ , where j is the index of the input and i the share index. The same holds for the tuple of potential faulty outputs  $\mathcal{O}' = ((\mathcal{O}'_{i,j})_{i \in [s]})_{j \in [m]}$ , which is constructed by ReplicationSelect. Hence, we bound the number of allowed faults per input and output share by k.

Second, and in contrast, probes on outputs are extended to all replications of the probed value<sup>4</sup>. Hence, the tuple  $\mathcal{O} = (\mathcal{O}_i)_{i \in [m]}$ , where each  $\mathcal{O}_i$  contains the probed share indices of the *i*'th output, does not change. However, the meaning of  $j \in \mathcal{O}_i$  changes in so far as now all replications of the *j*'th share of the *i*'th output need to be simulated. This is necessary to allow for a wide range of gadget implementations where there are potential interdependencies between different replications, e.g., via a correction module, that allows probe propagation across replications [25]. Similarly, the simulator gets access to all replications of the shares indicated in the tuple  $\mathcal{I} = (\mathcal{I}_i)_{i \in [h]}$ .

Third, we define the failure probability for probe simulation  $\epsilon_{\mathcal{I}'}$  in dependence on the tuple of faulty-input indices  $\mathcal{I}'$ . This is analog to the definition of RRFC (Definition 6) and allows us to iterate over all possible tuples  $\mathcal{I}'$  for our combined composition. In particular, this enables a precise definition of the conditions for Random Probing Composition under Faults (RPCUF), which is essentially Definition 5 under a given tuple of potentially faulty inputs  $\mathcal{I}'$  and a random fault combination  $\tilde{\mathcal{F}} \in \mathcal{F}^{\infty}$ .

**Definition 8 (Random Probing Composition under Faults).** Let  $\mathcal{I}' = ((\mathcal{I}'_{i,j})_{i \in [s]})_{j \in [h]}$  be a tuple of sets such that  $\forall i,j: \mathcal{I}'_{i,j} \subseteq [n]$  and  $|\mathcal{I}'_{i,j}| \leq k$ . A gadget  $G: ((\mathbb{F}^n_2)^s)^h \to ((\mathbb{F}^n_2)^s)^m$  with n=2k+1 is  $(\mathcal{I}', \mathbb{D}\mathcal{F}^\infty, d, \mathbb{D}\mathcal{W}^\infty, \epsilon)$ -RPCUF if there exists a deterministic algorithm ShareSelect and a probabilistic simulator Sim such that for all faulty inputs  $x' \in ((\mathbb{F}^n_2)^s)^h$ , for which there exists an  $x \in (\mathbb{V}^s_n)^h$  with  $x|_{\overline{\mathcal{I}'}} = x'|_{\overline{\mathcal{I}'}}$ , and every tuple of sets  $\mathcal{O} = (\mathcal{O}_1, \ldots, \mathcal{O}_m)$ , with  $\forall i: \mathcal{O}_i \subseteq [s]$  and  $|\mathcal{O}_i| \leq d$ , the random experiment

$$\begin{split} G^{\tilde{\mathcal{F}}} &\leftarrow \mathtt{AssignFaultGates}(G, \mathbb{D}\mathcal{F}^{\infty}) \\ \tilde{\mathcal{W}} &\leftarrow \mathtt{LeakingWires}(G^{\tilde{\mathcal{F}}}, \mathbb{D}\mathcal{W}^{\infty}) \\ \mathcal{I} &:= (\mathcal{I}_1 \dots \mathcal{I}_h) \leftarrow \mathtt{ShareSelect}(\tilde{\mathcal{W}}, \mathcal{O}) \\ out &\leftarrow \mathsf{Sim}(x'|_{\mathcal{I}}, \mathcal{I}, \mathcal{I}', \mathcal{O}, \tilde{\mathcal{W}}) \end{split}$$

yields

$$\Pr[(|\mathcal{I}_1| > d) \lor \ldots \lor (|\mathcal{I}_h| > d)] \le \epsilon$$

$$out \equiv (\texttt{AssignWires}(G^{\tilde{\mathcal{F}}}, \tilde{\mathcal{W}}, x'), y'|_{\mathcal{O}})$$

with

$$y' \leftarrow G^{\tilde{\mathcal{F}}}(x')$$

.

$<sup>^{4}</sup>$  The same procedure should be used when analyzing replicated circuits for standalone GRPC.

Fourth, and similar to Section 3.3, we only check for side-channel security if the gadget is fault secure to keep the failure probabilities for probe simulation  $\epsilon_{\mathcal{I}'}$  and correctness  $\mu_{\mathcal{I}'}$  independent. For this, we again introduce a subset of fault combinations  $\mathcal{B}_{\mathcal{I}'} \subseteq \mathcal{F}^{\infty}$ , such that  $\mathcal{B}_{\mathcal{I}'}$  captures all fault combinations that, in combination with potential faults on the inputs with indices in  $\mathcal{I}'$ , lead to a gadget output that can be corrected, i.e.,  $\mathcal{B}_{\mathcal{I}'} = \{\tilde{\mathcal{F}} \in \mathcal{F}^{\infty} \mid \mathcal{L}_{\mathcal{I}',\tilde{\mathcal{F}}}(G) = 0\}$ . Note, that we define this set to be dependent on the tuple  $\mathcal{I}'$ . The corresponding distribution  $\mathbb{D}\mathcal{B}_{\mathcal{I}'}$  is defined as the scaled distribution  $\mathbb{D}\mathcal{F}^{\infty}$  conditioned on the event  $\mathcal{L}_{\mathcal{I}',\tilde{\mathcal{F}}}(G) = 0$ .

With this, we say that a gadget supports Known-Fault Random Combined Composability (RCC<sub>KF</sub>) if, for any tuple  $\mathcal{I}'$ , the gadget supports RRFC and RPCUF with negligible advantage for the adversary. To again compute a unified failure probability we chose the maximum combined failure probability (i.e., the probability that either RRFC fails or RPCUF fails under the condition that RRFC holds) over all tuples  $\mathcal{I}'$ .

**Definition 9 (Known-Fault Random Combined Composability).** A gadget  $G: ((\mathbb{F}_2^n)^s)^h \to ((\mathbb{F}_2^n)^s)^m$  is  $(d,k,\mathbb{D}\mathcal{W}^\infty,\mathbb{D}\mathcal{F}^\infty,\gamma)\text{-}RCC_{KF}$  if for all tuples of sets  $\mathcal{I}' = ((\mathcal{I}'_{i,j})_{i\in[s]})_{j\in[h]}$ , such that  $\forall i,j:\mathcal{I}'_{i,j}\subseteq[n]$  and  $|\mathcal{I}'_{i,j}|\leq k$ , there exists some  $\mu_{\mathcal{I}'},\epsilon_{\mathcal{I}'}\leq 1$  such that the gadget G is  $(\mathcal{I}',k,\mathbb{D}\mathcal{F}^\infty,\mu_{\mathcal{I}'})\text{-}RRFC$  and  $(\mathcal{I}',\mathbb{D}\mathcal{B}_{\mathcal{I}'},d,\mathbb{D}\mathcal{W}^\infty,\epsilon_{\mathcal{I}'})\text{-}RPCUF$  and it holds that  $\max_{\mathcal{I}'}\{\mu_{\mathcal{I}'}+(1-\mu_{\mathcal{I}'})\epsilon_{\mathcal{I}'}\}\leq \gamma$ .

Under this definition, we can arbitrarily compose any  $RCC_{KF}$  gadgets as long as each output of a gadget is only used once as input to another gadget. This restriction comes from the composition under probes (cf. Section 4.1). Then, under the assumption of mutually independent fault and probing distributions per gadget, the combined failure probability increases linearly in the number of gadgets in the circuit.

**Theorem 4.** Let C be a circuit constructed by composition of gadgets G that are  $(d, k, \mathbb{D}W_i^{\infty}, \mathbb{D}\mathcal{F}_i^{\infty}, \gamma_i)$ - $RCC_{KF}$ , for  $i \in \{1, ..., |C|\}$ , such that each output of  $G_i$  is used as input of at most one other gadget  $G_j$  or as output of C. Then, C is

$$(\prod_{i=1}^{|C|} \mathbb{D} \mathcal{W}_i^{\infty}, \prod_{i=1}^{|C|} \mathbb{D} \mathcal{F}_i^{\infty}, 1 - \prod_{i=1}^{|C|} (1 - \gamma_i)) - RCS_{KF}.$$

Intuitively, the proof follows the lines of the compositional statements for standalone probing and faulting. Specifically, we first go from inputs to outputs through the circuit to construct the respective tuples of potentially faulty inputs to each gadget to show composition under faults. Then, we go backward, i.e., from outputs to inputs, through the gadgets and use the fact that the set of faulty inputs is bounded in case of a fault combination that can be corrected to show random probing security under faults.

*Proof.* Let the faulty circuit be  $C^{\tilde{\mathcal{F}}} \leftarrow \mathtt{AssignFaultGates}(C, \prod_{i=1}^{|C|} \mathbb{D}\mathcal{F}_i^{\infty})$ , with  $\tilde{\mathcal{F}}$  the set of faults selected with  $\mathsf{Pr}_{\prod_i \mathbb{D}\mathcal{F}_i^{\infty}}[\tilde{\mathcal{F}}]$ . We can divide  $\tilde{\mathcal{F}}$  into |C| disjoint

fault sets  $\tilde{\mathcal{F}}_i \subseteq \tilde{\mathcal{F}}$  such that  $\tilde{\mathcal{F}}_i$  belongs to  $G_i$  and is selected with  $\Pr_{\mathbb{D}\mathcal{F}_i^{\infty}}[\tilde{\mathcal{F}}_i]$ . Further, let  $\tilde{\mathcal{W}}$  be the set of leaking wires of C selected with  $\Pr_{\prod_i \mathbb{D}\mathcal{W}_i^{\infty}}[\tilde{\mathcal{W}}]$ . We can divide  $\tilde{\mathcal{W}}$  into |C| disjoint parts  $\tilde{\mathcal{W}}_i \subseteq \tilde{\mathcal{W}}$ , each belonging to the gadget  $G_i$  such that each  $\tilde{\mathcal{W}}_i$  was selected with  $\Pr_{\mathbb{D}\mathcal{W}_i^{\infty}}[\tilde{\mathcal{W}}_i]$ .

Since each gadget  $G_i$  is  $(\mathcal{I}', k, \mathbb{D}\mathcal{F}^{\infty}, \mu_{\mathcal{I}'})$ -RRFC for all tuples  $\mathcal{I}'$  it follows with Theorem 3 that the circuit random fault secure with

$$\mu = 1 - \prod_{i=1}^{|C|} (1 - \mu_i). \tag{2}$$

Let  $\mathcal{B} = \{\tilde{\mathcal{F}} \mid \tilde{\mathcal{F}} = \bigcup_{i=1}^{|C|} \tilde{\mathcal{F}}_i, \forall \mathcal{I}'_{G_i} : \mathcal{L}_{\mathcal{I}'_{G_i}}, \tilde{\mathcal{F}}_i(G_i) = 0\}$  be the set of faults considered secure in Theorem 3, i.e., all fault combinations that can be corrected at the output of the respective gadgets. We denote by

$$\mathcal{B}_{\mathcal{I}'_{G_i}} = \{ \tilde{\mathcal{F}}_i \in \mathcal{F}^{\infty} \mid \mathcal{L}_{\mathcal{I}'_{G_i}, \tilde{\mathcal{F}}_i}(G_i) = 0 \} \subseteq \mathcal{B}$$

the set of fault combinations that can be corrected in a gadget  $G_i$  under faults in the input indices in  $\mathcal{I}'_{G_i}$ , with  $\forall j: |\mathcal{I}'_{G_i,j}| \leq k$ .

We now go backward through the circuit, starting with gadgets connected to the outputs of C, considering only faults  $\tilde{\mathcal{F}} \in \mathcal{B}$ . Let  $G_i$  be a gadget only connected to outputs of C. By RPCUF of  $G_i$ , we can construct a simulator  $\mathsf{Sim}_{G_i}$  that requires a subset of inputs (defined by the tuple  $\mathcal{I}_{G_i}$ ) for the simulation of the wires in  $\tilde{\mathcal{W}}_i$  under the faults  $\tilde{\mathcal{F}}_i$  and with faulty inputs with indices in  $\mathcal{I}'_{G_i}$ . Let the failure probability of  $\mathsf{Sim}_{G_i}$  be  $\epsilon_i$ .

We continue with the parent gadgets, i.e., gadgets that have outputs connected to the inputs of just handled gadgets and (potentially) outputs of the circuit. Let  $G_j$  be such a gadget. By RPCUF of  $G_j$ , we can construct a simulator  $\mathsf{Sim}_{G_j}$  that requires a subset of inputs (defined by the tuple  $\mathcal{I}_{G_j}$ ) for the simulation of the wires in  $\tilde{\mathcal{W}}_j$  and the output wires defined by the tuples  $\mathcal{I}_{G_i}$  of the child gadgets  $G_i$  under the faults  $\tilde{\mathcal{F}}_j$  and with faulty inputs with indices in  $\mathcal{I}'_{G_j}$ . In particular, each gadget output with index  $\ell$  is only used once in the circuit and we use the corresponding set  $\mathcal{I}_{G_i,\ell'}$  of the child gadget as  $\mathcal{O}_{G_j,\ell}$ . Again, we denote the failure probability of  $\mathsf{Sim}_{G_i}$  by  $\epsilon_j$ . We repeat this process until we reach the inputs of C.

Given this, we can construct the simulator  $\mathsf{Sim}$  for C by composition of the gadget simulators  $\mathsf{Sim}_{G_i}$ . The failure probability  $\epsilon$  of  $\mathsf{Sim}$  is the probability that at least one simulators  $\mathsf{Sim}_{G_i}$  fails, i.e.,

$$\epsilon = 1 - \prod_{i=1}^{|C|} (1 - \epsilon_i). \tag{3}$$

Therefore, with Equation 2 and 3 we have

$$\mu + (1 - \mu)\epsilon = 1 - \prod_{i=1}^{|C|} (1 - \mu_i) + \prod_{i=1}^{|C|} (1 - \mu_i)(1 - \prod_{i=1}^{|C|} (1 - \epsilon_i))$$

$$= 1 - \prod_{i=1}^{|C|} (1 - \mu_i)(1 - \epsilon_i)$$

$$\leq 1 - \prod_{i=1}^{|C|} (1 - \gamma_i),$$

with  $\gamma_i = \mu_i + (1 - \mu_i)\epsilon_i$  being the combined failure probability of each gadget  $G_i$ . It follows  $(\prod_{i=1}^{|C|} \mathbb{D} \mathcal{W}_i^{\infty}, \prod_{i=1}^{|C|} \mathbb{D} \mathcal{F}_i, 1 - \prod_{i=1}^{|C|} (1 - \gamma_i))$ -RCS<sub>KF</sub> of C.

Similar to Theorem 3, the above composition loses some tightness by only considering fault combinations that can be corrected after each gadget. While the set  $\mathcal{B}$  gets bigger, and hence  $\epsilon$  increases, when considering all fault combinations that can be corrected at the output of C, the overall  $\gamma$  gets smaller. The reason is that the respective fault combination is entirely captured in  $\mu$  of the above argument, however, it would only be partially captured (multiplied by some  $\epsilon \leq 1$ ) when considering the tighter definition of  $\mathcal{B}$ . Hence, the provided  $\gamma$  is indeed a upper bound of the combined failure probability.

Relation to Combined-Secure Composition. As with RFC, to the best of our knowledge, this is the first work discussing compositional properties in the context of the random combined model. However, again in the threshold model, several compositional notions were discussed. Most of them are a combination of compositional notions for probing and faulting, respectively. In this respect, (Strong) Non-Interference Non-Accumulation ((S)NINA) [20] (later refined to Combined (Strong) Non-Interference (C-(S)NI) [37]) is the combination of (S)NA with (S)NI, and Combined-Isolating Non-Interference (CINI) [27] is the combination of FINI and PINI, respectively. In the context of polynomial masking, Berndt et al. [12] coined the notion of fault-resilient (S)NI, which is the usual (S)NI notion that is invariant to fault injection. Our proposed compositional notation has some similarities with (S)NINA/C-(S)NI in that it is a combination of stand-alone faulting and probing composition and the underlying stand-alone notions relate to the respective stand-alone notions of (S)NA and (S)NI.

An interesting direction for future research into the composition in the random combined model is the notion of expansion (as considered in the random probing model) and the investigation of gadgets where the random probing security is invariant to faults.

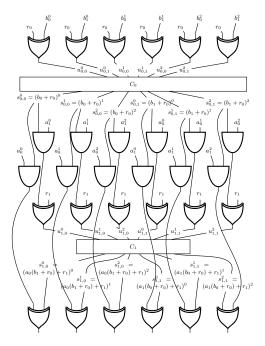

# 5 Automatic Verification of Protected Implementations

We implement the verification of the new notion of random combined security (and its composability variants) for cryptographic circuits by extending the verification tools VERICA [37] and IronMask [11]. At the state of the art, VERICA can be employed for combined hardware security verification considering the glitch-extended probing model [24] and the zeta fault-injection model [39], while IronMask is able to verify various (random, glitch-extended) probing security notions in an efficient way by relying on an algebraic characterization for specific gadgets.

In our work, we first aim to establish a common foundation for the practical verification of circuits under the new security models. Subsequently, we provide detailed insights into our extensions, denoted as VERICA<sup>+</sup> and IronMask<sup>+</sup>, enabling the verification of combined security properties in cryptographic circuits.

#### 5.1 Verification of the Generalized Security Models

We provide explicit formulas and practical verification choices for the computation of the simulation and correction failure probabilities in the general random probing model, the general random fault model, and the known-fault random combined security. These then serve as a basis for the extensions VERICA<sup>+</sup> and IronMask<sup>+</sup>.

General Random Probing Security. For the general random probing security (cf. Definition 1), we now assume independent and different leakage probabilities  $p_w$  for each wire w in W, to ease the computation for the verification. Then, the probability of a leaking wire combination  $\tilde{W}$  is the product of leakage probabilities of each wire  $w \in \tilde{W}$  times the product of  $(1 - p_{w'})$  of the remaining wires  $w' \in W \setminus \tilde{W}$ . Consequently, let  $\epsilon$  be the simulation failure probability such that

$$\epsilon = \sum_{i=1}^{|\mathcal{W}|} \sum_{\tilde{\mathcal{W}} \in \mathcal{W}_{\#i}^{\infty}} \prod_{w \in \tilde{\mathcal{W}}} p_w \prod_{w' \in \mathcal{W} \setminus \tilde{\mathcal{W}}} (1 - p_{w'}), \tag{4}$$

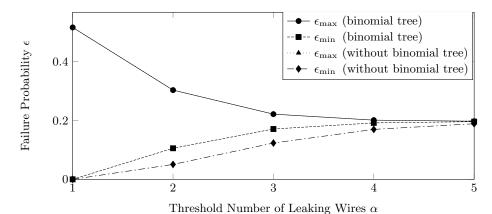

where  $W_{\#i}^{\infty} \subseteq W^{\infty}$  is the set of wire combinations of exactly i wires that lead to a simulation failure, i.e.,  $\tilde{W}_{\#i}^{\infty} = \{\tilde{W} \in W^{\infty} \mid |\tilde{W}| = i \text{ and } Sim(C, \tilde{W}) = \bot\}$ . The above equation generalizes the computation of the simulation failure probability in the random probing security from Belaïd et al. [10]. Precisely, Equation 4 is only equivalent to the latter if we consider that all wires are leaked with the same probability p.

Practically, a circuit may be too large for exhaustively checking all wire combinations. Therefore, VERICA<sup>+</sup> and IronMask<sup>+</sup> compute the outer sum of Equation 4 only up to a threshold  $\alpha$ , i.e., for  $i \in [1, \alpha]$ . For any combinations of more than  $\alpha$  wires, we can either consider that (1) they do not result in a simulation failure  $(\forall i \in ]\alpha, |\mathcal{W}|], \mathcal{W}_{\#_i}^{\infty} = \emptyset$ ) to obtain a lower bound  $\epsilon_{\min}$ , or (2) they all

lead to a simulation failure  $(\forall i \in ]\alpha, |\mathcal{W}|], \tilde{\mathcal{W}}_{\#i}^{\infty} = \{\tilde{\mathcal{W}} \in \mathcal{W}^{\infty} \mid |\tilde{\mathcal{W}}| = i\})$  to obtain an upper bound  $\epsilon_{\max}$ . Those lower and upper bound computations follow the same method used for the random probing security by Belaïd et al. in [10].

General Random Fault Security. For the general random fault model (cf. Definition 2), again for usability purposes of the verification process, we now assume independent and different fault probabilities  $q_f$  for each fault  $f = (g, \tau)$ . The probability of a fault combination  $\tilde{\mathcal{F}}$  is thus the product of the individual fault probabilities of the said combination times the product of  $(1-q_{f'})$  for all faults f' not present in it. Let  $\mu$  be the correction failure probability defined by

$$\mu = \sum_{i=1}^{|\mathcal{F}|} \sum_{\tilde{\mathcal{F}} \in \mathcal{F}_{\#i}^{\infty}} \prod_{f \in \tilde{\mathcal{F}}} q_f \prod_{f' \in \mathcal{F} \setminus \tilde{\mathcal{F}}} (1 - q_{f'}), \qquad (5)$$

where  $\mathcal{F}_{\#i}^{\infty} \subseteq \mathcal{F}^{\infty}$  is the set of fault combinations of exactly i faults that cannot

be corrected (such that  $\tilde{\mathcal{F}} \in \mathcal{F}_{\#i}^{\infty}$  iff  $\mathcal{L}_{\tilde{\mathcal{F}}}(C) = 1$ ). For practical reasons, Equation 5 is computed for up to  $\beta$  faults during security verification; the outer sum thus reduces to  $\sum_{i=1}^{\beta}$ . Similarly to the previous models, we derive the lower bound  $\mu_{\min}$  and the upper bound  $\mu_{\max}$  of  $\mu$  by assuming that any combination of more than  $\beta$  faults can be, respectively, corrected or not.

Known-Fault Random Combined Security. For simplicity, we restrict ourselves to RCS<sub>KF</sub> (cf. Definition 4) in the practical tool implementations. We then rely on the discussed security reduction for RCS<sub>UF</sub> (cf. Section 3.3) and leave room for a tighter RCS<sub>UF</sub> security analysis for future work. That said, three parameters are reported for  $RCS_{KF}$ :

- 1. the correction failure probability  $\mu$  as described in Equation 5,