# Comparing Hardware Performance of Fourteen Round Two SHA-3 Candidates Using FPGAs

Ekawat Homsirikamol

Marcin Rogawski

Kris Gaj

George Mason University

ehomsiri, mrogawsk, kgaj@gmu.edu

Last revised: December 21, 2010

# Contents

| 1        | Intr | oducti  | on and Motivation                                 | 2  |

|----------|------|---------|---------------------------------------------------|----|

| <b>2</b> | Met  | hodolo  | ogy                                               | 4  |

|          | 2.1  | Choice  | e of a Language, FPGA Devices, and Tools          | 4  |

|          | 2.2  |         | mance Metrics for FPGAs                           | 4  |

|          | 2.3  | Unifor  | m Interface                                       | 7  |

|          | 2.4  | Assum   | ptions and Simplifications                        | 9  |

|          | 2.5  | Optim   | ization Target                                    | 9  |

|          | 2.6  | Design  | Methodology                                       | 10 |

| 3        | Con  | nprehe  | nsive Designs of SHA-3 Candidates                 | 13 |

|          | 3.1  | _       | ons and Symbols                                   | 13 |

|          | 3.2  | Basic ( | Component Description                             | 15 |

|          |      | 3.2.1   | Multiplication by 2 in the Galois Field $GF(2^8)$ | 15 |

|          |      | 3.2.2   | Multiplication by n in the Galois Field $GF(2^8)$ | 15 |

|          |      | 3.2.3   | AES                                               | 16 |

|          | 3.3  | BLAK    | E                                                 | 19 |

|          |      | 3.3.1   | Block Diagram Description                         | 19 |

|          |      | 3.3.2   | 256 vs. 512 Variant Differences                   | 21 |

|          | 3.4  | Blue M  | Midnight Wish (BMW)                               | 24 |

|          |      | 3.4.1   | Block Diagram Description                         | 24 |

|          |      | 3.4.2   | 256 vs. 512 Variant Differences                   | 24 |

|          | 3.5  | CubeH   | Iash                                              | 26 |

|          |      | 3.5.1   | Block Diagram Description                         | 26 |

|          |      | 3.5.2   | 256 vs. 512 Variant Differences                   | 26 |

|          | 3.6  | ECHO    |                                                   | 29 |

|          |      | 3.6.1   | Block Diagram Description                         | 29 |

|          |      | 3.6.2   | 256 vs. 512 Variant Differences                   | 31 |

|          | 3.7  | Fugue   |                                                   | 33 |

|          |      | 3.7.1   | Block Diagram Description                         | 33 |

| Comparing Hardware Performance of Fourteen Round Two SHA-3 Candidates 3 | een Round Two SHA-3 Candidates 3 |

|-------------------------------------------------------------------------|----------------------------------|

|-------------------------------------------------------------------------|----------------------------------|

|   |      | 3.7.2 256 vs. 512 Variant Differences                                        | 35  |

|---|------|------------------------------------------------------------------------------|-----|

|   | 3.8  | Groestl                                                                      | 39  |

|   |      | 3.8.1 Block Diagram Description                                              | 39  |

|   |      | 3.8.2 256 vs. 512 Variant Differences                                        | 41  |

|   | 3.9  | Hamsi                                                                        | 43  |

|   |      | 3.9.1 Block Diagram Description                                              | 43  |

|   |      | 3.9.2 256 vs. 512 Variant Differences                                        | 45  |

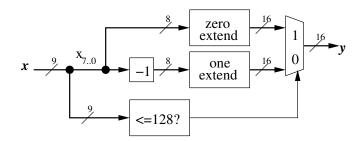

|   | 3.10 | JH                                                                           | 48  |

|   |      | 3.10.1 Block Diagram Description                                             | 48  |

|   |      | 3.10.2 256 vs. 512 Variant Differences                                       | 48  |

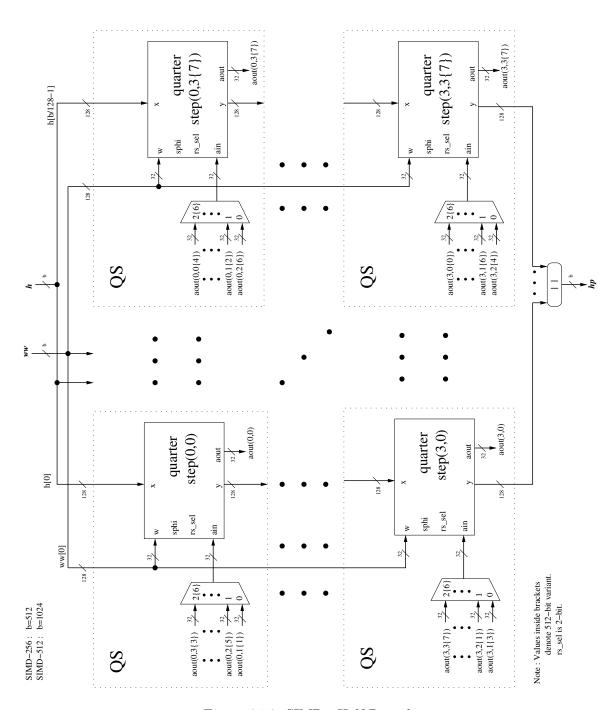

|   | 3.11 | Keccak                                                                       | 53  |

|   |      | 3.11.1 Block Diagram Description                                             | 53  |

|   |      | 3.11.2 256 vs. 512 Variant Differences                                       | 57  |

|   | 3.12 | Luffa                                                                        | 58  |

|   |      | 3.12.1 Block Diagram Description                                             | 58  |

|   |      | 3.12.2 256 vs. 512 Variant Differences                                       | 58  |

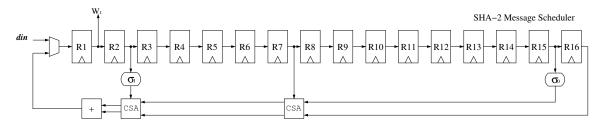

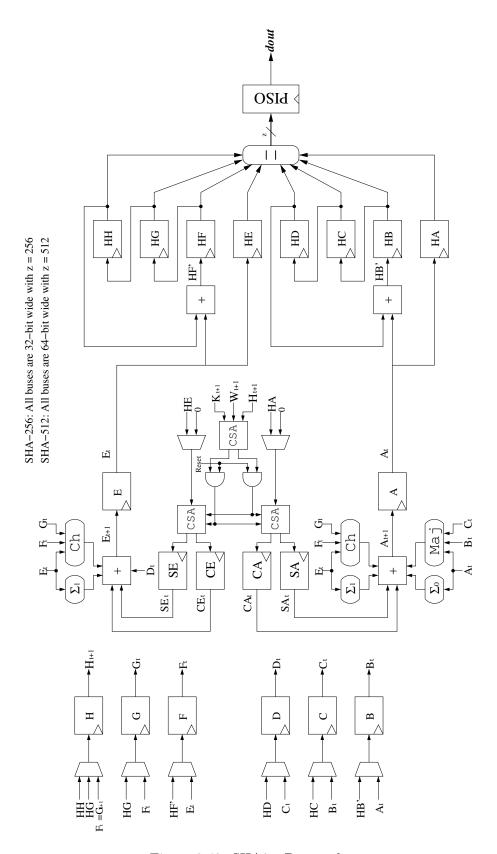

|   | 3.13 | SHA-2                                                                        | 65  |

|   |      | 3.13.1 Block Diagram Description                                             | 65  |

|   |      | 3.13.2 256 vs. 512 Variant Differences                                       | 65  |

|   | 3.14 | Shabal                                                                       | 67  |

|   |      | 3.14.1 Block Diagram Description                                             | 67  |

|   |      | 3.14.2 256 vs 512 Variant Differences                                        | 67  |

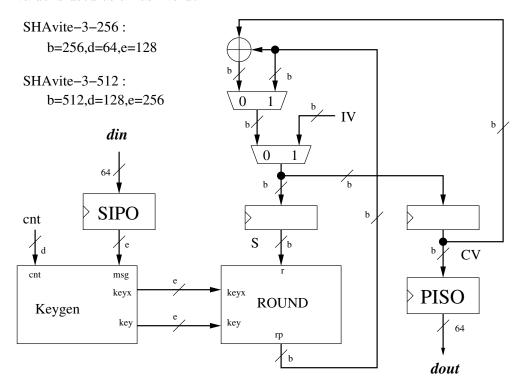

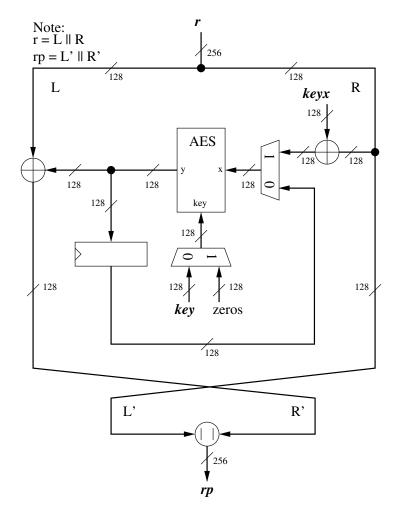

|   | 3.15 | SHAvite-3                                                                    | 69  |

|   |      | 3.15.1 Block Diagram Description                                             | 69  |

|   |      | 3.15.2 256 vs. 512 Variant Differences                                       | 70  |

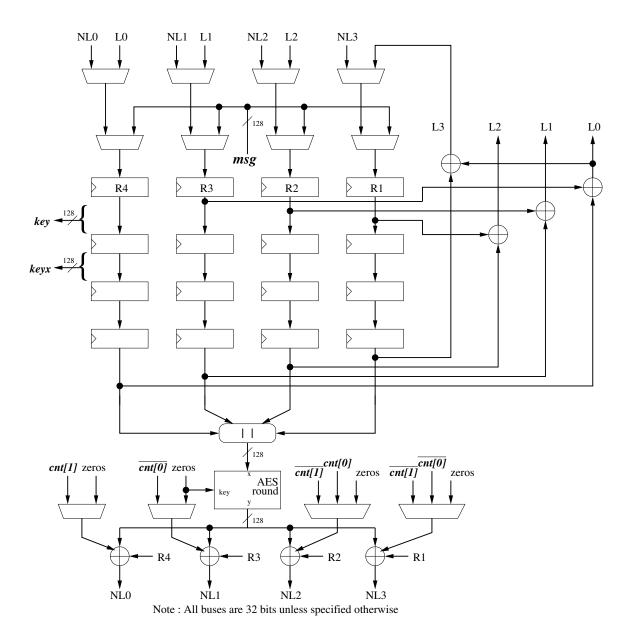

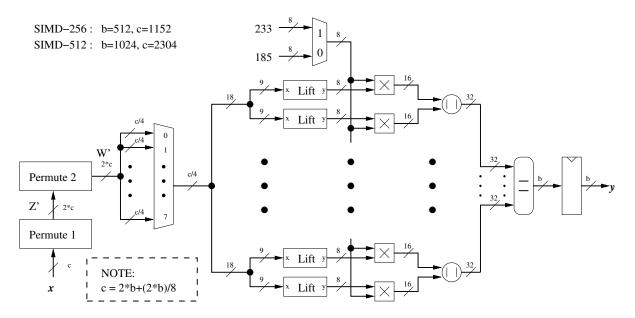

|   | 3.16 | SIMD                                                                         | 75  |

|   |      | 3.16.1 Block Diagram Description                                             | 75  |

|   |      | 3.16.2 256 vs. 512 Variant Differences                                       | 82  |

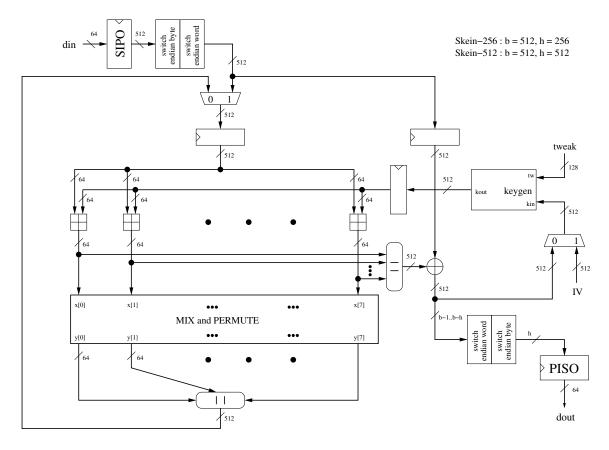

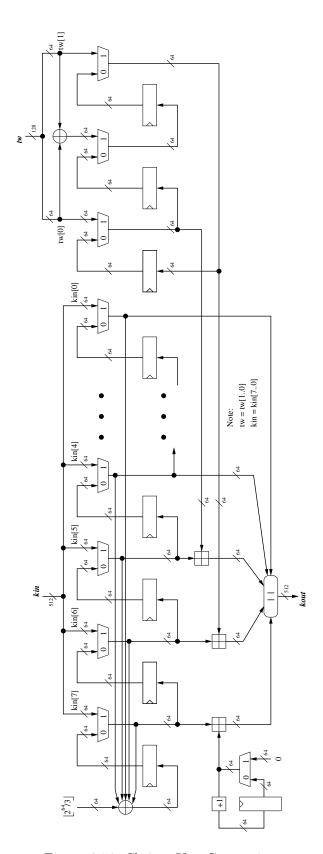

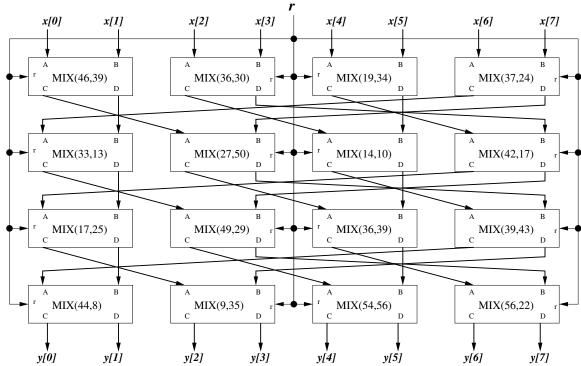

|   | 3.17 | Skein                                                                        | 86  |

|   | 0.1. | 3.17.1 Block Diagram Description                                             | 86  |

|   |      | 3.17.2 256 vs. 512 Variant Differences                                       | 87  |

|   |      | 511,12 200 (c) 512 (analy 2 instance)                                        | 0.  |

| 4 | Desi | ign Summary and Results                                                      | 90  |

|   | 4.1  | Design Summary                                                               | 90  |

|   | 4.2  | Relative Performance of the 512 and 256-bit Variants of the SHA-3 Candidates | 91  |

|   | 4.3  | Results                                                                      | 93  |

| 5 | Res  | ults from Other Groups                                                       | 108 |

|   | 5.1  | Best Results from Other Groups                                               | 108 |

|   | 5.2  | Best Results                                                                 | 109 |

| 6            | Conclusions and Future Work            | 114 |

|--------------|----------------------------------------|-----|

| $\mathbf{A}$ | Absolute Results for Ten FPGA Families | 116 |

E. Homsirikamol, M. Rogawski, and K. Gaj

4

#### Abstract

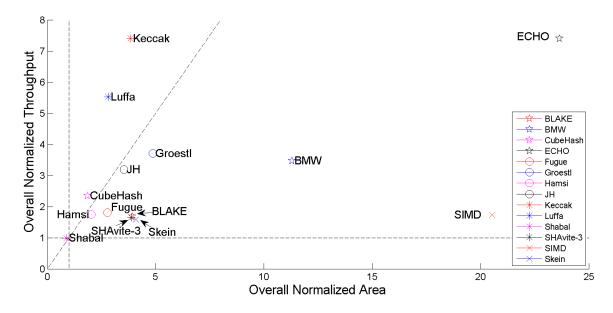

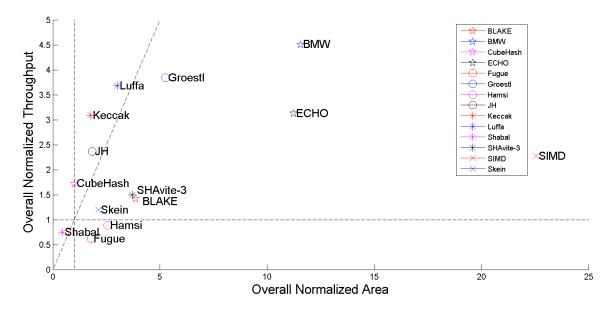

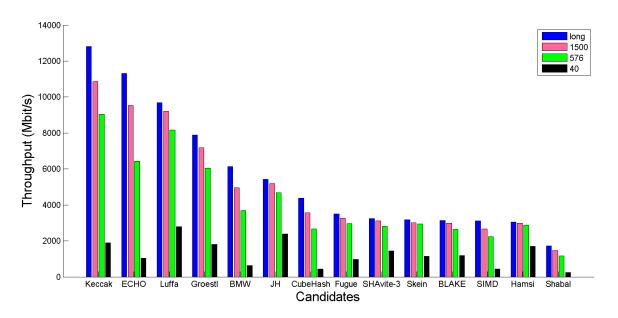

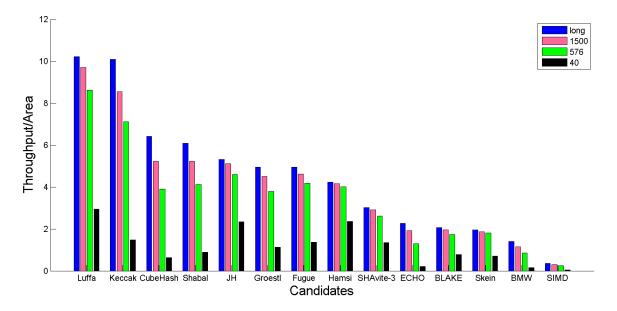

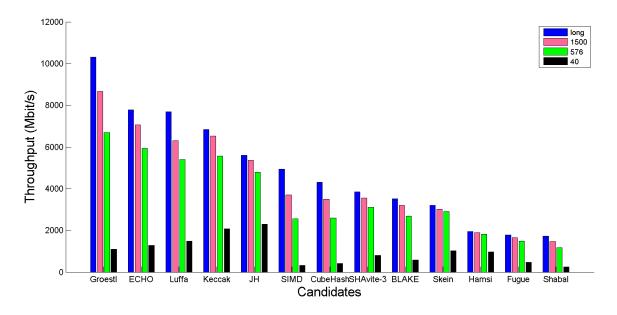

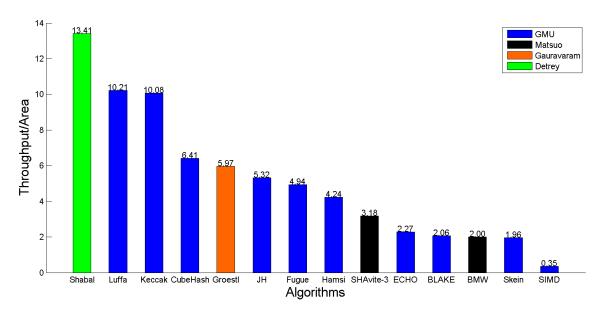

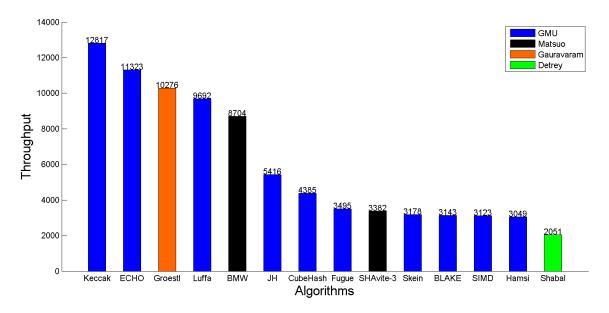

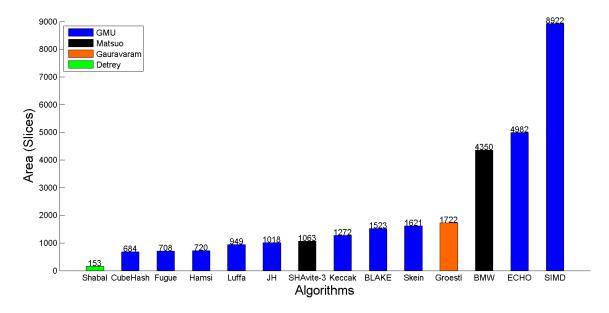

Performance in hardware has been demonstrated to be an important factor in the evaluation of candidates for cryptographic standards. Up to now, no consensus exists on how such an evaluation should be performed in order to make it fair, transparent, practical, and acceptable for the majority of the cryptographic community. In this report, we formulate a proposal for a fair and comprehensive evaluation methodology, and apply it to the comparison of hardware performance of 14 Round 2 SHA-3 candidates. The most important aspects of our methodology include the definition of clear performance metrics, the development of a uniform and practical interface, generation of multiple sets of results for several representative FPGA families from two major vendors, and the application of a simple procedure to convert multiple sets of results into a single ranking. The VHDL codes for 256 and 512-bit variants of all 14 SHA-3 Round 2 candidates and the old standard SHA-2 have been developed and thoroughly verified. These codes have been then used to evaluate the relative performance of all aforementioned algorithms using ten modern families of Field Programmable Gate Arrays (FPGAs) from two major vendors, Xilinx and Altera. All algorithms have been evaluated using four performance measures: the throughput to area ratio, throughput, area, and the execution time for short messages. Based on these results, the 14 Round 2 SHA-3 candidates have been divided into several groups depending on their overall performance in FPGAs.

# Chapter 1

## Introduction and Motivation

Starting from the Advanced Encryption Standard (AES) contest organized by NIST in 1997-2000 [1], open contests have become a method of choice for selecting cryptographic standards in the U.S. and over the world. The AES contest in the U.S. was followed by the NESSIE competition in Europe [2], CRYPTREC in Japan, and eSTREAM in Europe [3].

Four typical criteria taken into account in the evaluation of candidates are: security, performance in software, performance in hardware, and flexibility. While security is commonly recognized as the most important evaluation criterion, it is also a measure that is most difficult to evaluate and quantify, especially during a relatively short period of time reserved for the majority of contests. A typical outcome is that, after eliminating a fraction of candidates based on security flaws, a significant number of remaining candidates fail to demonstrate any easy to identify security weaknesses, and as a result are judged to have adequate security.

Performance in software and hardware are next in line to clearly differentiate among the candidates for a cryptographic standard. Interestingly, the differences among the cryptographic algorithms in terms of hardware performance seem to be particularly large, and often serve as a tiebreaker when other criteria fail to identify a clear winner. For example, in the AES contest, the difference in hardware speed between the two fastest final candidates (Serpent and Rijndael) and the slowest one (Mars) was by a factor of seven [1][4]; in the eSTREAM competition the spread of results among the eight top candidates qualified to the final round was by a factor of 500 in terms of speed (Trivium x64 vs. Pomaranch), and by a factor of 30 in terms of area (Grain v1 vs. Edon80) [5][6].

At this point, the focus of the attention of the entire cryptographic community is on the SHA-3 contest for a new hash function standard, organized by NIST [7][8]. The contest is now in its second round, with 14 candidates remaining in the competition. The evaluation is scheduled to continue until the second quarter of 2012.

In spite of the progress made during previous competitions, no clear and commonly

accepted methodology exists for comparing hardware performance of cryptographic algorithms [9]. The majority of the reported evaluations have been performed on an ad-hoc basis, and focused on one particular technology and one particular family of hardware devices. Other pitfalls included the lack of a uniform interface, performance metrics, and optimization criteria. These pitfalls are compounded by different skills of designers, using two different hardware description languages, and no clear way of compressing multiple results to a single ranking. In this paper, we address all the aforementioned issues, and propose a clear, fair, and comprehensive methodology for comparing hardware performance of SHA-3 candidates and any future algorithms competing to become a new cryptographic standard. Our methodology is based on the use of FPGA devices from various vendors. The advantages of using FPGAs for comparison include short development time, wide availability of tools, and a limited number of vendors dominating the market.

The hardware evaluation of SHA-3 candidates started shortly after announcing the specifications and reference software implementations of 51 algorithms submitted to the contest [7][8][10]. The majority of initial comparisons were limited to less than five candidates, and their results have been published at [10]. The more comprehensive efforts became feasible only after NISTs announcement of 14 candidates qualified to the second round of the competition in July 2009.

Since then, several comprehensive studies have been reported in the Cryptology ePrint Archive [11][12], at the CHES 2010 workshop [13][14], and during the Second SHA-3 Candidate Conference [15][16][17][18]. This report is an extension of our earlier papers presented at CHES 2010 and the SHA-3 Candidate Conference [13][16]. To our best knowledge, this is the first report that presents the detailed block diagrams of all 14 Round 2 SHA-3 Candidates, and a comprehensive set of results covering two major SHA-3 variants (SHA-3-256 and SHA-3-512) implemented using 10 FPGA families from two major vendors, Xilinx and Altera.

# Chapter 2

# Methodology

## 2.1 Choice of a Language, FPGA Devices, and Tools

Out of two major hardware description languages used in industry, VHDL and Verilog HDL, we choose VHDL. We believe that either of the two languages is perfectly suited for the implementation and comparison of SHA-3 candidates, as long as all candidates are described in the same language. Using two different languages to describe different candidates may introduce an undesired bias to the evaluation.

FPGA devices from two major vendors, Xilinx and Altera, dominate the market with about 90% of the market share. We therefore feel that it is appropriate to focus on FPGA devices from these two companies. In this study, we have chosen to use ten families of FPGA devices from Xilinx and Altera. These families include two major groups, those optimized for minimum cost (Spartan 3 from Xilinx, and Cyclone II, III, and IV from Altera) and those optimized for high performance (Virtex 4, 5, and 6 from Xilinx, and Stratix II, III, and IV from Altera). Within each family, we use devices with the highest speed grade, and the largest number of pins.

As CAD tools, we have selected tools developed by FPGA vendors themselves: Xilinx ISE Design Suite v. 12.3 (including Xilinx XST, used for synthesis) and Altera Quartus II v. 10.0 Subscription Edition Software.

#### 2.2 Performance Metrics for FPGAs

Choosing proper performance metrics for the implementation of hash functions (or any other cryptographic transformations) using FPGAs is a non-trivial task, and no clear consensus exists so far on how these metrics should be defined. Below we summarize our proposed approach, which we applied in our study.

#### Speed.

In order to characterize the speed of the hardware implementation of a hash function, we suggest using Throughput, understood as a throughput (number of input bits processed per unit of time) for long messages. To be exact, we define Throughput using the following formula:

$$Throughput = \frac{block\_size}{T \cdot (HTime(N+1) - HTime(N))}$$

(2.1)

where  $block\_size$  is a message block size, characteristic for each hash function, HTime(N) is a total number of clock cycles necessary to hash an N-block message, T is a clock period, different and characteristic for each hardware implementation of a specific hash function.

Throughput defined this way is typically independent of N (and thus the size of the message), as in all hash function architectures we investigated so far, the expression HTime(N+1) - HTime(N) is a constant that corresponds to the number of clock cycles between processing of two subsequent input blocks.

The effective throughput for short messages is always smaller, and is expressed by the formula

$$Throughput_{eff} = \frac{N \cdot block\_size}{T \cdot HTime(N)}$$

(2.2)

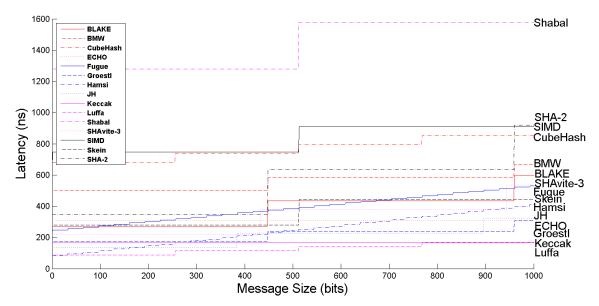

In this paper, we provide the exact formulas for HTime(N) for each SHA-3 candidate (see Table 4.2), and values of f = 1/T for each algorithm–FPGA device pair (see Tables 4.8 and 4.9). Therefore, we provide sufficient information to calculate and compare values of the effective throughputs for each specific message size, which may be of interest in a given application.

For short messages, it is more important to evaluate the total time required to process a message of a given size (rather than throughput). The size of the message can be chosen depending on the requirements of an application. For example, in the eBASH study of software implementations of hash functions, execution times for all sizes of messages, from 0-bytes (empty message) to 4096 bytes, are reported, and five specific sizes 8, 64, 576, 1536, and 4096 are featured in the tables [19]. The generic formulas we include in this paper (see Table 4.2) allow the calculation of the execution times for any message size.

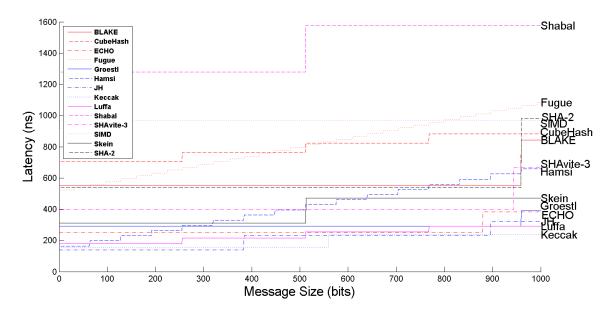

In order to characterize the capability of a given hash function implementation for processing short messages, we present in this study the comparison of execution times for messages ranging in size from 0 to 1000 bits before padding.

#### Resource Utilization/Area.

Resource utilization is particularly difficult to compare fairly in FPGAs, and is often a source of various evaluation pitfalls. First, the basic programmable block (such as CLB slice in Xilinx FPGAs) has a different structure and different capabilities for various FPGA families from different vendors. For example, in Virtex 5 and Virtex 6, a CLB slice includes

four 6-input Look-Up-Tables (LUTs); in Spartan 3 and Virtex 4, a CLB slice includes two 4-input LUTs. In Cyclone II, III, and IV, the basic programmable block is called Logic Element (LE); in Stratix II, III, and IV, the basic programmable component has a different structure and is called ALUT (Adaptive Look-Up Table). Taking this issue into account, we suggest avoiding any comparisons across family lines. Secondly, all modern FPGAs include multiple dedicated resources, which can be used to implement specific functionality. These resources include Block RAMs (BRAMs), multipliers (MULs), and DSP units in Xilinx FPGAs, and memory blocks, multipliers, and DSP units in Altera FPGAs. In order to implement a specific operation, some of these resources may be interchangable, but there is no clear conversion factor to express one resource in terms of the other.

Therefore, we suggest in the general case, treating resource utilization as a vector, with coordinates specific to a given FPGA family. For example,

$$Resource\_Utilization_{Spartan3} = (\#CLBslices, \#BRAMs, \#MULs)$$

(2.3)

$$Resource\_Utilization_{CycloneIII} = (\#LE, \#memory\_bits, \#MULs)$$

(2.4)

Taking into account that vectors cannot be easily compared to each other, we have decided to opt out of using any dedicated resources in the hash function implementations used for our comparison. Thus, all coordinates of our vectors, other than the first one have been forced (by choosing appropriate options of the synthesis and implementation tools) to be zero. This way, our resource utilization (further referred to as Area) is characterized using a single number, specific to the given family of FPGAs, namely the number of CLB slices (#CLBslices) for Xilinx FPGAs, the number of Logic Elements (#LE) for Cyclone families, and the number of Adaptive Look-Up Tables (#ALUT) in Stratix families.

Unfortunately, in four out of ten families, namely Cyclone II, Cyclone III, Cyclone IV, and Stratix II, the complete elimination of the use of memory blocks is very difficult, and might require a substantial redesign of the circuit. This is because these families have no concept of distributed memory, i.e., memory implemented inside of basic configurable building blocks of Altera FPGAs, such as Logic Elements or Adaptive Look-Up Tables. As a result, each time memory is inferred by the VHDL code, this memory is implemented using memory blocks characteristic for a given family (of the size of 4 kbits in Cyclone II, 9 kbits in Cyclone III and IV, and of the sizes of 512 bytes, 4 kbits, or 512 kbits in Stratix II). In our analysis below we neglect these memory requirements, as typically they amount to a relatively small percentage of memory resources available in target FPGAs.

The resource utilization vector in FPGAs (or even its simplified one-coordinate form, referred to as Area above) cannot be easily translated to an equivalent area or the number of transistors in ASICs. Any attempts to define a resource utilization unit that would apply to both technologies (such as an equivalent logic gate) have been mostly unsuccessful, and of limited value in practice. The only common denominator is cost, but unfortunately the prices of integrated circuits, and FPGAs in particular, are not commonly available, and are affected by multiple non-technical factors (including the number of units ordered, the relationship between companies, etc.)

## 2.3 Uniform Interface

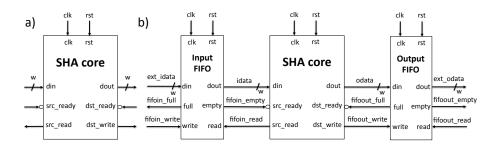

In order to remove any ambiguity in the definition of our hardware cores for SHA-3 candidates, and in order to make our implementations as practical as possible, we have developed an interface shown in Fig. 2.1a, and described below. In a typical scenario, the SHA core is assumed to be surrounded by two standard FIFO modules: Input FIFO and Output FIFO, as shown in Fig. 2.1b. In this configuration, SHA core is an active module, while a surrounding logic (FIFOs) is passive. Passive logic is much easier to implement, and in our case is composed of standard logic components, FIFOs, available in any major library of IP cores.

Each FIFO module generates signals empty and full, which indicate that the FIFO is empty and/or full, respectively. Each FIFO accepts control signals write and read, indicating that the FIFO is being written to and/or read from, respectively.

The aforementioned assumptions about the use of FIFOs as surrounding modules are very natural and easy to meet. For example, if a SHA core implemented on an FPGA communicates with an outside world using PCI, PCI-X, or PCIe interface, the implementations of these interfaces most likely already include Input and Output FIFOs, which can be directly connected to a SHA core. If a SHA core communicates with another core implemented on the same FPGA, then FIFOs are often used on the boundary between the two cores in order to accommodate for any differences between the rate of generating data by one core and the rate of accepting data by another core.

Additionally, the inputs and outputs of our proposed SHA core interface do not need to be necessarily generated/consumed by FIFOs. Any circuit that can support control signals src\_ready and src\_read can be used as a source of data. Any circuit that can support control signals dst\_ready and dst\_write can be used as a destination for data.

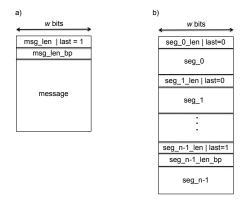

The exact format of an input to the SHA core, for the case of pre-padded messages, is shown in Fig. 2.2. Two scenarios of operation are supported. In the first scenario, the message bitlength after padding is known in advance and is smaller than  $2^w$ . In this scenario, shown in Fig. 2.2a, the first word of input represents message length after padding,

Figure 2.1: a) Input/output interface of a SHA core. b) A typical configuration of a SHA core connected to two surrounding FIFOs.

Figure 2.2: Format of input data for two different operation scenarios: a) with message bitlength known in advance, and b) with message bitlength unknown in advance. Notation: msg\_len – message length after padding, msg\_len\_bp – message length before padding, seg\_i\_len – segment i length after padding, seg\_i\_len\_bp – segment i length before padding, last – a one-bit flag denoting the last segment of the message (or one-segment message), "|" – bitwise OR.

expressed in bits. This word has the least significant bit, representing a flag called last, set to one. This word is followed by the message length before padding. This value is required by several SHA-3 algorithms using internal counters (such as BLAKE, ECHO, Shavite-3, and Skein), even if padding is done outside of the SHA core. These two control words are followed by all words of the message.

The second format, shown in Fig. 2.2b, is used when either message length is not known in advance, or it is greater than  $2^w$ . In this case, the message is processed in segments of data denoted as  $seg_0$ ,  $seg_1$ ,..., $seg_n$ . For the ease of processing data by the hash core, the size of the segments, from  $seg_0$  to  $seg_n$ -2 is required to be always an integer multiple of the block size b, and thus also of the word size w. The least significant bit of the segment length expressed in bits is thus naturally zero, and this bit, treated as a flag called last, can be used to differentiate between the last segment and all previous segments of the message. The last segment before padding can be of arbitrary length  $< 2^w$ . This segment is processed in the same way as the entire message in scenario a). This way there is no need for any additional signal to distinguish between these two scenarios. Scenario a) is a special case of scenario b). In case the SHA core supports padding, the protocol can be even simpler, as explained in [20].

Please note that scenario b) is very similar to the way data is processed by a typical software API for hash functions, such as [21]. The Update function of the software API corresponds to processing segments from seg\_0 to seg\_n-2. The function Final corresponds to the processing of the last segment of data, seg\_n-1.

## 2.4 Assumptions and Simplifications

Our study is performed using the following assumptions. Only the SHA-3 candidate variants with the 256-bit and the 512-bit outputs have been implemented and compared at this point. Other variants, treated either independently or as combinations of multiple variants (all-in-one hash cores) may be subjects of future comparisons.

Padding is assumed to be done outside of the hash cores (e.g., in software). All investigated hash functions have very similar padding schemes, which would lead to similar absolute area overhead if implemented as a part of the hardware core. The relative area penalty will be higher for cores with smaller area used for main processing. The complexity of the padding circuit will also depend on the assumptions regarding the smallest unit of a message (bit, byte, or word), which may be different for specific applications.

Only the primary mode of operation is supported for all functions. Special modes, such as tree hashing or MAC mode are not implemented (their implementation would actually work against the respective candidates, because of the area and speed penalty introduced by these extra features). There is also no support for providing salt specific to each message. The salt values are fixed to all zeros in all SHA-3 candidates supporting this special input (namely BLAKE, ECHO, SHAvite-3, and Skein).

## 2.5 Optimization Target

We believe that the choice of the primary optimization target is one of the most important decisions that needs to be made before the start of the comparison. The optimization target should drive the design process of every SHA-3 candidate, and it should also be used as a primary factor in ranking the obtained SHA-3 cores. The most common choices are: Maximum Throughput, Minimum Latency, Minimum Area, Throughput to Area Ratio, Product of Latency times Area, etc.

Our choice is the Throughput to Area Ratio, where Throughput is defined as Throughput for long messages, and Area is expressed in terms of the number of basic programmable logic blocks specific to a given FPGA family. This choice has multiple advantages. First, it is practical, as hardware cores are typically applied in situations, where the size of the processed data is significant and the speed of processing is essential. Otherwise, the input/output latency overhead associated with using a hardware accelerator dominates the total processing time, and the cost of using dedicated hardware (FPGA) is not justified. Optimizing for the best ratio provides a good balance between the speed and the cost of the solution.

Secondly, this optimization criterion is a very reliable guide throughout the entire design process. At every junction where the decisions must be made, starting from the choice of a high-level hardware architecture down to the choice of the particular FPGA tool options, this criterion facilitates the decision process, leaving very few possible paths for further investigation.

On the contrary, optimizing for Throughput alone, leads to highly unrolled hash function architectures, in which a relatively minor improvement in speed is associated with a major increase in the circuit area. In hash function cores, latency, defined as a delay between providing an input and obtaining the corresponding output, is a function of the input size. Since various sizes may be most common in specific applications, this parameter is not a well-defined optimization target. Finally, optimizing for area leads to highly sequential designs, resembling small general-purpose microprocessors, and the final product depends highly on the maximum amount of area (e.g., a particular FPGA device) assumed to be available.

## 2.6 Design Methodology

Our design of all 14 SHA-3 candidates followed an identical design methodology. Each SHA core is composed of the Datapath and the Controller. The Controller is implemented using three main Finite State Machines, working in parallel, and responsible for the Input, Main Processing, and the Output, respectively. As a result, each circuit can simultaneously perform the following three tasks: output hash value for the previous message, process a current block of data, and read the next block of data. The parameters of the interface are selected in such a way that the time necessary to process one block of data is always larger or equal to the time necessary to read the next block of data. This way, the processing of long streams of data can happen at full speed, without any visible input interface overhead. The finite state machines responsible for input and output are almost identical for all hash function candidates; the third state machine, responsible for main data processing, is based on a similar template. The similarity of all designs and reuse of common building blocks assures a high fairness of the comparison.

The design of the Datapath starts from the high level architecture. At this point, the most complex task that can be executed in an iterative fashion, with the minimum overhead associated with multiplexing inputs specific to a given iteration round, is identified. The proper choice of such a task is very important, as it determines both the number of clock cycles per block of the message and the circuit critical path (minimum clock period).

It should be stressed that the choice of the most complex task that can be executed in an iterative fashion should not follow blindly the specification of a function. In particular, quite often one round (or one step) from the description of the algorithm is not the most suitable component to be iterated in hardware. Either multiple rounds (steps) or fractions thereof may be more appropriate. In Table 2.1 we summarize our choices of the main iterative tasks of SHA-3 candidates. Each such task is implemented as combinational logic, surrounded by registers.

The next step is an efficient implementation of each combinational block within the DataPath. In Table 2.2, we summarize major operations of all SHA-3 candidates that require logic resources in hardware implementations. Fixed shifts, fixed rotations, and

Table 2.1: Main iterative tasks of the hardware architectures of SHA-3 candidates optimized for the maximum Throughput to Area ratio

| Function | Main Iterative Task           | Function  | Main Iterative Task     |

|----------|-------------------------------|-----------|-------------------------|

| BLAKE    | $G_{i}G_{i+3}$                | JH        | Round function $R_8$    |

| BMW      | entire function               | Keccak    | Round R                 |

| CubeHash | one round                     | Luffa     | The Step Function, Step |

| ECHO     | AES round/AES round/          | Shabal    | Two iterations          |

|          | BIG.SHIFTROWS, BIG.MIXCOLUMNS |           | of the main loop        |

| Fugue    | 2 subrounds                   | SHAvite-3 | AES round               |

|          | (ROR3, CMIX, SMIX)            |           |                         |

| Groestl  | Modified AES round            | SIMD      | 4 steps of the          |

|          |                               |           | compression function    |

| Hamsi    | Truncated Non-Linear          | Skein     | 4 rounds of             |

|          | Permutation P                 |           | Threefish-512           |

Table 2.2: Major operations of SHA-3 candidates (other than permutations, fixed shifts and fixed rotations). mADDn denotes a multioperand addition with n operands.

| Function  | NTT | Linear | S-box   | GF MUL       | MUL        | mADD   | ADD     | Boolean     |

|-----------|-----|--------|---------|--------------|------------|--------|---------|-------------|

|           |     | code   |         |              |            |        | /SUB    |             |

| BLAKE     |     |        |         |              |            | mADD3  | ADD     | XOR         |

| BMW       |     |        |         |              |            | mADD17 | ADD,SUB | XOR         |

| CubeHash  |     |        |         |              |            |        | ADD     | XOR         |

| ECHO      |     |        | AES 8x8 | x02, x03     |            |        |         | XOR         |

| Fugue     |     |        | AES 8x8 | x04x07       |            |        |         | XOR         |

| Groestl   |     |        | AES 8x8 | x02x05, 0x07 |            |        |         | XOR         |

| Hamsi     |     | LC     | Serpent |              |            |        |         | XOR         |

|           |     |        | 4x4     |              |            |        |         |             |

| JH        |     |        | 4x4     | x2, x5       |            |        |         | XOR         |

|           |     |        |         |              |            |        |         |             |

| Keccak    |     |        |         |              |            |        |         | NOT,AND,XOR |

| Luffa     |     |        | 4x4     | x02          |            |        |         | XOR         |

| Shabal    |     |        |         |              | x3, x5     |        | ADD,SUB | NOT,AND,XOR |

| SHAvite-3 |     |        | AES 8x8 | x02, x03     |            |        |         | NOT,XOR     |

| SIMD      | NTT |        |         |              | x185, x233 | mADD3  | ADD     | NOT,AND,OR  |

| Skein     |     |        |         |              |            |        | ADD     | XOR         |

| SHA-256   |     |        |         |              |            | mADD5  |         | NOT,AND,XOR |

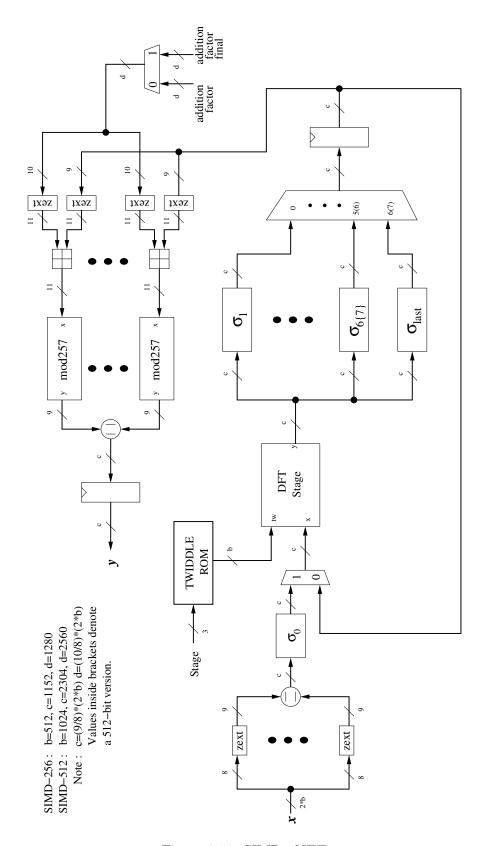

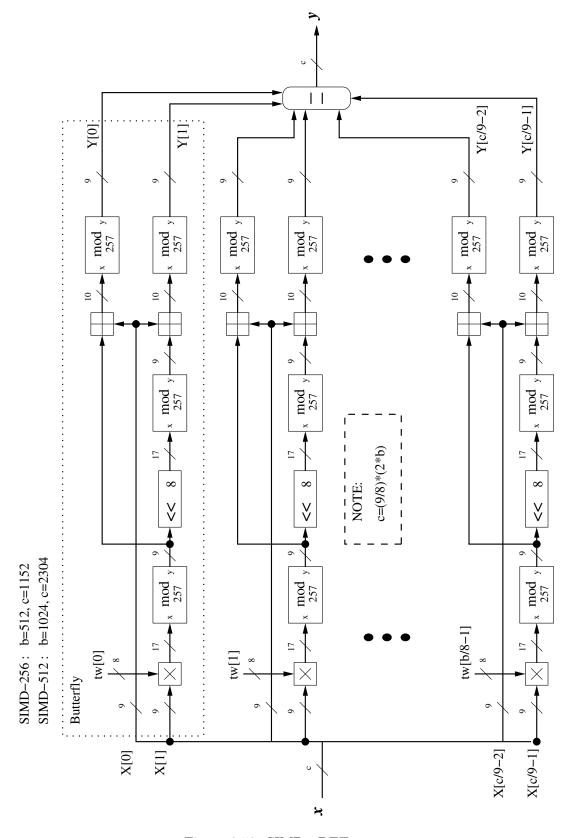

other more complex permutations are omitted because they appear in all candidates and require only routing resources (programmable interconnects). The most complex out of logic operations are the Number Theoretic Transform (NTT) [22] in SIMD, linear code (LC) [23] in Hamsi, basic operations of AES (8x8 AES S-box and multiplication by a constant in the Galois Field  $GF(2^8)$ ) in ECHO, Fugue, Groestl, and SHAvite-3; and multioperand additions in BLAKE, BMW, SIMD, and SHA-256.

For each of these operations we have implemented at least two alternative architectures. NTT was optimized by using a Fast Fourier Transform (FFT) [22]. In Hamsi, the linear code was implemented using both logic (matrix by vector multiplications in GF(4)), and using look-up tables. AES 8x8 S-boxes (SubBytes) were implemented using both look-up tables (stored in distributed memories), and using logic only (following method described in [24], Section 10.6.1.3). Multi-operand additions were implemented using the following four methods: carry save adders (CSA), tree of two operand adders, parallel counter, and a "+" in VHDL [25]). Finally, integer multiplications by 3 and 5 in Shabal have been replaced by a fixed shift and addition.

All optimized implementations of basic operations have been applied uniformly to all SHA-3 candidates. In case the initial testing did not provide a strong indication of superiority of one of the alternative methods, the entire hash function unit was implemented using two alternative versions of the basic operation code, and the results for a version with the better throughput to area ratio have been listed in the result tables.

All VHDL codes have been thoroughly verified using a universal testbench, capable of testing an arbitrary hash function core that follows interface described in Section 2.3 [26]. A special padding script was developed in Perl in order to pad messages included in the Known Answer Test (KAT) files distributed as a part of each candidates submission package. An output from the script follows a similar format as its input, but includes apart from padding bits also the lengths of the message segments, defined in Section 2.3, and shown schematically in Fig. 2.2b. The generation of a large number of results was facilitated by an open source tool ATHENa (Automated Tool for Hardware EvaluatioN) [26]. This benchmarking environment was also used to optimize requested synthesis and implementation frequencies and other tool options.

# Chapter 3

# Comprehensive Designs of SHA-3 Candidates

The designs of all 14 SHA-3 candidates followed the same basic design principle with the core separated into two main units, the Datapath and the Controller. Only the Datapath diagrams are provided in this chapter as the Controller can be derived from the Datapath and the specification of the function, and described using ASM charts. The full specification of each of the algorithms can be found in [27–41].

## 3.1 Notations and Symbols

Table 3.1 provides the notation and symbols that are being used throughout this chapter.

|                                                                                                 | Table 3.1: Notations and Symbols                                       |

|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| Word                                                                                            | A group of bits used in arithmetic and logic operations, typically     |

|                                                                                                 | of the size of 32 or 64 bits.                                          |

| Block                                                                                           | A group of words.                                                      |

| $\overline{X[i]}$                                                                               | Refers to an array position i in X.                                    |

| $\overline{X_i}$                                                                                | Refers to a bit position i in X.                                       |

| salt                                                                                            | Salt values are always assumed to be zero and as a result they are     |

|                                                                                                 | omitted from the diagrams.                                             |

| b                                                                                               | Block size in bits.                                                    |

| h                                                                                               | Hash value size in bits.                                               |

| W                                                                                               | Word size in bits.                                                     |

| IV                                                                                              | Initialization vector                                                  |

| SEXT                                                                                            | Sign extension.                                                        |

| ZEXT                                                                                            | Zero extension.                                                        |

| << <r< td=""><td>Rotation left by R positions. If R is a constant: fixed rotation;</td></r<>    | Rotation left by R positions. If R is a constant: fixed rotation;      |

|                                                                                                 | if R is a variable: variable rotation implemented using a barrel       |

|                                                                                                 | rotator.                                                               |

| >>>R                                                                                            | Rotation right by R positions. If R is a constant: fixed rotation;     |

|                                                                                                 | if R is a variable: variable rotation implemented using a barrel       |

|                                                                                                 | rotator.                                                               |

| < <s< td=""><td>Shift left by S positions. If S is a constant: fixed shift; if S is a</td></s<> | Shift left by S positions. If S is a constant: fixed shift; if S is a  |

|                                                                                                 | variable: variable shift implemented using a barrel shifter.           |

| >>S                                                                                             | Shift right by S positions. If S is a constant: fixed shift; if S is a |

|                                                                                                 | variable: variable shift implemented using a barrel shifter.           |

|                                                                                                 | Concatenation. By default, the buses concatenate back to the           |

|                                                                                                 | same arrangement as before the separation (split) occurs.              |

| SIPO                                                                                            |                                                                        |

| SIFO                                                                                            | Serial-in-parallel-out unit.                                           |

|                                                                                                 | -                                                                      |

| PISO                                                                                            | Danallal in garial aut weit                                            |

|                                                                                                 | Parallel-in-serial-out unit.                                           |

| switch<br>endian word                                                                           |                                                                        |

| elidiali word                                                                                   | Wordwise endianness switching.                                         |

| switch                                                                                          |                                                                        |

| endian byte                                                                                     | Bytewise endianness switching.                                         |

|                                                                                                 | 1 = 2 = 2 = 2 = 2 = 2 = 2 = 2 = 2 = 2 =                                |

## 3.2 Basic Component Description

This section describes implementations of selected basic components used in more than one algorithm. These components include multiplication by 2 in  $GF(2^8)$ , SubBytes, Mix-Columns, and AES Round.

## 3.2.1 Multiplication by 2 in the Galois Field GF(2<sup>8</sup>)

Figure 3.1: Basic: x2

## 3.2.2 Multiplication by n in the Galois Field $GF(2^8)$

Galois Field multiplication by n other than 2 is summarized in Table 3.2.

Table 3.2: Galois Field Multiplication by n

$$x3(X) = x2(X) \oplus X$$

$$x4(X) = x2(x2(X))$$

$$x5(X) = x4(X) \oplus X$$

$$x6(X) = x4(X) \oplus x2(X)$$

$$x7(X) = x4(X) \oplus x3(X)$$

## 3.2.3 AES

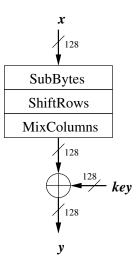

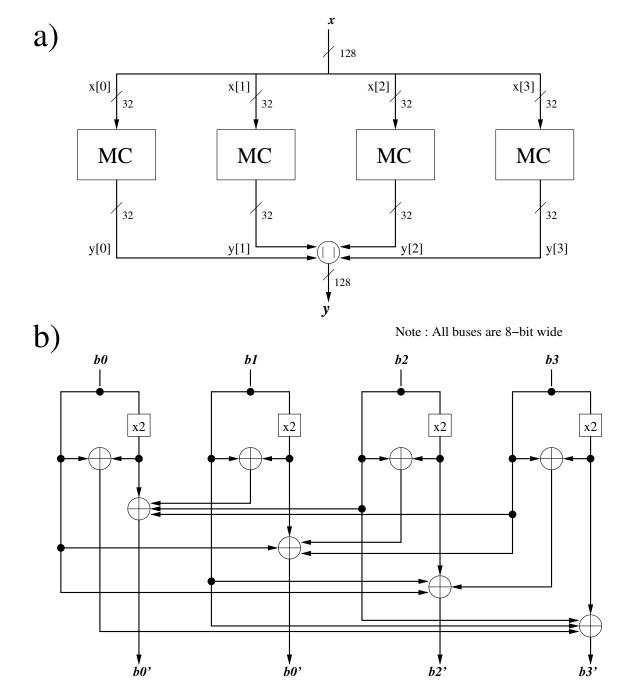

AES is a basic building block of many SHA-3 candidates. An AES round consists of three basic operations, SubBytes, ShiftRows, and MixColumns as shown in Figure 3.2. The SubBytes operation, shown in Figure 3.3, performs direct substitution on all bytes of its input. MixColumns performs multiplication of a constant 4x4 matrix by each word of its input. A word of AES contains 32 bits or 4 bytes. Hence, four instances of MC (MixColumn) are required to process the entire AES block of 128 bits, as shown in Figure 3.4. The SBOX and ShiftBytes operations of AES and their full specifications can be found in [42] and [43].

Figure 3.2: Basic: AES Round

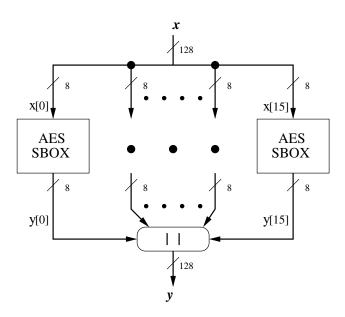

Figure 3.3: Basic : AES SubBytes

Figure 3.4: Basic : AES MixColumns. a) Applying MixColumns to the entire AES block, and b) MC: Applying MixColumns to a single word.

#### 3.3 BLAKE

## 3.3.1 Block Diagram Description

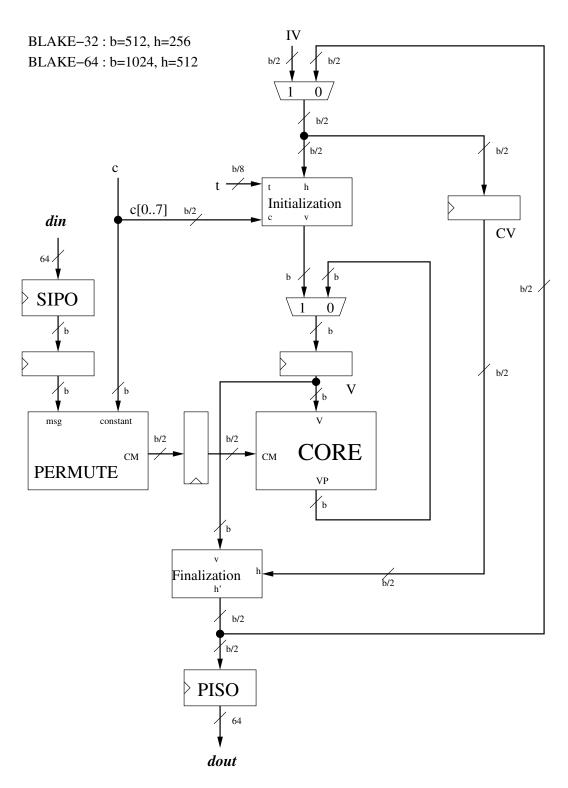

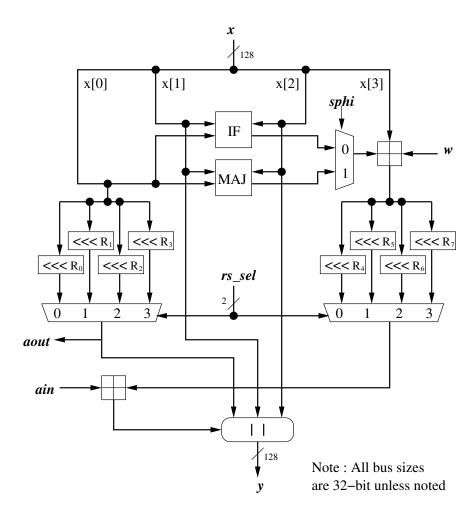

Figure 3.5 shows the datapath of BLAKE. In this design, the combinational CORE implements one half of the BLAKE's round [27]. Thus, two clock cycles are necessary to implement the full round. First, a message block is loaded into SIPO. Once done, the block is stored in a temporary register, used to hold the message block until this block is fully processed by the CORE. This temporary register allows the next message block to be loaded simultaneously into SIPO. The message block msg and the constant c are then applied as inputs to the function PERMUTE and the obtained output is passed to the design's CORE. Simultaneously, the chaining value, CV, is initialized with the the Initialization Vector, IV, and an input to the CORE, V, is initialized with the value dependent on the chaining value, the counter, t, and a lower half of the constant c. The initial value of V is mixed by the CORE with an output of the block PERMUTE, CM, for twenty clock cycles (10 rounds). Once this operation is completed, an additional clock cycle is required for finalization. The output of Finalization is used as the next chaining value, for intermediate message blocks, or as the final hash value for the last message block.

The Initialization unit performs the following function:

$$\begin{pmatrix} v[0] & v[1] & v[2] & v[3] \\ v[4] & v[5] & v[6] & v[7] \\ v[8] & v[9] & v[10] & v[11] \\ v[12] & v[13] & v[14] & v[15] \end{pmatrix} \longleftarrow \begin{pmatrix} h[0] & h[1] & h[2] & h[3] \\ h[4] & h[5] & h[6] & h[7] \\ c[0] & c[1] & c[2] & c[3] \\ t[0] \oplus c[4] & t[1] \oplus c[5] & c[6] & c[7] \end{pmatrix}.$$

The Finalization unit performs the following operation:

$$h'[0] \leftarrow h[0] \oplus v[0] \oplus v[8]$$

$$h'[1] \leftarrow h[1] \oplus v[1] \oplus v[9]$$

$$h'[2] \leftarrow h[2] \oplus v[2] \oplus v[10]$$

$$h'[3] \leftarrow h[3] \oplus v[3] \oplus v[11]$$

$$h'[4] \leftarrow h[4] \oplus v[4] \oplus v[12]$$

$$h'[5] \leftarrow h[5] \oplus v[5] \oplus v[13]$$

$$h'[6] \leftarrow h[6] \oplus v[6] \oplus v[14]$$

$$h'[7] \leftarrow h[7] \oplus v[7] \oplus v[15].$$

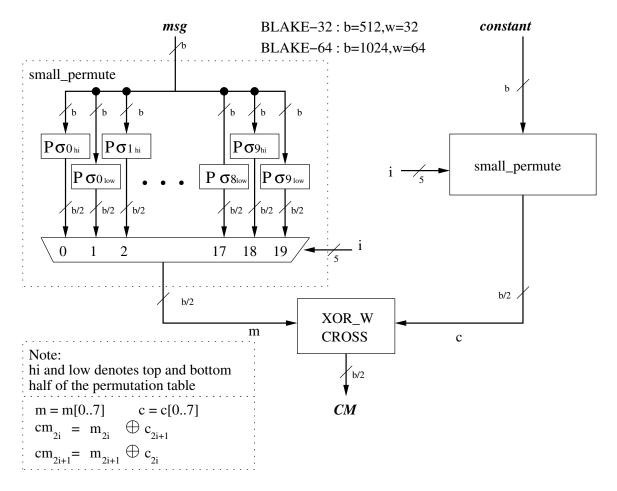

In Figure 3.6, an operation of the BLAKE's PERMUTE module is presented. A new value of the variable m is selected depending on the round number using a wide multiplexer preceded by constant permutations. A permutation table is shown in Table 3.3. The selection signal of the multiplexer cycles from 0 to 19 (and then again back to 0 for BLAKE-64) until all BLAKE's rounds are executed. Each output of the multiplexer is then mixed with the respective constant using the transformation  $XOR\_W\_CROSS$  (defined in the note to Fig. 3.6) and registered afterwards.

Figure 3.5: BLAKE : Datapath

| -                     | Table 3.3: BLAKE: Permutation Constants |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |

|-----------------------|-----------------------------------------|----|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|

|                       | hi                                      |    |    |    |    |    |    |    |    | low |    |    |    |    |    |    |

| $\overline{\sigma_0}$ | 0                                       | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9   | 10 | 11 | 12 | 13 | 14 | 15 |

| $\sigma_1$            | 14                                      | 10 | 4  | 8  | 9  | 15 | 13 | 6  | 1  | 12  | 0  | 2  | 11 | 7  | 5  | 3  |

| $\sigma_2$            | 11                                      | 8  | 12 | 0  | 5  | 2  | 15 | 13 | 10 | 14  | 3  | 6  | 7  | 1  | 9  | 4  |

| $\sigma_3$            | 7                                       | 9  | 3  | 1  | 13 | 12 | 11 | 14 | 2  | 6   | 5  | 10 | 4  | 0  | 15 | 8  |

| $\sigma_4$            | 9                                       | 0  | 5  | 7  | 2  | 4  | 10 | 15 | 14 | 1   | 11 | 12 | 6  | 8  | 3  | 13 |

| $\sigma_5$            | 2                                       | 12 | 6  | 10 | 0  | 11 | 8  | 3  | 4  | 13  | 7  | 5  | 15 | 14 | 1  | 9  |

| $\sigma_6$            | 12                                      | 5  | 1  | 15 | 14 | 13 | 4  | 10 | 0  | 7   | 6  | 3  | 9  | 2  | 8  | 11 |

| $\sigma_7$            | 13                                      | 11 | 7  | 14 | 12 | 1  | 3  | 9  | 5  | 0   | 15 | 4  | 8  | 6  | 2  | 10 |

| $\sigma_8$            | 6                                       | 15 | 14 | 9  | 11 | 3  | 0  | 8  | 12 | 2   | 13 | 7  | 1  | 4  | 10 | 5  |

| $\sigma_9$            | 10                                      | 2  | 8  | 4  | 7  | 6  | 1  | 5  | 15 | 11  | 9  | 14 | 3  | 12 | 13 | 0  |

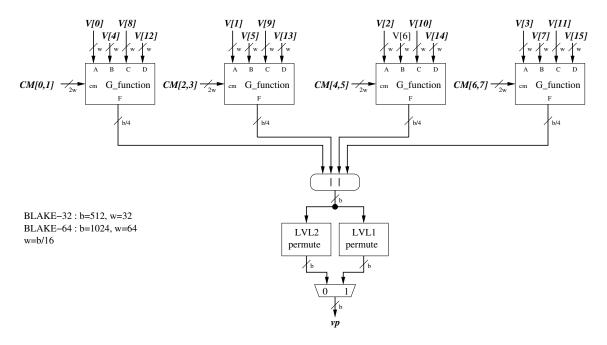

The CORE unit is shown in Figure 3.7 and represents one half of the BLAKE's round. As specified in [27], there are two levels of G functions and therefore a permutation between the first and the second half-round is required. This permutation is performed wordwise and is shown in Table 3.4. LVL2 transforms the state matrix (output of 4 parallel G functions) into a new matrix appropriate for the second half-round. LVL1 is a permutation inverse to LVL2.

| Table 3.4: Blake : Half Round Permutations<br>LVL2 (forward) |                          |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |

|--------------------------------------------------------------|--------------------------|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|

| input                                                        | 0                        | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 |

| output                                                       | 0                        | 1 | 2 | 3 | 5 | 6 | 7 | 4 | 10 | 11 | 8  | 9  | 15 | 12 | 13 | 14 |

|                                                              | LVL1 (inverse) input   0 |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |

| input                                                        | 0                        | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 |

| output                                                       | 0                        | 1 | 2 | 3 | 7 | 4 | 5 | 6 | 10 | 11 | 8  | 9  | 13 | 14 | 15 | 12 |

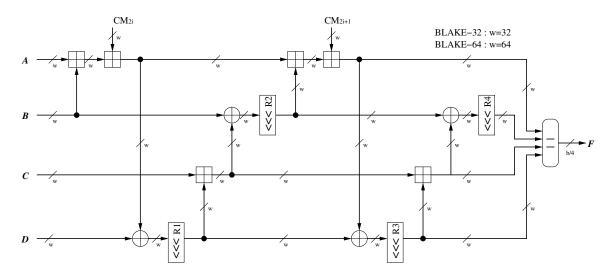

The G-function in the CORE unit is shown in Figure 3.8. Note that the XOR operations used to calculate input values  $CM_{2i}$  and  $CM_{2i+1}$ , which are normally depicted as a part of the G-function, are omitted in our design. These operations were placed as a part of the PERMUTE unit and therefore skipped here. R1, R2, R3 and R4 are rotating constants. The values of these constants are shown in Table 3.5

#### 3.3.2 256 vs. 512 Variant Differences

BLAKE-64 doubles the word size of BLAKE-32, thereby increasing the block size as well. Hence, the IV and the constant are changed from 512 bits to 1024 bits. These values can

Figure 3.6: BLAKE : PERMUTE

Table 3.5: BLAKE: Rotation Constants of BLAKE-32

| R1 | $\mathbf{R2}$ | R3 | <b>R4</b> |

|----|---------------|----|-----------|

| 16 | 12            | 8  | 7         |

be found in Section 2.2.1 of [27]. BLAKE-64 introduces also an increase in the number of mixing rounds from 10 to 14. As a result, the number of clock cycles required in our design for processing a single block of message increases from 21 to 29. The multiplexer selection signal in the PERMUTE unit loops back when the round number reaches 10. Hence, after reaching 19, this selection signal goes back to 0. Finally, the rotation constants are adjusted to reflect the increased word size. These values are described in Table 3.6.

Figure 3.7: BLAKE : CORE

Figure 3.8: BLAKE : G-function

Table 3.6: BLAKE: Rotating Constants of BLAKE-64

| R1 | R2 | R3 | R4 |  |  |

|----|----|----|----|--|--|

| 32 | 25 | 16 | 11 |  |  |

## 3.4 Blue Midnight Wish (BMW)

## 3.4.1 Block Diagram Description

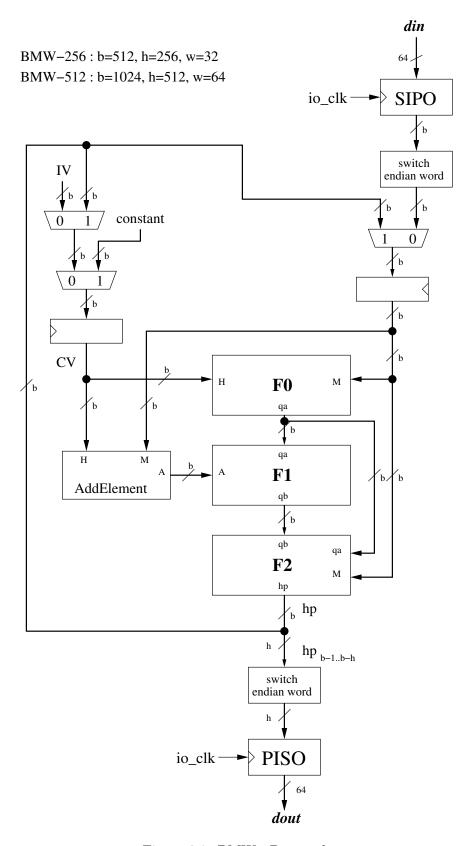

Our design for Blue Midnight Wish (BMW) hashes a block of data within one clock cycle. Since the number of clock cycles necessary to read a block of a message is greater than the number of clock cycles required to hash it, an additional clock signal is used in the circuit as shown in Figure 3.9. This faster clock (io\_clk) is used to drive the SIPO and PISO units, allowing them to read and write data at a faster rate than the operation of other units in the circuit. The rate of reading and writing is determined by the block size and the number of cycles required to process a block. Since only one clock cycle is used to process a message block, the frequency of io\_clk is block\_size/word\_size times higher than the main clock. This ratio is equal to 8 for BMW-256. BMW requires each message block to go through the endianness switching before the start of processing. A message block is then mixed with the chaining value in order to obtain the next chaining value. Once all blocks of the message are processed, a finalization round is initiated. Since there is no incoming message block, the chaining value and the input message block are replaced by the constant and the chaining value, respectively. The descriptions of F0, F1, F2 and AddElements and its associated logical operations can be found in Table 1.3 and Table 2.2-2.4 in [28].

#### 3.4.2 256 vs. 512 Variant Differences

BMW-512 increases the word size of BMW-256 from 32 to 64 bits. As a result, the block size is doubled as well. Since the block size increases, the number of clock cycles required to load a message block also increases for *io\_clk* from 8 cycles to 16 cycles. Furthermore, logic functions, specifically shifts and rotations, are adjusted to accommodate the increased word size. These changes are shown in Table 1.3 of [28]. All other operations remain the same.

Figure 3.9: BMW : Datapath

## 3.5 CubeHash

#### 3.5.1 Block Diagram Description

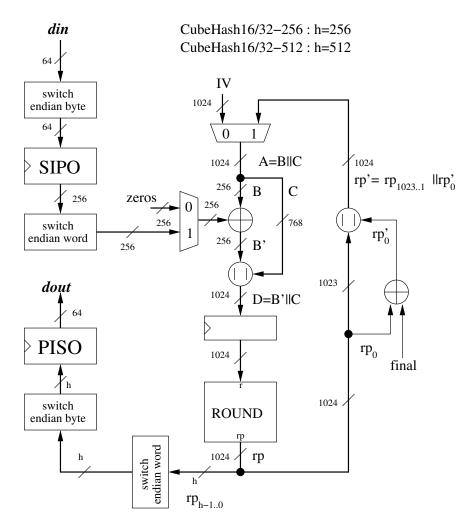

A straightforward iterative architecture is used in our design. The datapath of CubeHash is shown in Figure 3.10. Due to endianness issue, the input message is required to go through endianness switching twice. First, the bytewise endianness switching is applied, which is then followed by the wordwise endianness switching. A word of CubeHash consists of 32 bits.

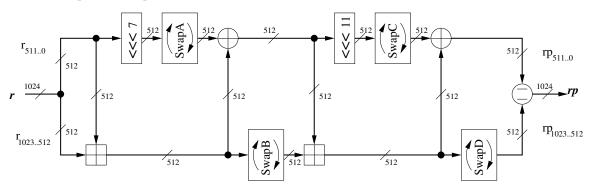

For each message, the chaining value A is initialized to IV. The 256 leftmost bits of the chaining value are xored with an input message block. The state is then transformed for 16 rounds. A round is described in Figure 3.11. Swaps used inside of the round are described in Figure 3.12. All operations inside the round are performed wordwise. This process repeats until all message blocks are processed. In the last round of the last message block, an integer one is xored with the position zero of the chaining value, rp, by activating the control signal final before the chaining value is inserted back into the state register. Then, the chaining value is transformed for 160 rounds to get the final hash value. The hash value is required to go through the endianness switching process again to reach the correct hash output.

#### 3.5.2 256 vs. 512 Variant Differences

Everything is the same for both variants with the exception of truncation size. CubeHash16/32-256 truncates the state to 256 bits to obtain the hash value, as opposed to CubeHash16/32-512 which truncates the state to 512 bits.

Figure 3.10: CubeHash : Datapath

Note: All operations are performed wordwise, with w=32

Figure 3.11: CubeHash : Round

Figure 3.12: CubeHash : Swaps

## 3.6 ECHO

#### 3.6.1 Block Diagram Description

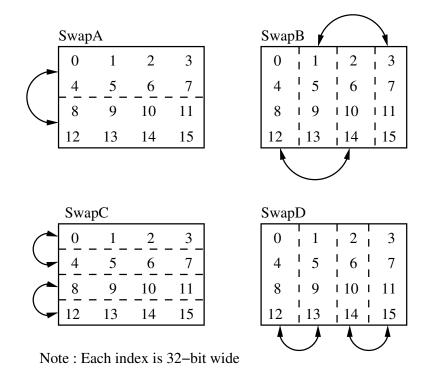

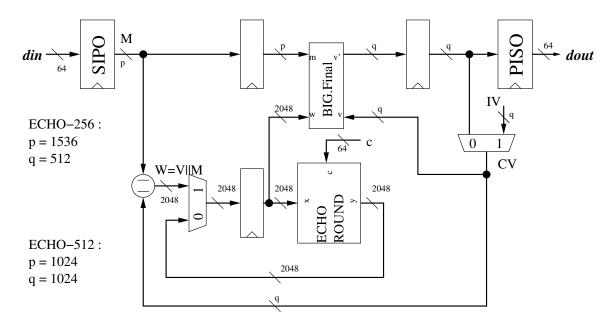

ECHO's top level datapath is shown in Figure 3.13. A message block is first concatenated with the chaining value to produce the state matrix. The state matrix is viewed as an array of 16 words with each word representing 128 bits. The state then goes through 8 iterations of the ECHO Round. Note that c represents the number of bits hashed so far. This value also includes bits of the currently processed block. Once the state matrix is thoroughly mixed, a new chaining value is computed from the state matrix by the BIG. Final unit. This operation is described as follows:

```

v'[0] \leftarrow v[0] \oplus m[0] \oplus m[4] \oplus m[8] \oplus w[0] \oplus w[4] \oplus w[8] \oplus w[12]

v'[1] \leftarrow v[1] \oplus m[1] \oplus m[5] \oplus m[9] \oplus w[1] \oplus w[5] \oplus w[9] \oplus w[13]

v'[2] \leftarrow v[2] \oplus m[2] \oplus m[6] \oplus m[10] \oplus w[2] \oplus w[6] \oplus w[10] \oplus w[14]

v'[3] \leftarrow v[3] \oplus m[3] \oplus m[7] \oplus m[11] \oplus w[3] \oplus w[7] \oplus w[11] \oplus w[15]

```

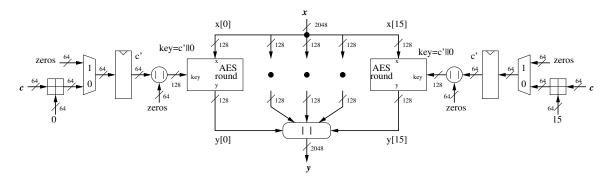

Figure 3.13: ECHO: Datapath

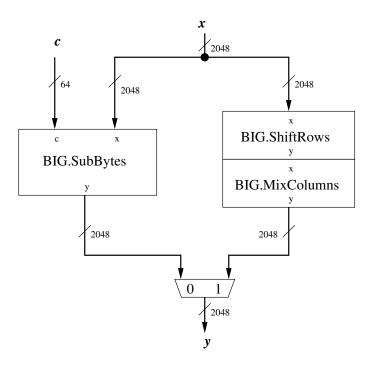

In Figure 3.14, operations inside of the ECHO round are shown. In our design, each ECHO round is executed in three clock cycles. BIG.SubBytes is performed in the first two clock cycles and BIG.ShiftRows and BIG.MixColumns in the third cycle. BigSubBytes operation is shown in Figure 3.15. The unit takes in the state matrix and the message length counter, c, and produces the next state. In the first clock cycle of the round

Figure 3.14: ECHO: Round

operation, the key is chosen to be the length counter plus the numbers between 0 and 15. These added values follow the word number. Hence, the fourteenth word gets the key as c + 14. In the next cycle, salt is selected as the key. Since in our implementation, salt is not used, zero is selected instead.

Figure 3.15: ECHO: BIG.SubBytes

Two operations are performed in the third cycle of a round. First, BIG.ShiftRows is performed. This operation is equivalent to the word permutation given in Table 3.7. Next,

BIG.MixColumns transforms the permuted state to obtain the final value of a round. In Figure 3.16, a diagram of BIG.MixColumns is shown. BIG.MixColumns separates the state into 4 blocks, each block containing 4 128-bit words. A byte of data from each word is selected to go through the AES MixColumns. All data is then combined together to produce the final state.

| Table 3.7: ECHO: BIG.ShiftRows |   |   |    |    |   |   |    |   |   |    |    |    |    |    |    |    |

|--------------------------------|---|---|----|----|---|---|----|---|---|----|----|----|----|----|----|----|

| Word                           | 0 | 1 | 2  | 3  | 4 | 5 | 6  | 7 | 8 | 9  | 10 | 11 | 12 | 13 | 14 | 15 |

| Permuted Word                  | 0 | 5 | 10 | 15 | 4 | 9 | 14 | 3 | 8 | 13 | 2  | 7  | 12 | 1  | 6  | 11 |

Figure 3.16: ECHO: BIG.MixColumns

#### 3.6.2 256 vs. 512 Variant Differences

ECHO-512 differs from ECHO-256 in its message block and chaining value sizes. The message block is reduced from 1536 bits to 1024. On the other hand, the chaining value is increased from 512 to 1024 bits. The number of rounds changes from 8 to 10. All other

operations, except BIG. Final, remain the same. The BIG. Final operation of ECHO-512 is described below:

$v'[0] \leftarrow v[0] \oplus m[0] \oplus w[0] \oplus w[8]$   $v'[1] \leftarrow v[1] \oplus m[1] \oplus w[1] \oplus w[9]$   $v'[2] \leftarrow v[2] \oplus m[2] \oplus w[2] \oplus w[10]$   $v'[3] \leftarrow v[3] \oplus m[3] \oplus w[3] \oplus w[11]$   $v'[4] \leftarrow v[4] \oplus m[4] \oplus w[4] \oplus w[12]$   $v'[5] \leftarrow v[5] \oplus m[5] \oplus w[5] \oplus w[13]$   $v'[6] \leftarrow v[6] \oplus m[6] \oplus w[6] \oplus w[14]$   $v'[7] \leftarrow v[7] \oplus m[7] \oplus w[7] \oplus w[15]$

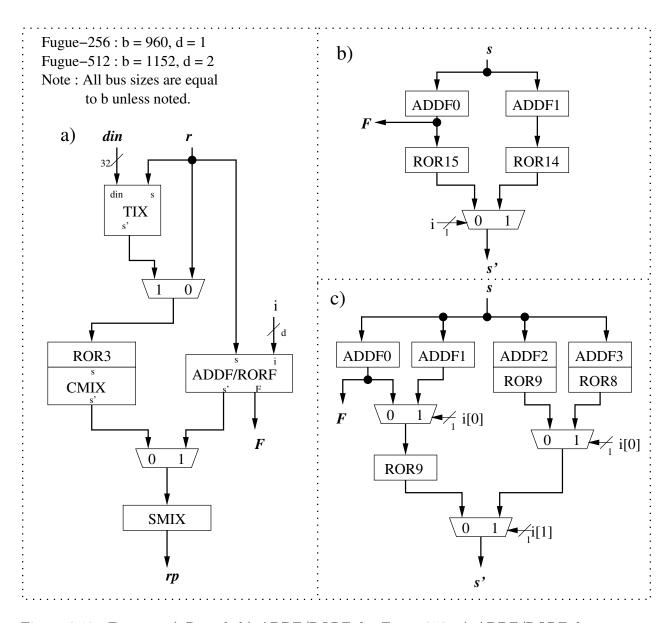

# 3.7 Fugue

## 3.7.1 Block Diagram Description

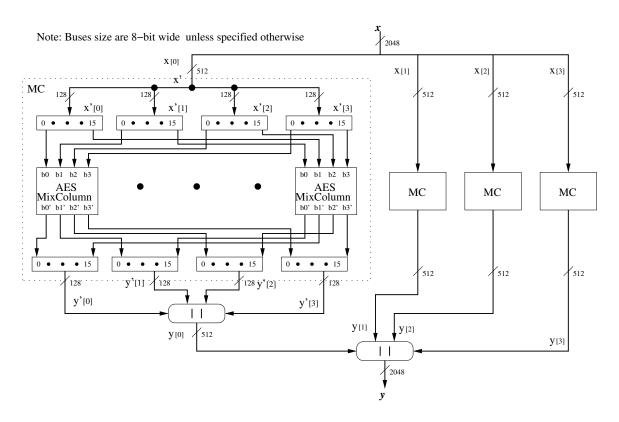

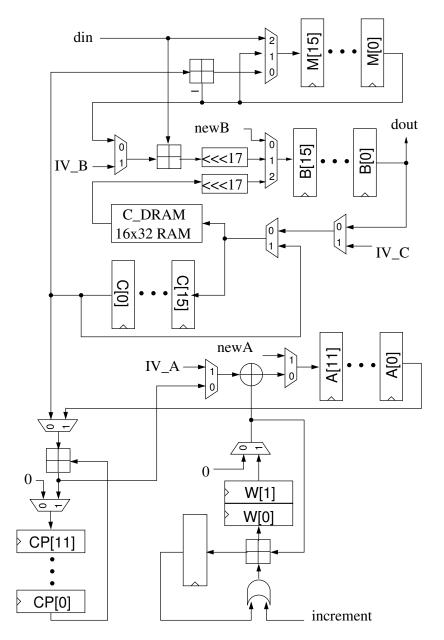

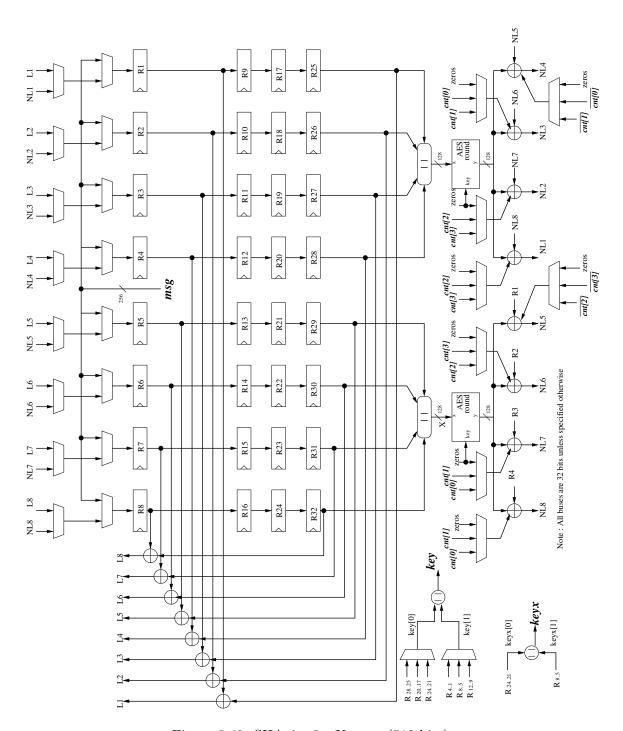

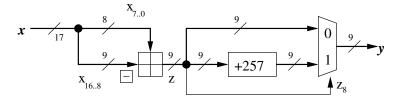

Fugue-256: b=960, h=256 size of 0s: b-h Fugue-512: b=1152, h=512 size of IV: h

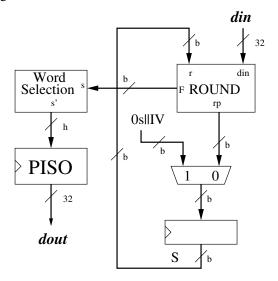

Figure 3.17: Fugue: Datapath

In Figure 3.17, the datapath of Fugue is shown. For every message, the state register is initialized to zeros concatenated with the h-bit IV. The state is viewed as a matrix of 4 by X bytes, where X is the number of columns in the matrix, dependent on the block size of Fugue. For Fugue-256, the block size is equal to 960 bits. Hence, the matrix have dimensions 4 x 30. The state is mixed with input message blocks through the ROUND unit. Once all message blocks are processed, the state goes through ADDF0 followed by Word Selection. For Fugue-256, Word Selection is described below:

$$S' = \frac{S[1..3] || S[4] ||}{S[15] || S[16..18]}.$$

A round of Fugue is shown in Figure 3.18. The path through the ROUND unit is selected based on the sequence of operations as described in Section 4.3.5 of Fugue-256 in [31]. TIX operates in parallel as follows:

$$S'[0] = din$$

$S'[1] = S[1] \oplus S[24]$

$S'[8] = S[8] \oplus din$

$S'[10] = S[10] \oplus S[0].$

Figure 3.18: Fugue : a) Round, b) ADDF/RORF for Fugue-256, c) ADDF/RORF for Fugue-512.

$\begin{array}{c|c} i & y \\ \hline 0 & S'[4] = S[4] \oplus S[0] \\ S'[15] = S[15] \oplus S[0] \\ \hline 1 & S'[4] = S[4] \oplus S[0] \\ S'[16] = S[16] \oplus S[0] \\ \end{array}$

Table 3.8: Fugue-256: ADDFi Operation

ROR3 and CMIX are performed consecutively. RORn sets

$$S'[i] = S[(i-n) \mod 30]$$

, for  $i = 0..29$  in Fugue-256, and  $S'[i] = S[(i-n) \mod 36]$ , for  $i = 0..35$  in Fugue-512.

As such, RORn can be considered as >>> (n\*32).

CMIX operates as follows:

$$S'[0] = S[0] \oplus S[4]$$

$S'[1] = S[1] \oplus S[5]$

$S'[2] = S[2] \oplus S[6]$

$S'[15] = S[15] \oplus S[4]$

$S'[16] = S[16] \oplus S[5]$

$S'[17] = S[17] \oplus S[6]$ .

The ADDF0 and ADDF1 operations are defined in Table 3.8.

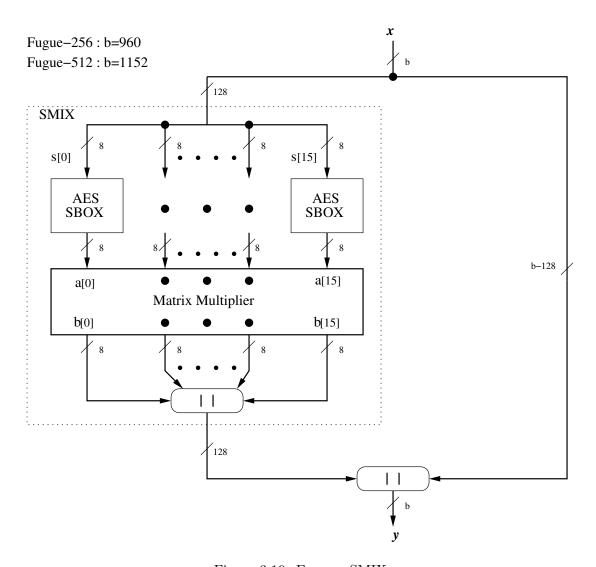

Finally, the SMIX operation is described in Figure 3.19. The SMIX operation affects only the first 128-bits of the state. These 128 bits are split into 16 bytes. These bytes are transformed using AES SBOX, and the resulting vector of 16 bytes is used as an input to the Matrix Multiplier. The Matrix Multiplier performs multiplication of a constant matrix by an input vector. The value of the constant matrix is shown in Table 3.9. Empty positions in this table correspond to the values zero. All multiplications are defined as multiplications in  $GF(2^8)$ .

#### 3.7.2 256 vs. 512 Variant Differences

Fugue-512 increases the state size to  $4 \times 36$  bytes, which is equivalent to 1152 bits. Additionally, TIX, CMIX, ADDF/RORF and Word Selection have been modified. TIX is now performed in parallel as follows:

|       | Table 3.9: Fugue: Matrix Multiplier Table |      |      |      |      |      |      |      |      |      |       |       |       |       |       |       |

|-------|-------------------------------------------|------|------|------|------|------|------|------|------|------|-------|-------|-------|-------|-------|-------|

|       | X[0]                                      | X[1] | X[2] | X[3] | X[4] | X[5] | X[6] | X[7] | X[8] | X[9] | X[10] | X[11] | X[12] | X[13] | X[14] | X[15] |

| Y[0]  | 1                                         | 4    | 7    | 1    | 1    |      |      |      | 1    |      |       |       | 1     |       |       |       |

| Y[1]  |                                           | 1    |      |      | 1    | 1    | 4    | 7    |      | 1    |       |       |       | 1     |       |       |

| Y[2]  |                                           |      | 1    |      |      |      | 1    |      | 7    | 1    | 1     | 4     |       |       | 1     |       |

| Y[3]  |                                           |      |      | 1    |      |      |      | 1    |      |      |       | 1     | 4     | 7     | 1     | 1     |

| Y[4]  |                                           |      |      |      |      | 4    | 7    | 1    | 1    |      |       |       | 1     |       |       |       |

| Y[5]  |                                           | 1    |      |      |      |      |      |      | 1    | 4    | 7     |       |       | 1     |       |       |

| Y[6]  |                                           |      | 1    |      |      |      | 1    |      |      |      |       |       | 7     | 1     |       | 4     |

| Y[7]  | 4                                         | 7    | 1    |      |      |      |      | 1    |      |      |       | 1     |       |       |       |       |

| Y[8]  |                                           |      |      |      | 7    |      |      |      | 6    | 4    | 7     | 1     | 7     |       |       |       |

| Y[9]  |                                           | 7    |      |      |      |      |      |      |      | 7    |       |       | 1     | 6     | 4     | 7     |

| Y[10] | 7                                         | 1    | 6    | 4    |      |      | 7    |      |      |      |       |       |       |       | 7     |       |

| Y[11] |                                           |      |      | 7    | 4    | 7    | 1    | 6    |      |      |       | 7     |       |       |       |       |

| Y[12] |                                           |      |      |      | 4    |      |      |      | 4    |      |       |       | 5     | 4     | 7     | 1     |

| Y[13] | 1                                         | 5    | 4    | 7    |      |      |      |      |      | 4    |       |       |       | 4     |       |       |

| Y[14] |                                           |      | 4    |      | 7    | 1    | 5    | 4    |      |      |       |       |       |       | 4     |       |

| Y[15] |                                           |      |      | 4    |      |      |      | 5    | 4    | 7    | 1     | 5     |       |       |       |       |

$$S'[0] = din$$

$$S'[1] = S[1] \oplus S[24]$$

$$S'[4] = S[4] \oplus S[27]$$

$$S'[7] = S[7] \oplus S[30]$$

$$S'[8] = S[8] \oplus din$$

$$S'[22] = S[22] \oplus S[0].$$

CMIX is now performed as follows:

$$S'[0] = S[0] \oplus S[4]$$

$$S'[1] = S[1] \oplus S[5]$$

$$S'[2] = S[2] \oplus S[6]$$

$$S'[18] = S[18] \oplus S[4]$$

$$S'[19] = S[19] \oplus S[5]$$

$$S'[20] = S[20] \oplus S[6].$$

The ADDFi operations, for i = 0..3 are defined in Table 3.10. Finally, Word Selection is performed as follows:

$$S' = \frac{S[1..3] \mid\mid S[4] \mid\mid S[9] \mid\mid S[10..12] \mid\mid}{S[18] \mid\mid S[19..21] \mid\mid S[27] \mid\mid S[10..12].}$$

Figure 3.19: Fugue : SMIX

Table 3.10: Fugue-512: ADDFi Operation

| i | у                                                                                                                          | i | у                                                                                                                        |

|---|----------------------------------------------------------------------------------------------------------------------------|---|--------------------------------------------------------------------------------------------------------------------------|

| 0 | $S'[4] = S[4] \oplus S[0]$<br>$S'[9] = S[9] \oplus S[0]$<br>$S'[18] = S[18] \oplus S[0]$<br>$S'[27] = S[27] \oplus S[0]$   | 2 | $S'[4] = S[4] \oplus S[0]$<br>$S'[9] = S[9] \oplus S[0]$<br>$S'[19] = S[19] \oplus S[0]$<br>$S'[27] = S[27] \oplus S[0]$ |

| 1 | $S'[4] = S[4] \oplus S[0]$<br>$S'[10] = S[10] \oplus S[0]$<br>$S'[18] = S[18] \oplus S[0]$<br>$S'[27] = S[27] \oplus S[0]$ | 3 | $S'[4] = S[4] \oplus S[0]$<br>$S'[9] = S[9] \oplus S[0]$<br>$S'[19] = S[19] \oplus S[0]$<br>$S'[28] = S[28] \oplus S[0]$ |

| Table 5.11. Groesu. Matrix Multiplier Table |      |      |      |      |      |      |      |      |  |  |  |  |

|---------------------------------------------|------|------|------|------|------|------|------|------|--|--|--|--|

|                                             | B[0] | B[1] | B[2] | B[3] | B[4] | B[5] | B[6] | B[7] |  |  |  |  |

| B'[0]                                       | 2    | 2    | 3    | 4    | 5    | 3    | 5    | 7    |  |  |  |  |

| B'[1]                                       | 7    | 2    | 2    | 3    | 4    | 5    | 3    | 5    |  |  |  |  |

| B'[2]                                       | 5    | 7    | 2    | 2    | 3    | 4    | 5    | 3    |  |  |  |  |

| B'[3]                                       | 3    | 5    | 7    | 2    | 2    | 3    | 4    | 5    |  |  |  |  |

| B'[4]                                       | 5    | 3    | 5    | 7    | 2    | 2    | 3    | 4    |  |  |  |  |

| B'[5]                                       | 4    | 5    | 3    | 5    | 7    | 2    | 2    | 3    |  |  |  |  |

| B'[6]                                       | 3    | 4    | 5    | 3    | 5    | 7    | 2    | 2    |  |  |  |  |

| B'[7]                                       | 2    | 3    | 4    | 5    | 3    | 5    | 7    | 2    |  |  |  |  |

Table 3.11: Groestl: Matrix Multiplier Table

## 3.8 Groestl

#### 3.8.1 Block Diagram Description

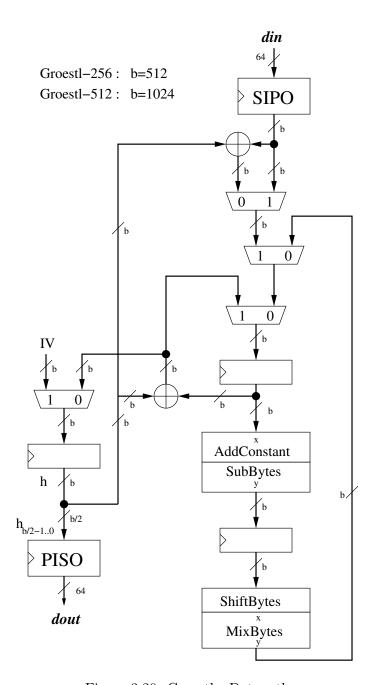

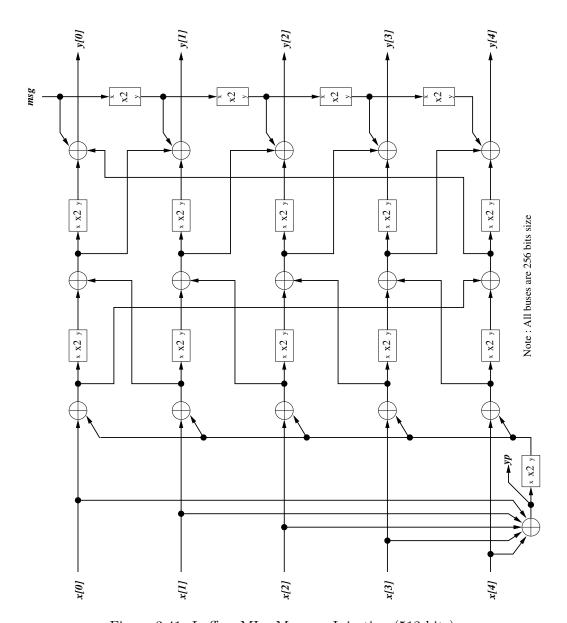

Groestl is an example of another SHA-3 candidate based on AES. A block diagram in Figure 3.20 shows datapath used in our design. As opposed to a straightforward design, a pipelined architecture is applied. The pipeline register is inserted between SubBytes and ShiftBytes operations. A message block is xored with an initialized chain register to create an input for the operation P in the first cycle of processing. In the next cycle, an input message is loaded directly to the state register as an input to the operation Q. At the same time when the first stage of the pipeline starts executing the operation Q, the second stage of the pipeline continues the execution of the operation P. The first stage of the pipeline consists of the ADD\_SUB unit. The second stage of the pipeline consists of the ShiftBytes and MixBytes units. A part of the function P is always performed one cycle ahead of the corresponding part of function Q. Finalization in this design takes two clock cycles. First, the chaining value is xored with the final value of P, while Q is being still processed. In the subsequent cycle the final result of Q is mixed with the chaining value as well. The entire process is repeated until all blocks of a message are thoroughly mixed. Finally, a hash value is taken from the bottom half of the chaining value.

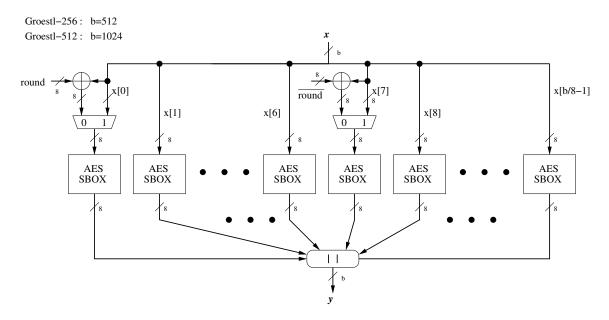

Figure 3.21, describes how the AddConstant and SubBytes are performed in our design. A round number is xored with the first byte of a message in the P operation. In the Q operation, a complemented round number is xored into the 8th byte. After that, all bytes go through the SBOX of AES.

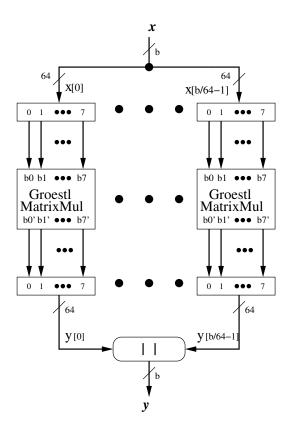

ShiftBytes operation is performed by rotating all bytes in row i to the right by  $\sigma_i$ , where  $\sigma$  is given as  $\sigma = [0, 1, 2, 3, 4, 5, 6, 7]$ . Figure 3.22 describes MixBytes operation. The MixBytes operation splits an input into b/64 64-bit words. Each word becomes an input into Groestl matrix multiplication. The constant matrix multiplication table used in Groestl is given in Table 3.11. All operations are performed in  $GF(2^8)$ , the same as in AES, as shown in Table 3.2.

Figure 3.20: Groestl : Datapath

Figure 3.21: Groestl: AddConstant and SubBytes

#### 3.8.2 256 vs. 512 Variant Differences

In Groestl-512 the block size is doubled. This means that the state size is increased by a factor of two as well. All basic operations of Groestl remain the same with the exception of ShiftRows. The ShiftRows rotation constants for each row are now changed to  $\sigma = [0, 1, 2, 3, 4, 5, 6, 11]$ . Finally, the number of rounds for Groestl-512 is increased to 14.

Figure 3.22: Groestl : MixBytes

#### 3.9 Hamsi

### 3.9.1 Block Diagram Description

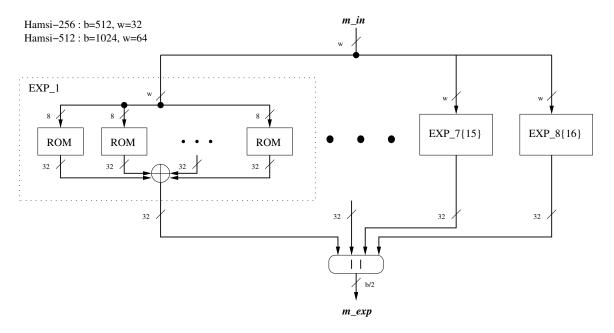

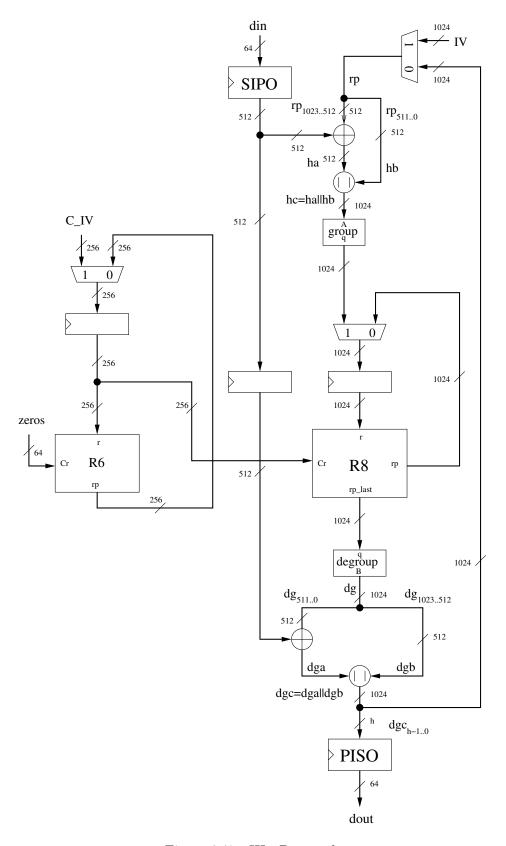

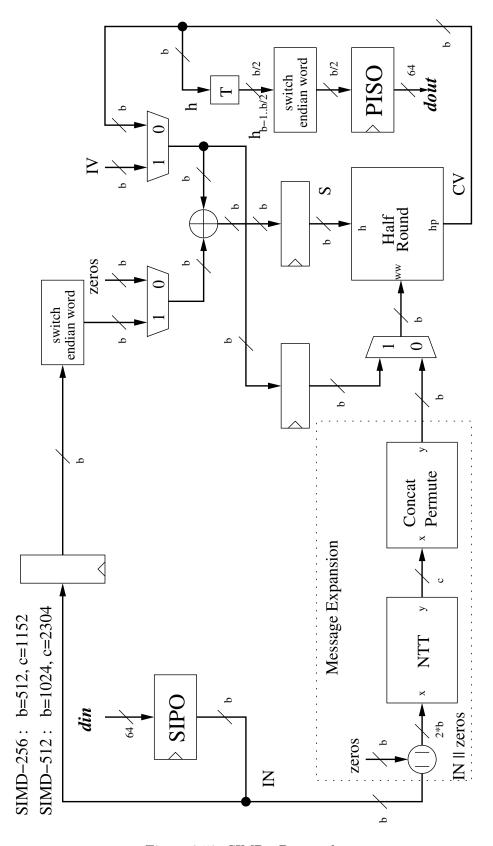

The datapath of Hamsi is shown in Figure 3.23. For every message block, an expanded message is concatenated with the chaining value to form a state. This state is viewed as an array of 32-bit words. The state is transformed through P or  $P_f$  rounds, using ACC, Substitution Layer and Diffusion Layer in each round. For Hamsi-256, P and  $P_f$  are equal to 3 and 8, respectively.  $P_f$  is selected as a number of rounds during processing of the last block of a message. After completing all rounds, the state is truncated and xored with the previous chaining value to form a new one.

In Figure 3.24, Message Expansion is shown. Message Expansion expands an input word of the size of w bits to an output of the size of half of the block size b/2. Each word is split into an array of bytes. Each byte becomes an input to a ROM-based look-up table, which produces a 32-bit output. The outputs from w/8 neighboring look-up tables are xored together to produce a portion of the overall output of the Message Expansion. All ROMs contain different dataset values, which can be obtained from a reference software implementation included in the submission package of [33].

Concatenation is performed as follows:

$$y = m[0..1]||c[0..3]||m[2..5]||c[4..7]||m[6..7]$$

ACC refers to Addition of Constants and Counter step. This step can be described by the following sequence of operations:

$$s'[1] = s[1] \oplus \alpha[1] \oplus c$$

$$s'[i] = s[i] \oplus \alpha[i]$$

for  $i$ =0, 2..15.

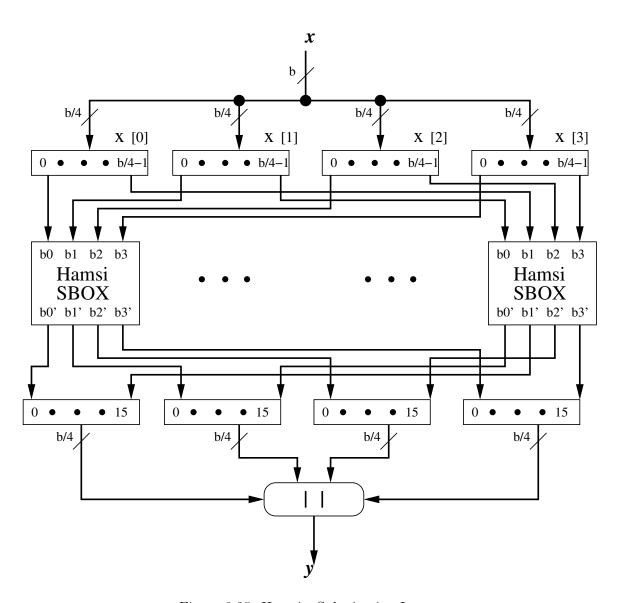

Substitution Layer is shown in Figure 3.25. An input is split into four equal blocks. Then the corresponding bits of each block form an input to the Hamsi SBOX. This SBOX is defined in Table 3.12.

| Table 3.12: Hamsi: SBOX |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|-------------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| X                       | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | A | В | С | D | Е | F |

| s[X]                    | 8 | 6 | 7 | 9 | 3 | С | A | F | D | 1 | Е | 4 | 0 | В | 5 | 2 |

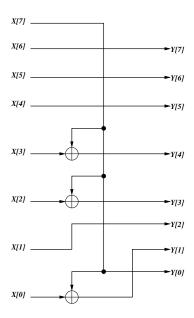

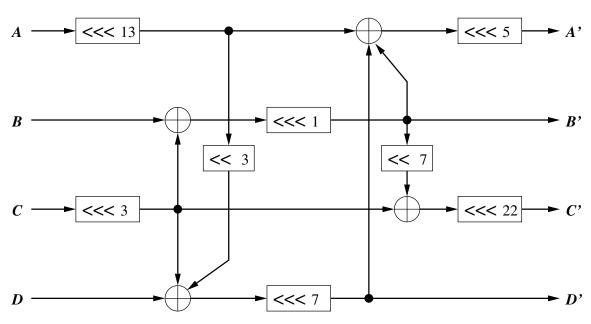

The Diffusion Layer is based on the logic function L, shown in 3.26. This function performs the following sequence of operations:

$$\begin{aligned} &(s[0], s[5], s[10], s[15]) = L(s[0], s[5], s[10], s[15]) \\ &(s[1], s[6], s[11], s[12]) = L(s[1], s[6], s[11], s[12]) \\ &(s[2], s[7], s[8], s[13]) = L(s[2], s[7], s[8], s[13]) \\ &(s[3], s[4], s[9], s[14]) = L(s[3], s[4], s[9], s[14]) \end{aligned}$$

Hamsi-256: b=512,w=32

Hamsi-512: b=1024,w=64 din IV b/2 b/2 PISO b/2 m\_in dout Message b/2 Expansion m\_exp b/2 b/2 Truncation Concatenation Ωf ACC b Substitution Layer

Figure 3.23: Hamsi : Datapath

Diffusion Layer

b .

Figure 3.24: Hamsi: Message Expansion

Finally, Truncation is performed as follows:

$$y = s[0..3] \mid\mid s[8..11]$$

#### 3.9.2 256 vs. 512 Variant Differences

An input to Hamsi-512 is increased to 64 bits. As a result, the size of ROMs used in the Message Expansion unit is increased as well. Similar to Hamsi-256, the data to populate these ROM-based look-up tables can be found in the reference software implementation. The rest of the operations remain largely the same with the following exceptions: Concatenation, Addition of Constants and Counter, Diffusion Layer, and Truncation.

Concatenation of Hamsi-512 is performed as follows:

$$y = \frac{m[0..1]||c[0..3]||m[2..5]||c[4..7], m[6..9]||c[8..9]||}{m[10..11]||c[10..13]||m[12..13]||c[14..5]||m[14..15]}$$

The Addition of Constants and Counter step is defined as follows:

$$\begin{aligned} s'[1] &= s[1] \oplus \alpha[1] \oplus c \\ s'[i] &= s[i] \oplus \alpha[i] \\ \text{for } i &= 0, \, 2..31. \end{aligned}$$

Diffusion Layer of Hamsi-512 is defined using the following sequence of operations:

$\boldsymbol{x}$

Figure 3.25: Hamsi : Substitution Layer

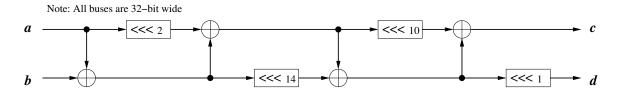

Note: All bus sizes are 32 bits

Figure 3.26: Hamsi: L

```

(s[0], s[9], s[18], s[27]) = L(s[0], s[9], s[18], s[27])

(s[1], s[10], s[19], s[28]) = L(s[1], s[10], s[19], s[28])

(s[2], s[11], s[20], s[29]) = L(s[2], s[11], s[20], s[29])

(s[3], s[12], s[21], s[30]) = L(s[3], s[12], s[21], s[30])

(s[4], s[13], s[22], s[31]) = L(s[4], s[13], s[22], s[31])

(s[5], s[14], s[23], s[24]) = L(s[5], s[14], s[23], s[24])

(s[6], s[15], s[16], s[25]) = L(s[6], s[15], s[16], s[25])

(s[7], s[8], s[17], s[26]) = L(s[7], s[8], s[17], s[26])

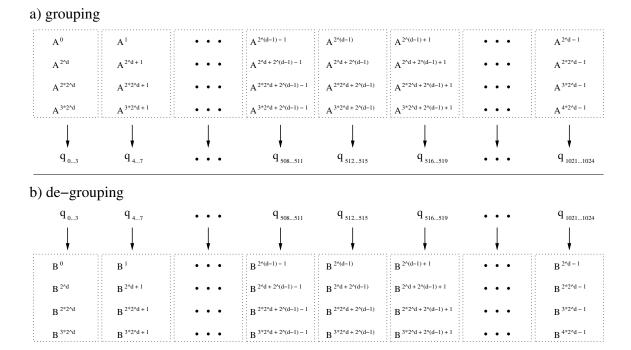

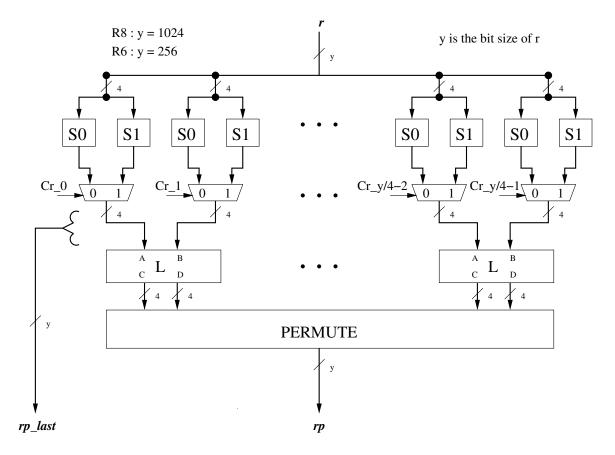

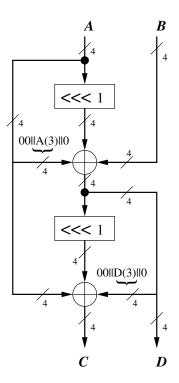

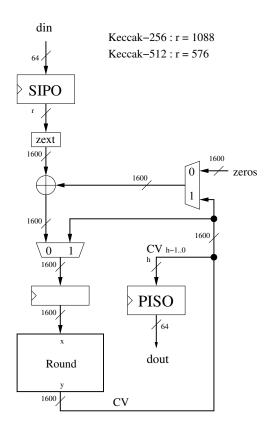

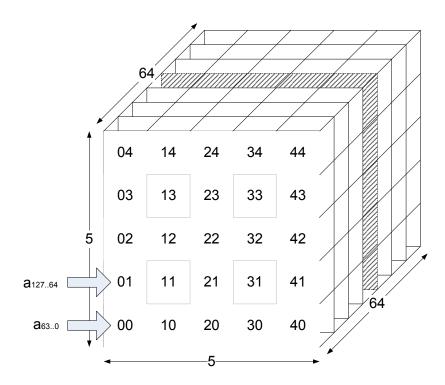

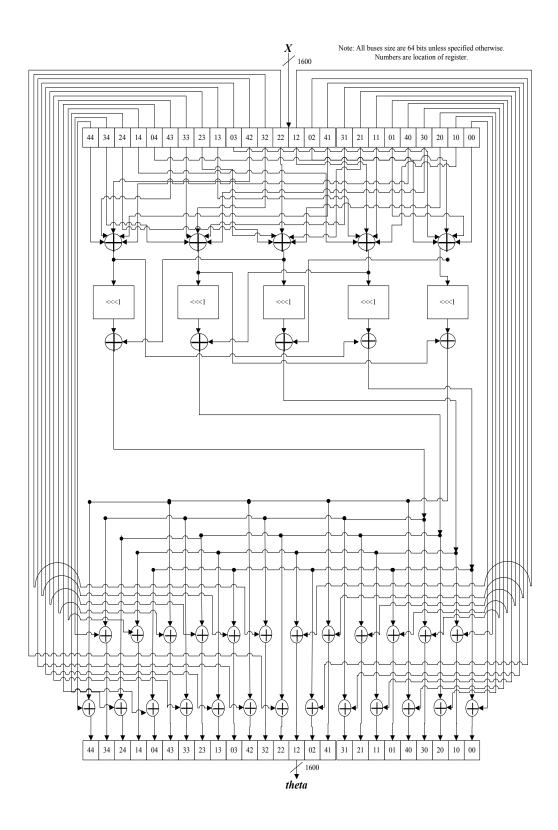

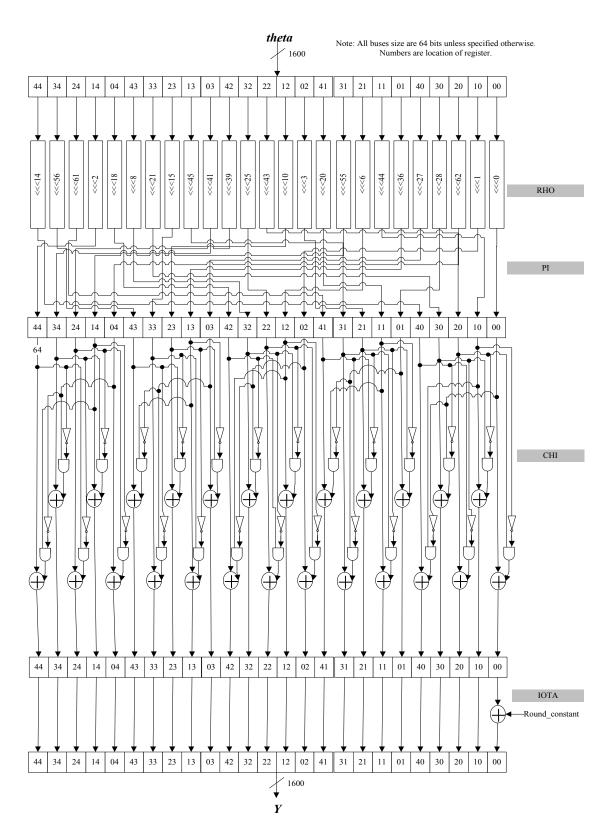

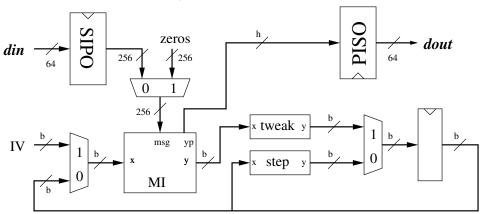

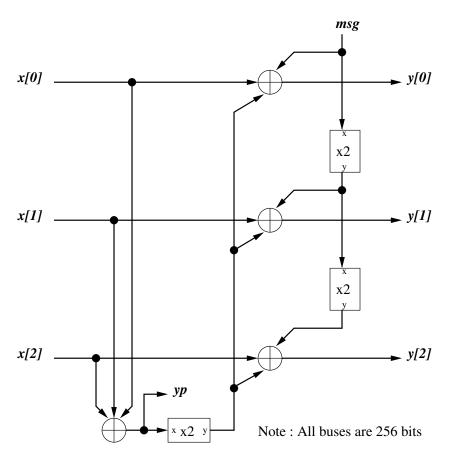

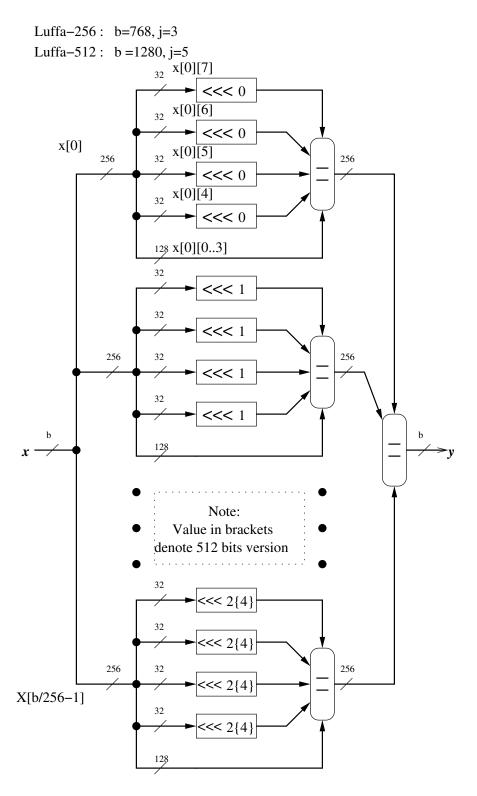

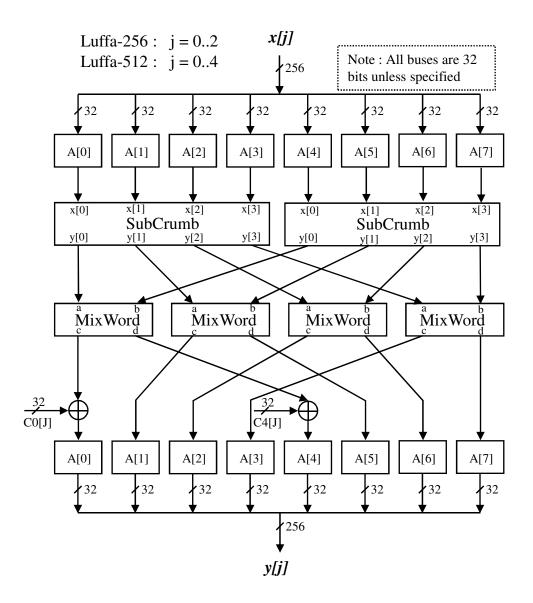

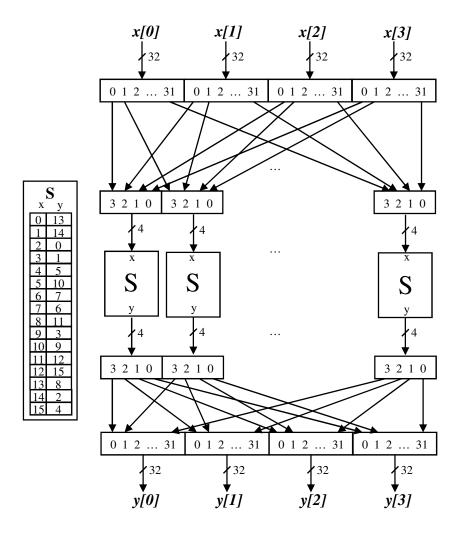

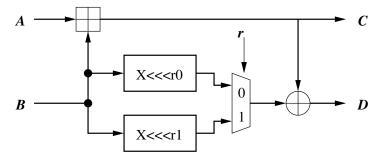

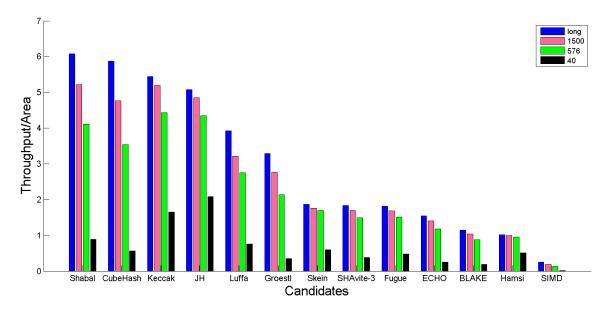

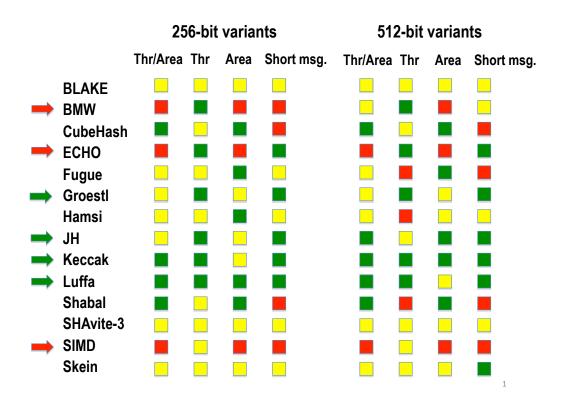

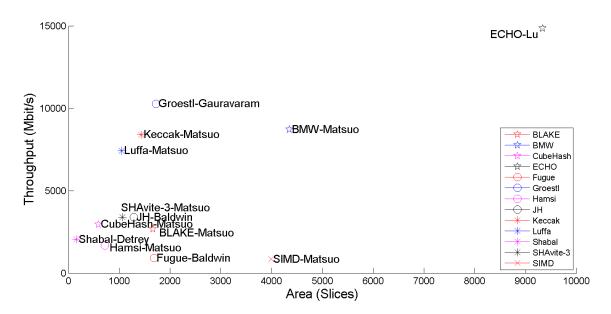

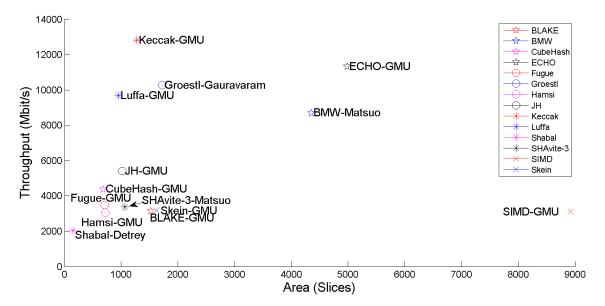

(s[0], s[2], s[5], s[7]) = L(s[0], s[2], s[5], s[7])